單芯片解決方案,開啟全新體驗(yàn)——W55MH32高性能以太網(wǎng)單片機(jī)

W55MH32是WIZnet重磅推出的高性能以太網(wǎng)單片機(jī),它為用戶帶來(lái)前所未有的集成化體驗(yàn)。這顆芯片將強(qiáng)大的組件集于一身,具體來(lái)說(shuō),一顆W55MH32內(nèi)置高性能Arm? Cortex-M3核心,其主頻最高可達(dá)216MHz;配備1024KB FLASH與96KB SRAM,滿足存儲(chǔ)與數(shù)據(jù)處理需求;集成TOE引擎,包含WIZnet全硬件TCP/IP協(xié)議棧、內(nèi)置MAC以及PHY,擁有獨(dú)立的32KB以太網(wǎng)收發(fā)緩存,可供8個(gè)獨(dú)立硬件socket使用。如此配置,真正實(shí)現(xiàn)了All-in-One解決方案,為開發(fā)者提供極大便利。

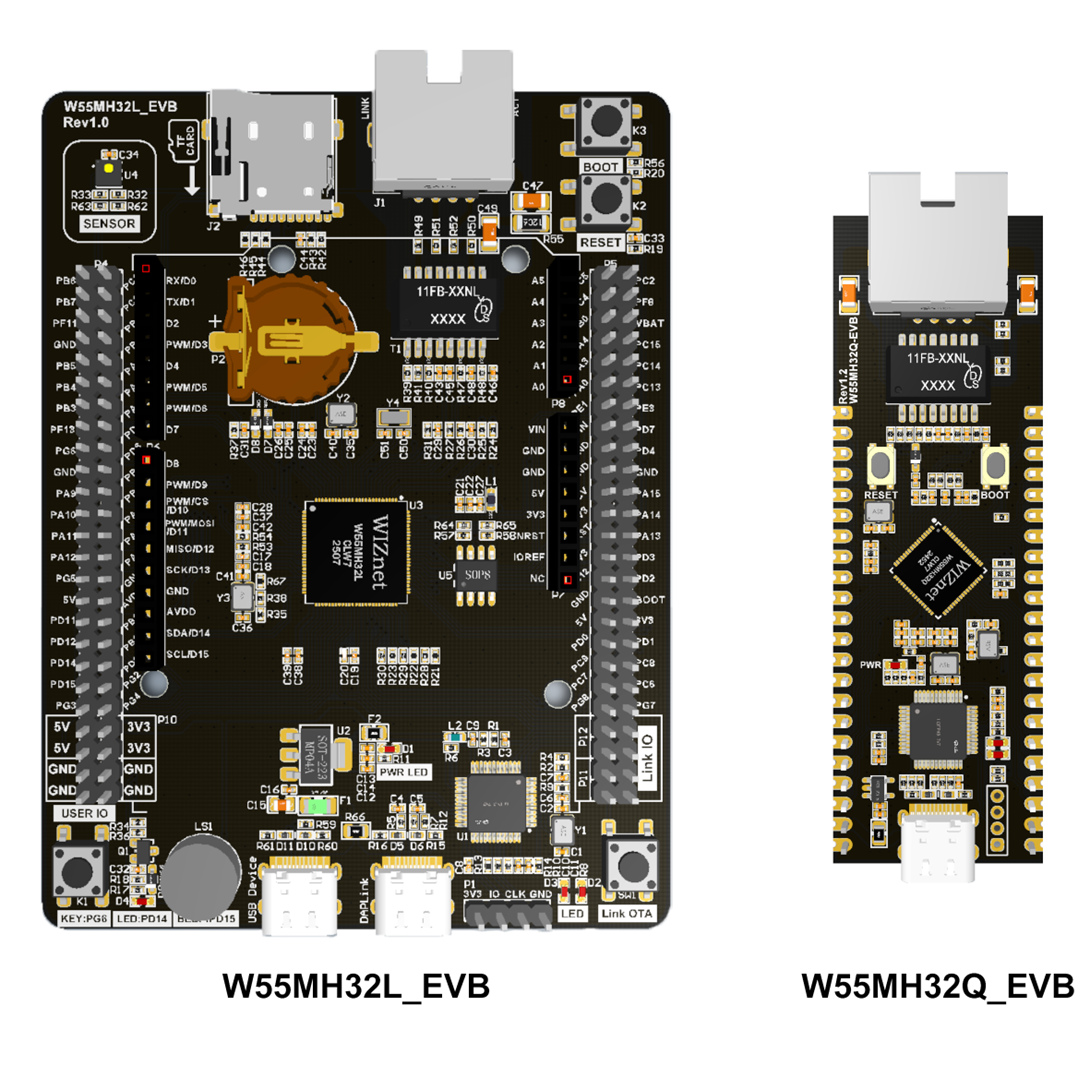

在封裝規(guī)格上,W55MH32提供了兩種選擇:QFN100和QFN68。

W55MH32L采用QFN100封裝版本,尺寸為12x12mm,其資源豐富,專為各種復(fù)雜工控場(chǎng)景設(shè)計(jì)。它擁有66個(gè)GPIO、3個(gè)ADC、12通道DMA、17個(gè)定時(shí)器、2個(gè)I2C、5個(gè)串口、2個(gè)SPI接口(其中1個(gè)帶I2S接口復(fù)用)、1個(gè)CAN、1個(gè)USB2.0以及1個(gè)SDIO接口。如此豐富的外設(shè)資源,能夠輕松應(yīng)對(duì)工業(yè)控制中多樣化的連接需求,無(wú)論是與各類傳感器、執(zhí)行器的通信,還是對(duì)復(fù)雜工業(yè)協(xié)議的支持,都能游刃有余,成為復(fù)雜工控領(lǐng)域的理想選擇。同系列還有QFN68封裝的W55MH32Q版本,該版本體積更小,僅為8x8mm,成本低,適合集成度高的網(wǎng)關(guān)模組等場(chǎng)景,軟件使用方法一致。更多信息和資料請(qǐng)進(jìn)入http://www.w5500.com/網(wǎng)站或者私信獲取。

此外,本W(wǎng)55MH32支持硬件加密算法單元,WIZnet還推出TOE+SSL應(yīng)用,涵蓋TCP SSL、HTTP SSL以及 MQTT SSL等,為網(wǎng)絡(luò)通信安全再添保障。

為助力開發(fā)者快速上手與深入開發(fā),基于W55MH32L這顆芯片,WIZnet精心打造了配套開發(fā)板。開發(fā)板集成WIZ-Link芯片,借助一根USB C口數(shù)據(jù)線,就能輕松實(shí)現(xiàn)調(diào)試、下載以及串口打印日志等功能。開發(fā)板將所有外設(shè)全部引出,拓展功能也大幅提升,便于開發(fā)者全面評(píng)估芯片性能。

若您想獲取芯片和開發(fā)板的更多詳細(xì)信息,包括產(chǎn)品特性、技術(shù)參數(shù)以及價(jià)格等,歡迎訪問官方網(wǎng)頁(yè):http://www.w5500.com/,我們期待與您共同探索W55MH32的無(wú)限可能。

第三十五章 I2S——音頻傳輸接口

I2S(Inter-Integrated Circuit Sound)是W55MH32中用于數(shù)字音頻傳輸?shù)闹匾涌冢瑥V泛應(yīng)用于各種音頻設(shè)備與嵌入式系統(tǒng)。本文將從工作原理、注意事項(xiàng)、應(yīng)用場(chǎng)景以及程序設(shè)計(jì)來(lái)講解I2S接口,和大家一起學(xué)習(xí)和使用這一技術(shù)。

1I2S概述

1.1簡(jiǎn)介

I2S(Inter-Integrated Circuit Sound)是飛利浦公司為數(shù)字音頻設(shè)備之間的音頻數(shù)據(jù)傳輸而制定的一種總線標(biāo)準(zhǔn),專門用于音頻設(shè)備之間的高質(zhì)量數(shù)字音頻傳輸。在W55MH32中,I2S功能與SPI模塊共享相同的硬件資源,通過(guò)將寄存器SPI_I2SCFGR的I2SMOD位置為'1'即可使能I2S功能,將SPI模塊轉(zhuǎn)換為I2S音頻接口。

I2S接口與SPI接口使用大致相同的引腳、標(biāo)志和中斷,但專為音頻數(shù)據(jù)傳輸優(yōu)化。它采用獨(dú)立的導(dǎo)線傳輸時(shí)鐘與數(shù)據(jù)信號(hào),通過(guò)將數(shù)據(jù)和時(shí)鐘信號(hào)分離,避免了因時(shí)差誘發(fā)的失真,為用戶節(jié)省了購(gòu)買抵抗音頻抖動(dòng)的專業(yè)設(shè)備的費(fèi)用。I2S已成為數(shù)字音頻領(lǐng)域的事實(shí)標(biāo)準(zhǔn)接口,廣泛應(yīng)用于各種消費(fèi)電子和專業(yè)音頻設(shè)備中。

1.2功能特點(diǎn)

W55MH32的I2S接口有以下特點(diǎn):

單工通信(僅發(fā)送或接收)

主或者從操作

8位線性可編程預(yù)分頻器,獲得精確的音頻采樣頻率(8KHz到96kHz)

數(shù)據(jù)格式可以是16位,24位或者32位

音頻信道固定數(shù)據(jù)包幀為16位(16位數(shù)據(jù)幀)或32位(16、24或32位數(shù)據(jù)幀)

可編程的時(shí)鐘極性(穩(wěn)定態(tài))

從發(fā)送模式下的下溢標(biāo)志位和主/從接收模式下的溢出標(biāo)志位

16位數(shù)據(jù)寄存器用來(lái)發(fā)送和接收,在通道兩端各有一個(gè)寄存器

支持的I2S協(xié)議:

I2S飛利浦標(biāo)準(zhǔn)

MSB對(duì)齊標(biāo)準(zhǔn)(左對(duì)齊)

LSB對(duì)齊標(biāo)準(zhǔn)(右對(duì)齊)

PCM標(biāo)準(zhǔn)(16位通道幀上帶長(zhǎng)或短幀同步或者16位數(shù)據(jù)幀擴(kuò)展為32位通道幀)

數(shù)據(jù)方向總是MSB在先

發(fā)送和接收都具有DMA能力

主時(shí)鐘可以輸出到外部音頻設(shè)備,比率固定為256xFs(Fs為音頻采樣頻率)

1.3工作原理

I2S接口的核心工作原理基于三個(gè)主要信號(hào)線的協(xié)同工作:

串行時(shí)鐘(SCK/CK):也稱為位時(shí)鐘(BCLK),由主設(shè)備產(chǎn)生,用于同步數(shù)據(jù)傳輸。每個(gè)時(shí)鐘周期對(duì)應(yīng)音頻數(shù)據(jù)的一位。SCK的頻率計(jì)算公式為:SCK頻率 = 2 ×采樣頻率 ×采樣位數(shù)。例如,對(duì)于44.1kHz采樣率、16位精度的立體聲音頻,SCK頻率應(yīng)為44.1kHz×16bits×2(左右聲道)=1.4112MHz。

字選擇(WS):也稱為幀時(shí)鐘(LRCK),用于指示當(dāng)前傳輸?shù)囊纛l數(shù)據(jù)所屬聲道。在I2S飛利浦標(biāo)準(zhǔn)下,WS為'0'表示左聲道數(shù)據(jù),為'1'表示右聲道數(shù)據(jù)。WS信號(hào)在發(fā)送第一位數(shù)據(jù)(MSB)前1個(gè)時(shí)鐘周期即變?yōu)橛行А?/p>

串行數(shù)據(jù)(SD):承載實(shí)際的音頻數(shù)據(jù),采用二進(jìn)制補(bǔ)碼表示。數(shù)據(jù)總是從最高位(MSB)開始傳輸,與SPI接口的MSB優(yōu)先模式類似。

在某些需要更高精度時(shí)鐘同步的系統(tǒng)中,還可以使用第四個(gè)信號(hào)線:

主時(shí)鐘(MCK):為外部音頻編解碼器提供系統(tǒng)時(shí)鐘參考,通常設(shè)置為采樣頻率的256倍(256xFs)。當(dāng)寄存器SPI_I2SPR的MCKOE位為'1'時(shí),W55MH32可輸出此額外時(shí)鐘信號(hào)。

I2S的數(shù)據(jù)傳輸遵循嚴(yán)格的時(shí)序關(guān)系。在I2S飛利浦標(biāo)準(zhǔn)下,發(fā)送方在時(shí)鐘信號(hào)(CK)的下降沿改變數(shù)據(jù),接收方在上升沿讀取數(shù)據(jù)。WS信號(hào)也在時(shí)鐘信號(hào)的下降沿變化。這種同步機(jī)制確保了數(shù)據(jù)傳輸?shù)目煽啃裕词乖诟咚俾氏乱材鼙3州^低的誤碼率。

對(duì)于不同數(shù)據(jù)格式的處理,I2S硬件提供了自動(dòng)的數(shù)據(jù)對(duì)齊和填充功能。例如,當(dāng)16位數(shù)據(jù)擴(kuò)展到32位幀時(shí),高16位(MSB)為有效數(shù)據(jù),低16位被硬件強(qiáng)制為0x0000,無(wú)需軟件干預(yù)。24位數(shù)據(jù)擴(kuò)展到32位幀時(shí),高24位為有效數(shù)據(jù),低8位由硬件置0。這種自動(dòng)處理大大簡(jiǎn)化了軟件開發(fā),特別是在使用DMA傳輸時(shí)。

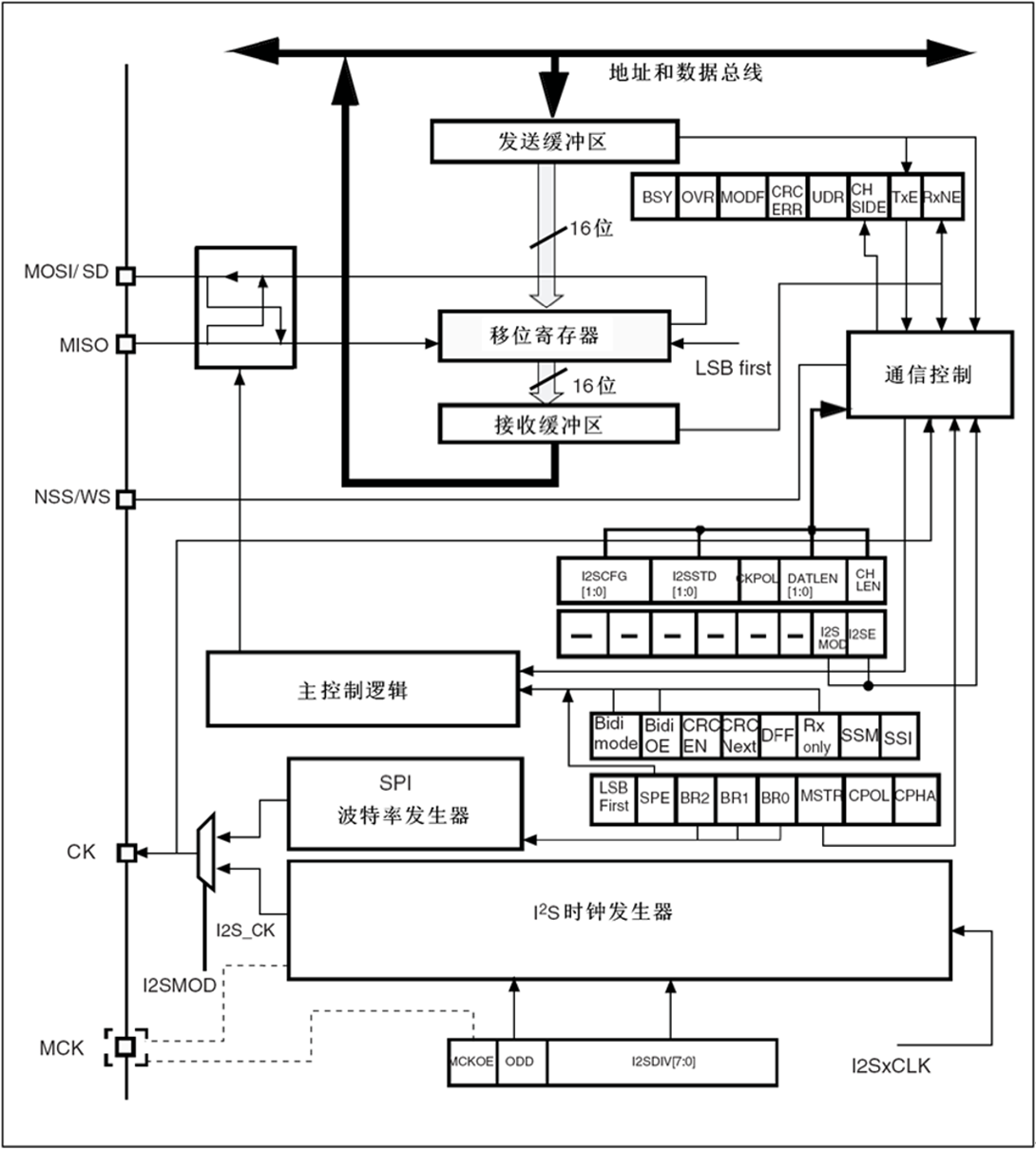

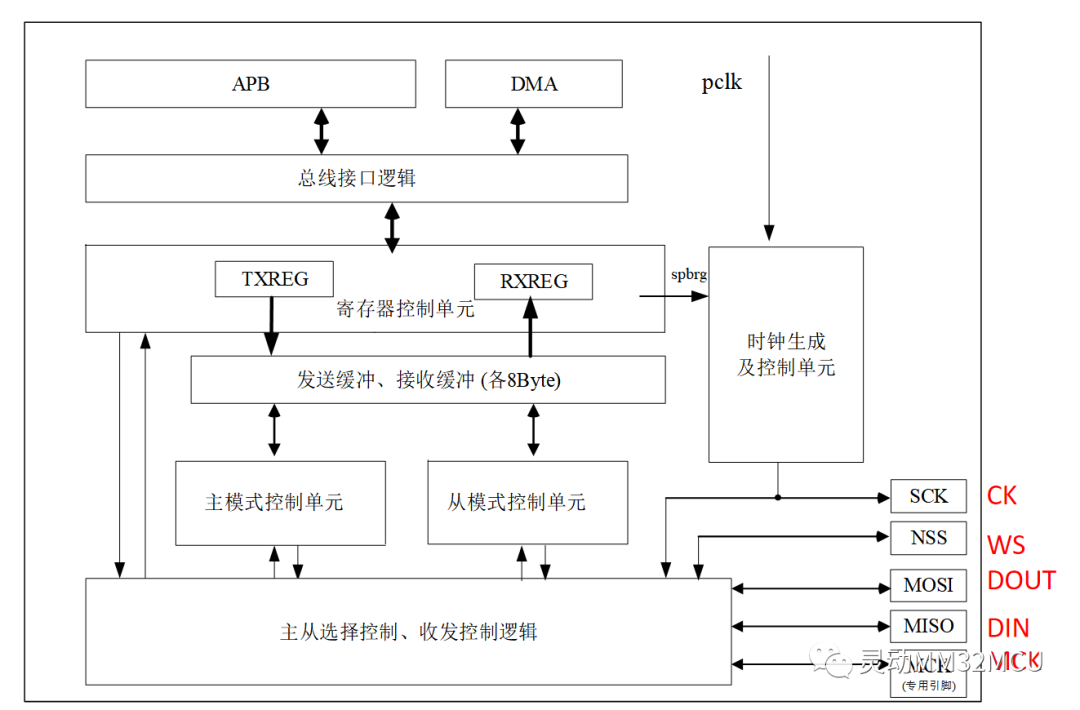

I2S的功能框圖如下:

1.4利用DMA通信的I2S

1.4.1I2S配合DMA通信工作原理

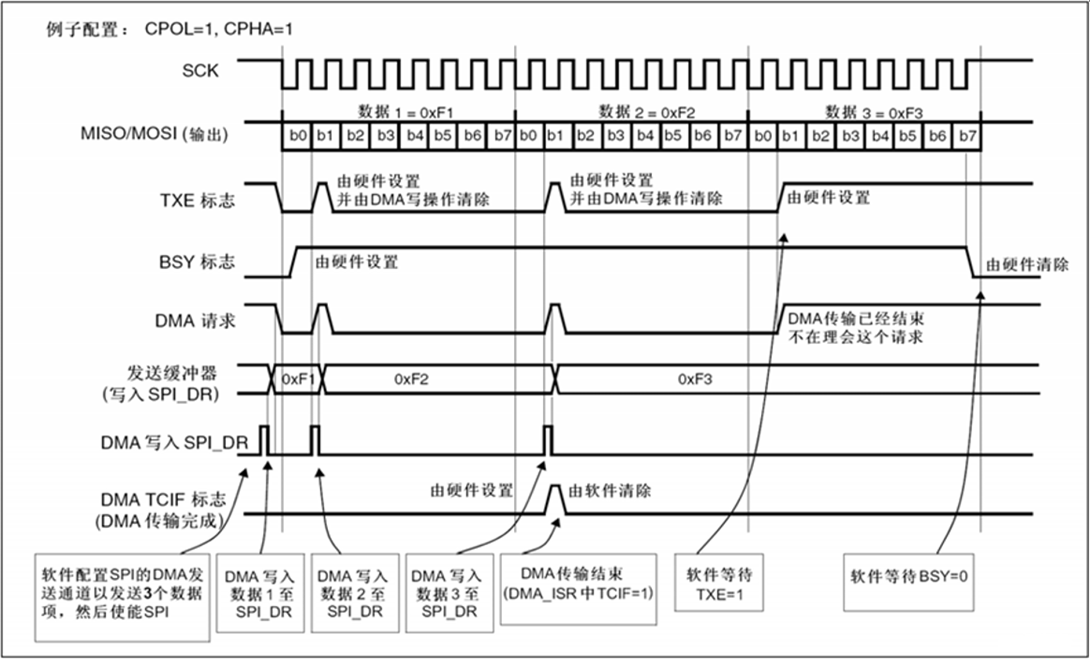

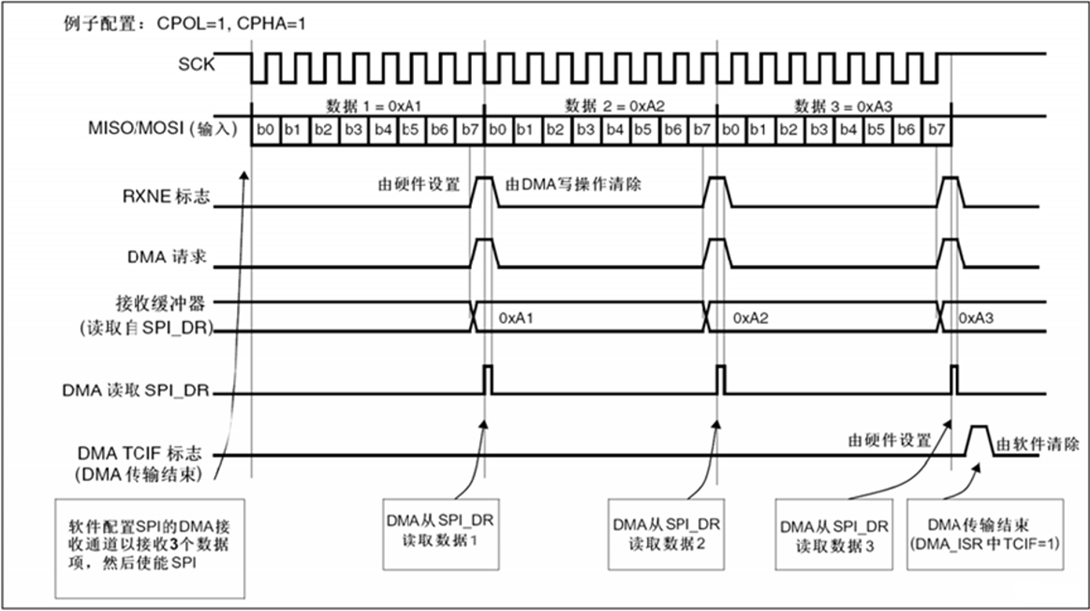

I2S接口與DMA控制器協(xié)同工作時(shí),形成高效的數(shù)據(jù)傳輸通道。通過(guò)將寄存器SPI_CR2的TXDMAEN/RXDMAEN位置1,可使能DMA傳輸請(qǐng)求。I2S模式下DMA的工作方式與SPI模式基本相同,只是沒有CRC功能。當(dāng)I2S接口需要發(fā)送或接收數(shù)據(jù)時(shí),會(huì)自動(dòng)觸發(fā)DMA請(qǐng)求:

發(fā)送過(guò)程:TXE標(biāo)志置1時(shí)觸發(fā)DMA請(qǐng)求,DMA控制器將數(shù)據(jù)從內(nèi)存搬運(yùn)至SPI_DR寄存器。

接收過(guò)程:RXNE標(biāo)志置1時(shí)觸發(fā)DMA請(qǐng)求,DMA控制器將數(shù)據(jù)從SPI_DR寄存器搬運(yùn)至內(nèi)。

使用DMA發(fā)送和接收的時(shí)序圖如下:

1.4.2配置要點(diǎn)

數(shù)據(jù)格式處理

I2S支持多種數(shù)據(jù)格式,DMA需要相應(yīng)配置:

| 數(shù)據(jù)格式 | DMA傳輸次數(shù) | 備注 |

| 16位→16位幀 | 1次 | 直接傳輸 |

| 16位→32位幀 | 1次 | 硬件自動(dòng)補(bǔ)0 |

| 24位→32位幀 | 2次 | 硬件補(bǔ)低8位0 |

| 32位→32位幀 | 2次 | 完整32位處理 |

聲道管理

左聲道數(shù)據(jù)總是先傳輸

通過(guò)CHSIDE標(biāo)志識(shí)別當(dāng)前聲道

從模式需提前準(zhǔn)備好第一個(gè)數(shù)據(jù)

發(fā)送流程

配置DMA:內(nèi)存→SPI_DR,設(shè)置數(shù)據(jù)寬度

啟動(dòng)傳輸:TXE=1時(shí)自動(dòng)觸發(fā)

聲道切換:根據(jù)CHSIDE處理左右聲道

完成處理:等待TXE=1及BSY=0后關(guān)閉

接收流程

配置DMA:SPI_DR→內(nèi)存,設(shè)置數(shù)據(jù)寬度

啟動(dòng)傳輸:RXNE=1時(shí)自動(dòng)觸發(fā)

數(shù)據(jù)解析:根據(jù)標(biāo)準(zhǔn)處理數(shù)據(jù)對(duì)齊

關(guān)閉時(shí)序:按數(shù)據(jù)格式選擇正確時(shí)序

2應(yīng)用場(chǎng)景

W55MH32的I2S接口憑借其高質(zhì)量數(shù)字音頻傳輸能力,在眾多領(lǐng)域得到廣泛應(yīng)用:

2.1消費(fèi)類音頻設(shè)備

便攜式音樂播放器:連接音頻DAC實(shí)現(xiàn)高質(zhì)量音樂播放,支持從MP3解碼器到功率放大器的數(shù)字音頻傳輸。

智能音箱:用于主控芯片與數(shù)字音頻處理器之間的連接,實(shí)現(xiàn)語(yǔ)音助手和音樂播放功能。

數(shù)字電視和機(jī)頂盒:傳輸數(shù)字音頻信號(hào)到音頻處理芯片或直接驅(qū)動(dòng)數(shù)字功放。

2.2專業(yè)音頻設(shè)備

錄音設(shè)備:連接高性能ADC實(shí)現(xiàn)多通道音頻采集,支持24位高分辨率錄音。

音頻混音器:在數(shù)字域混合多個(gè)音頻源,保持信號(hào)完整性。

效果處理器:傳輸音頻數(shù)據(jù)到DSP芯片進(jìn)行實(shí)時(shí)效果處理。

2.3通信設(shè)備

VoIP電話:實(shí)現(xiàn)雙向語(yǔ)音通信,同時(shí)支持回聲消除等高級(jí)功能。

會(huì)議系統(tǒng):連接數(shù)字麥克風(fēng)陣列和音頻處理單元。

無(wú)線耳機(jī):在藍(lán)牙模塊與編解碼器之間傳輸音頻數(shù)據(jù)。

2.4汽車電子

車載娛樂系統(tǒng):連接多個(gè)音頻源和功放,支持環(huán)繞聲處理。

主動(dòng)降噪系統(tǒng):實(shí)時(shí)采集車內(nèi)噪聲并生成反相聲波。

語(yǔ)音識(shí)別系統(tǒng):傳輸高清晰度語(yǔ)音數(shù)據(jù)到語(yǔ)音處理單元。

2.5嵌入式系統(tǒng)

工業(yè)控制人機(jī)界面:實(shí)現(xiàn)語(yǔ)音提示和報(bào)警功能。

醫(yī)療監(jiān)護(hù)設(shè)備:傳輸心音、呼吸音等生物音頻信號(hào)。

智能家居:用于門鈴、對(duì)講系統(tǒng)等需要音頻功能的設(shè)備。

3注意事項(xiàng)

時(shí)鐘同步:從模式需確保在外部時(shí)鐘有效前完成初始化。

數(shù)據(jù)對(duì)齊:注意不同標(biāo)準(zhǔn)(Philips/MSB/LSB)的數(shù)據(jù)對(duì)齊差異。

PCB布局:時(shí)鐘信號(hào)線應(yīng)盡量短并考慮端接匹配。

關(guān)閉順序:嚴(yán)格按照規(guī)范流程關(guān)閉接口,避免數(shù)據(jù)損壞。

4程序設(shè)計(jì)

4.1IIS_CS4344例程

IIS_CS4344例程主要實(shí)現(xiàn)了基于W55MH32芯片的I2S音頻傳輸功能。以下是實(shí)現(xiàn)過(guò)程和結(jié)果驗(yàn)證:

4.1.1I2S初始化

I2S的初始化函數(shù)為IIS_Configuration()函數(shù):

void IIS_Configuration(void)

{

I2S_InitTypeDef I2S_InitStructure;

GPIO_InitTypeDef GPIO_InitStructure;

RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO, ENABLE);

GPIO_PinRemapConfig(GPIO_Remap_SWJ_JTAGDisable, ENABLE);

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA| RCC_APB2Periph_GPIOB| RCC_APB2Periph_GPIOC, ENABLE);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_SPI3, ENABLE);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_15;

GPIO_InitStructure.GPIO_Speed= GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOA,&GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_3| GPIO_Pin_5;

GPIO_InitStructure.GPIO_Speed= GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOB,&GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin= GPIO_Pin_7;

GPIO_Init(GPIOC,&GPIO_InitStructure);

SPI_I2S_DeInit(SPI3);

I2S_InitStructure.I2S_Mode = I2S_Mode_MasterTx;

I2S_InitStructure.I2S_Standard = I2S_Standard_Phillips;

I2S_InitStructure.I2S_DataFormat= I2S_DataFormat_16b;

I2S_InitStructure.I2S_AudioFreq = I2S_AudioFreq_8k;

I2S_InitStructure.I2S_CPOL = I2S_CPOL_Low;

I2S_InitStructure.I2S_MCLKOutput= I2S_MCLKOutput_Enable;

I2S_Init(SPI3,&I2S_InitStructure);

SPI_I2S_DMACmd(SPI3, SPI_I2S_DMAReq_Tx, ENABLE);

I2S_Cmd(SPI3, ENABLE);

}

該函數(shù)首先使能了相關(guān)時(shí)鐘并釋放GPIOA15資源(PA15默認(rèn)為調(diào)試接口,必須先釋放其默認(rèn)的調(diào)試功能,否則,調(diào)試接口會(huì)持續(xù)占用該引腳,導(dǎo)致I2S無(wú)法正常工作。),然后配置GPIOA15、GPIOB3、GPIOB5和GPIOC7為復(fù)用推挽輸出模式以連接I2S的SCK、SD、WS和MCLK信號(hào),接著將SPI3初始化為I2S模式并設(shè)置為主機(jī)發(fā)送模式,采用飛利浦標(biāo)準(zhǔn)、16位數(shù)據(jù)格式、8kHz采樣率,啟用MCLK輸出和低時(shí)鐘極性,最后使能DMA傳輸以提高數(shù)據(jù)效率并激活I(lǐng)2S外設(shè)。

4.1.2DMA初始化

DMA_Configuration()為DMA初始化函數(shù):

void DMA_Configuration(void)

{

DMA_InitTypeDef DMA_InitStructure;

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_DMA2, ENABLE);

DMA_DeInit(DMA2_Channel2);

DMA_InitStructure.DMA_PeripheralBaseAddr=(uint32_t)&SPI3->DR;

DMA_InitStructure.DMA_MemoryBaseAddr =(uint32_t)I2S3_Buffer_Tx;

DMA_InitStructure.DMA_DIR = DMA_DIR_PeripheralDST;

DMA_InitStructure.DMA_BufferSize =BufferSize;

DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable;

DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable;

DMA_InitStructure.DMA_PeripheralDataSize= DMA_PeripheralDataSize_HalfWord;

DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_HalfWord;

DMA_InitStructure.DMA_Mode = DMA_Mode_Circular;

DMA_InitStructure.DMA_Priority = DMA_Priority_VeryHigh;

DMA_InitStructure.DMA_M2M = DMA_M2M_Disable;

DMA_Init(DMA2_Channel2,&DMA_InitStructure);

DMA_ITConfig(DMA2_Channel2, DMA_IT_TC, ENABLE);

/* Enable SPI1 DMA TX request */

DMA_Cmd(DMA2_Channel2, DISABLE);

}

該函數(shù)首先使能了DMA2時(shí)鐘,然后將DMA2通道2初始化為從內(nèi)存到外設(shè)的傳輸模式,設(shè)置外設(shè)基址為SPI3的數(shù)據(jù)寄存器(用于I2S通信),內(nèi)存基址為音頻數(shù)據(jù)緩沖區(qū)I2S3_Buffer_Tx,配置傳輸方向?yàn)閮?nèi)存到外設(shè)、緩沖區(qū)大小為BufferSize,禁用外設(shè)地址自增、啟用內(nèi)存地址自增,設(shè)置數(shù)據(jù)寬度為半字(16位,與I2S數(shù)據(jù)格式匹配),采用循環(huán)模式確保連續(xù)傳輸,設(shè)置優(yōu)先級(jí)為非常高,禁用內(nèi)存到內(nèi)存模式,最后使能傳輸完成中斷并暫時(shí)禁用DMA通道。

4.1.3中斷配置函數(shù)

NVIC_Configuration()為NVIC(嵌套向量中斷控制器)的配置函數(shù):

void NVIC_Configuration(void)

{

NVIC_InitTypeDef NVIC_InitStructure;

NVIC_InitStructure.NVIC_IRQChannel = DMA2_Channel2_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority =0;

NVIC_InitStructure.NVIC_IRQChannelSubPriority =0;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

}

該函數(shù)首先定義NVIC了初始化結(jié)構(gòu)體,然后將中斷通道設(shè)置為DMA2通道2(對(duì)應(yīng)I2S3的TX DMA傳輸),配置搶占優(yōu)先級(jí)和子優(yōu)先級(jí)均為0(最高優(yōu)先級(jí)),使能該中斷通道,最后調(diào)用初始化函數(shù)完成配置,整體實(shí)現(xiàn)了對(duì)DMA2通道2傳輸完成事件的高優(yōu)先級(jí)中斷響應(yīng)設(shè)置,確保音頻數(shù)據(jù)傳輸中斷能被及時(shí)處理。

4.1.4中斷服務(wù)函數(shù)

DMA2_Channel2_IRQHandler()為DMA2通道2的中斷服務(wù)函數(shù):

void DMA2_Channel2_IRQHandler(void)

{

if(DMA_GetITStatus(DMA2_IT_TC2)== SET)

{

DMA_ClearITPendingBit(DMA2_IT_TC2);

DMA_ClearFlag(DMA2_FLAG_TC2);

DMA_Cmd(DMA2_Channel2, DISABLE);

Flag=1;

}

}

程序首先檢查是否為DMA傳輸完成中斷(TC2),若是則清除中斷掛起位和完成標(biāo)志位,禁用DMA2通道2以暫停傳輸,最后將標(biāo)志位Flag置1以通知主程序數(shù)據(jù)已傳輸完畢,整體實(shí)現(xiàn)了對(duì)I2S音頻數(shù)據(jù)DMA傳輸完成的響應(yīng)處理,確保在數(shù)據(jù)發(fā)送完成后能進(jìn)行必要的狀態(tài)更新和后續(xù)操作。

4.1.5數(shù)據(jù)處理函數(shù)

DATA_Processing()是數(shù)據(jù)處理函數(shù),通過(guò)以下步驟實(shí)現(xiàn)將8位數(shù)據(jù)轉(zhuǎn)換為16位格式:

void DATA_Processing(void)

{

uint32_t i;

for(i=0; i< DATA_LEN?/?2; i++)

{

I2S3_Buffer_Tx[i]?= DATA[2?* i]?

程序首先定義循環(huán)計(jì)數(shù)器,然后對(duì)長(zhǎng)度為DATA_LEN的8位數(shù)據(jù)源數(shù)組DATA進(jìn)行遍歷,每次取連續(xù)的兩個(gè)8位數(shù)據(jù),將前一個(gè)左移8位后與后一個(gè)按位或運(yùn)算,組合成一個(gè)16位數(shù)據(jù)存入目標(biāo)數(shù)組I2S3_Buffer_Tx中,整體實(shí)現(xiàn)了將8位原始數(shù)據(jù)轉(zhuǎn)換為適合I2S傳輸?shù)?6位數(shù)據(jù)格式,確保音頻數(shù)據(jù)能夠正確地通過(guò)I2S接口發(fā)送。

4.1.6主程序

主程序main()通過(guò)以下步驟實(shí)現(xiàn)I2S音頻數(shù)據(jù)的持續(xù)傳輸:

int main(void)

{

RCC_ClocksTypeDef clocks;

delay_init();

UART_Configuration(115200);

RCC_GetClocksFreq(&clocks);

printf("n");

printf("SYSCLK: %3.1fMhz, HCLK: %3.1fMhz, PCLK1: %3.1fMhz, PCLK2: %3.1fMhz, ADCCLK: %3.1fMhzn",

(float)clocks.SYSCLK_Frequency /1000000,(float)clocks.HCLK_Frequency/1000000,

(float)clocks.PCLK1_Frequency /1000000,(float)clocks.PCLK2_Frequency/1000000,(float)clocks.ADCCLK_Frequency/1000000);

printf("IIS CS4344 Test.n");

IIS_Configuration();

DMA_Configuration();

NVIC_Configuration();

DATA_Processing();

DMA_Cmd(DMA2_Channel2, ENABLE);

while(1)

{

if(Flag==1)

{

printf("IIS DMA Data Send Successn");

Flag=0;

DMA_Configuration();

DMA_Cmd(DMA2_Channel2, ENABLE);

}

}

}

程序首先初始化系統(tǒng)時(shí)鐘和延時(shí)函數(shù),配置115200波特率的UART用于調(diào)試信息輸出,獲取并打印系統(tǒng)各時(shí)鐘頻率;接著依次配置I2S接口、DMA通道、NVIC中斷控制器,并將8位原始數(shù)據(jù)處理為16位格式以適配I2S傳輸;然后啟用DMA通道開始數(shù)據(jù)傳輸;最后在主循環(huán)中檢測(cè)傳輸完成標(biāo)志Flag,若置1則打印成功信息、重置標(biāo)志,重新配置并啟用DMA通道以實(shí)現(xiàn)循環(huán)傳輸,整體實(shí)現(xiàn)了通過(guò)I2S接口持續(xù)發(fā)送音頻數(shù)據(jù)的功能。

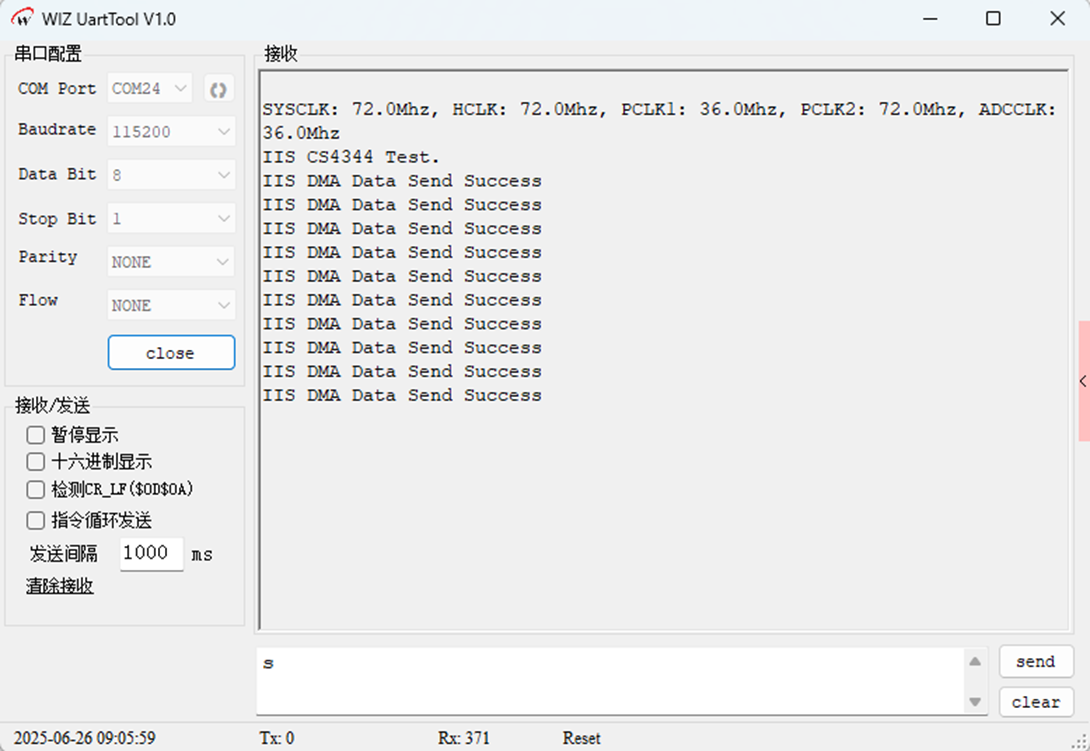

4.1.7下載驗(yàn)證

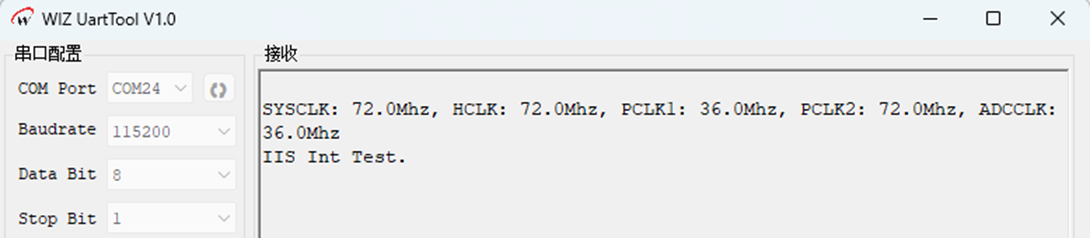

程序下載運(yùn)行后,首先打印了系統(tǒng)各時(shí)鐘的頻率和示例名稱,然后每發(fā)送成功一次I2S數(shù)據(jù)就會(huì)打印數(shù)據(jù)發(fā)送成功的信息:

此時(shí)我們接上DAC音頻轉(zhuǎn)換器、戴上耳機(jī)就能持續(xù)聽到“微信到賬100萬(wàn)元”的音頻內(nèi)容。

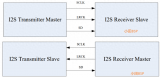

4.2IIS_Dma例程

IIS_Dma例程通過(guò)I2S接口和DMA傳輸機(jī)制,發(fā)送預(yù)設(shè)的音頻數(shù)據(jù)。該例程的I2S初始化、DMA初始化、中斷配置函數(shù)與IIS_CS4344例程保持一致,這里不再贅述。其他程序設(shè)計(jì)如下:

4.2.1發(fā)送數(shù)據(jù)

I2S3_Buffer_Tx為需要發(fā)送的測(cè)試數(shù)據(jù):

uint16_t I2S3_Buffer_Tx[BufferSize]={0x0102,0x0304,0x0506,0x0708,0x090A,0x0B0C,

0x0D0E,0x0F10,0x1112,0x1314,0x1516,0x1718,

0x191A,0x1B1C,0x1D1E,0x1F20,0x2122,0x2324,

0x2526,0x2728,0x292A,0x2B2C,0x2D2E,0x2F30,

0x3132,0x3334,0x3536,0x3738,0x393A,0x3B3C,

0x3D3E,0x3F40};

4.2.2中斷服務(wù)函數(shù)

DMA2_Channel2_IRQHandler是W55MH32中DMA2通道2的中斷處理函數(shù):

void DMA2_Channel2_IRQHandler(void)

{

if(DMA_GetITStatus(DMA2_IT_TC2)== SET)

{

DMA_ClearITPendingBit(DMA2_IT_TC2);

DMA_ClearFlag(DMA2_FLAG_TC2);

DMA_Cmd(DMA2_Channel2, DISABLE);

Flag=1;

}

}

當(dāng)DMA完成預(yù)設(shè)的32個(gè)16位數(shù)據(jù)傳輸后觸發(fā)。函數(shù)首先檢查傳輸完成中斷狀態(tài),若中斷已觸發(fā)則清除中斷掛起位和傳輸完成標(biāo)志,避免重復(fù)響應(yīng);接著禁用DMA2通道2,停止數(shù)據(jù)傳輸;最后將全局標(biāo)志位Flag置1,通知主程序DMA傳輸已完成,主循環(huán)檢測(cè)到該標(biāo)志后會(huì)輸出成功信息并重置標(biāo)志。此函數(shù)實(shí)現(xiàn)了DMA傳輸?shù)闹袛囗憫?yīng)與狀態(tài)反饋,是I2S音頻數(shù)據(jù)傳輸流程中的關(guān)鍵環(huán)節(jié)。

4.2.3主程序

主程序main()通過(guò)以下步驟實(shí)現(xiàn)I2S音頻數(shù)據(jù)的傳輸:

int main(void)

{

RCC_ClocksTypeDef clocks;

delay_init();

UART_Configuration(115200);

RCC_GetClocksFreq(&clocks);

printf("n");

printf("SYSCLK: %3.1fMhz, HCLK: %3.1fMhz, PCLK1: %3.1fMhz, PCLK2: %3.1fMhz, ADCCLK: %3.1fMhzn",

(float)clocks.SYSCLK_Frequency /1000000,(float)clocks.HCLK_Frequency/1000000,

(float)clocks.PCLK1_Frequency /1000000,(float)clocks.PCLK2_Frequency/1000000,(float)clocks.ADCCLK_Frequency/1000000);

printf("IIS DMA Test.n");

IIS_Configuration();

DMA_Configuration();

NVIC_Configuration();

DMA_Cmd(DMA2_Channel2, ENABLE);

while(1)

{

if(Flag==1)

{

printf("IIS DMA Data Send Successn");

Flag=0;

}

}

}

程序首先初始化系統(tǒng)時(shí)鐘、UART調(diào)試接口并打印時(shí)鐘信息,接著配置I2S接口(復(fù)用SPI3)、DMA2通道2(循環(huán)模式)和NVIC中斷控制器,隨后啟用DMA開始將預(yù)設(shè)的32個(gè)16位音頻數(shù)據(jù)循環(huán)傳輸?shù)絀2S接口,主循環(huán)持續(xù)檢測(cè)DMA傳輸完成標(biāo)志位Flag,當(dāng)Flag被中斷處理函數(shù)置1時(shí),打印傳輸成功信息并重置標(biāo)志,不過(guò)因中斷處理函數(shù)中禁用了DMA通道,實(shí)際數(shù)據(jù)僅能傳輸一次,此代碼常用于音頻設(shè)備初始化測(cè)試。

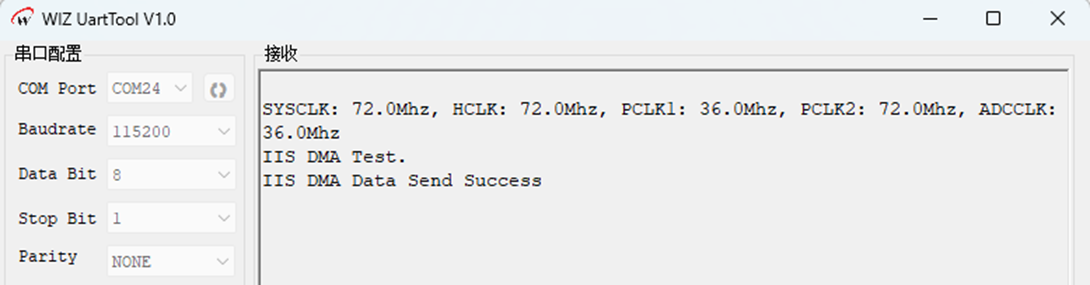

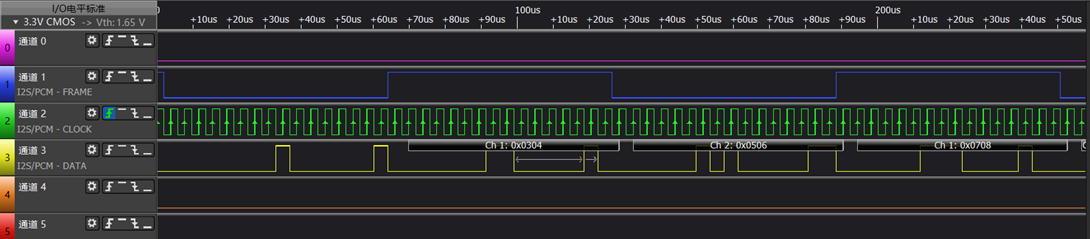

4.2.4下載驗(yàn)證

程序下載運(yùn)行后,首先打印了系統(tǒng)各時(shí)鐘的頻率和示例名稱,然后I2S數(shù)據(jù)發(fā)送成功后打印數(shù)據(jù)發(fā)送成功的信息:

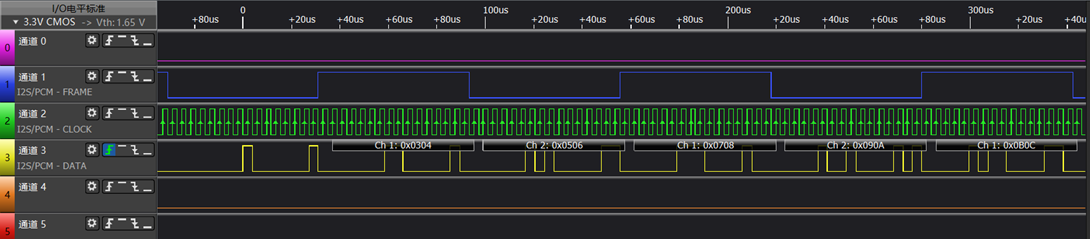

通過(guò)邏輯分析儀就可以解析出發(fā)送的數(shù)據(jù):

首幀和尾幀的數(shù)據(jù)實(shí)際已經(jīng)可以看到有數(shù)據(jù)脈沖信號(hào),未解析屬于硬件初始化特性(FIFO填充)或解析器同步延遲原因,不影響實(shí)際音頻功能。

4.3IIS_Int例程

IIS_Int例程通過(guò)I2S接口和中斷控制器實(shí)現(xiàn)音頻數(shù)據(jù)的中斷驅(qū)動(dòng)傳輸。其他程序設(shè)計(jì)如下:

4.3.1 I2S初始化

IIS_Configuration()函數(shù)用于初始化W55MH32的I2S接口(復(fù)用SPI3外設(shè))及中斷配置,其內(nèi)容如下:

void IIS_Configuration(void)

{

I2S_InitTypeDef I2S_InitStructure;

GPIO_InitTypeDef GPIO_InitStructure;

NVIC_InitTypeDef NVIC_InitStructure;

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA | RCC_APB2Periph_GPIOB| RCC_APB2Periph_GPIOC, ENABLE);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_SPI3, ENABLE);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_15;

GPIO_InitStructure.GPIO_Speed= GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOA,&GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_3| GPIO_Pin_5;

GPIO_InitStructure.GPIO_Speed= GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOB,&GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin= GPIO_Pin_7;

GPIO_Init(GPIOC,&GPIO_InitStructure);

NVIC_InitStructure.NVIC_IRQChannel = SPI3_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority =0;

NVIC_InitStructure.NVIC_IRQChannelSubPriority =0;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

SPI_I2S_DeInit(SPI3);

I2S_InitStructure.I2S_Mode = I2S_Mode_MasterTx;

I2S_InitStructure.I2S_Standard = I2S_Standard_Phillips;

I2S_InitStructure.I2S_DataFormat= I2S_DataFormat_16b;

I2S_InitStructure.I2S_AudioFreq = I2S_AudioFreq_8k;

I2S_InitStructure.I2S_CPOL = I2S_CPOL_Low;

I2S_InitStructure.I2S_MCLKOutput= I2S_MCLKOutput_Enable;

I2S_Init(SPI3,&I2S_InitStructure);

SPI_I2S_ITConfig(SPI3, SPI_I2S_IT_TXE, ENABLE);

I2S_Cmd(SPI3, ENABLE);

}

函數(shù)首先使能GPIOA/B/C和SPI3的時(shí)鐘,配置相關(guān)引腳為復(fù)用推挽輸出(包括數(shù)據(jù)輸出、字選擇、串行時(shí)鐘和主時(shí)鐘引腳);接著配置NVIC中斷控制器,設(shè)置SPI3中斷的優(yōu)先級(jí)并使能中斷;然后重置SPI3并設(shè)置I2S參數(shù),包括主發(fā)送模式、飛利浦標(biāo)準(zhǔn)、16位數(shù)據(jù)格式、8kHz采樣率、低時(shí)鐘極性和主時(shí)鐘輸出;最后啟用發(fā)送緩沖區(qū)空中斷(TXE)并使能I2S外設(shè)。該配置適用于簡(jiǎn)單音頻發(fā)送場(chǎng)景,通過(guò)中斷驅(qū)動(dòng)方式實(shí)現(xiàn)數(shù)據(jù)傳輸。

4.3.2 中斷服務(wù)函數(shù)

SPI3_IRQHandler()是SPI3外設(shè)的中斷處理函數(shù),用于處理I2S發(fā)送緩沖區(qū)空(TXE)事件,函數(shù)內(nèi)容如下:

void SPI3_IRQHandler(void)

{

if(SPI_I2S_GetITStatus(SPI3, SPI_I2S_IT_TXE)== SET)

{

/* Send a data from I2S3 */

SPI_I2S_SendData(SPI3, I2S3_Buffer_Tx[TxIdx++]);

}

if(TxIdx==32)

{

SPI_I2S_ITConfig(SPI3, SPI_I2S_IT_TXE, DISABLE);

}

}

當(dāng)檢測(cè)到TXE標(biāo)志置位時(shí),函數(shù)從預(yù)設(shè)的32元素?cái)?shù)據(jù)緩沖區(qū)I2S3_Buffer_Tx中讀取一個(gè)16位數(shù)據(jù)發(fā)送到I2S接口,并遞增索引TxIdx;當(dāng)TxIdx達(dá)到32時(shí),表示所有數(shù)據(jù)發(fā)送完畢,函數(shù)禁用TXE中斷以停止傳輸。該函數(shù)實(shí)現(xiàn)了基于中斷的單次數(shù)據(jù)塊發(fā)送,適用于小規(guī)模固定數(shù)據(jù)的傳輸場(chǎng)景。

4.3.3 主程序

以下為該例程的主程序,用于測(cè)試I2S接口的中斷驅(qū)動(dòng)數(shù)據(jù)發(fā)送功能:

int main(void)

{

RCC_ClocksTypeDef clocks;

delay_init();

UART_Configuration(115200);

RCC_GetClocksFreq(&clocks);

printf("n");

printf("SYSCLK: %3.1fMhz, HCLK: %3.1fMhz, PCLK1: %3.1fMhz, PCLK2: %3.1fMhz, ADCCLK: %3.1fMhzn",

(float)clocks.SYSCLK_Frequency /1000000,(float)clocks.HCLK_Frequency/1000000,

(float)clocks.PCLK1_Frequency /1000000,(float)clocks.PCLK2_Frequency/1000000,(float)clocks.ADCCLK_Frequency/1000000);

printf("IIS Int Test.n");

IIS_Configuration();

while(1);

}

程序先初始化延時(shí)函數(shù)和UART1串口,獲取并打印系統(tǒng)各時(shí)鐘頻率,然后初始化I2S接口(配置GPIO、中斷及I2S參數(shù)),最后進(jìn)入無(wú)限循環(huán),數(shù)據(jù)發(fā)送由I2S發(fā)送緩沖區(qū)空中斷驅(qū)動(dòng),主程序不參與具體傳輸邏輯。

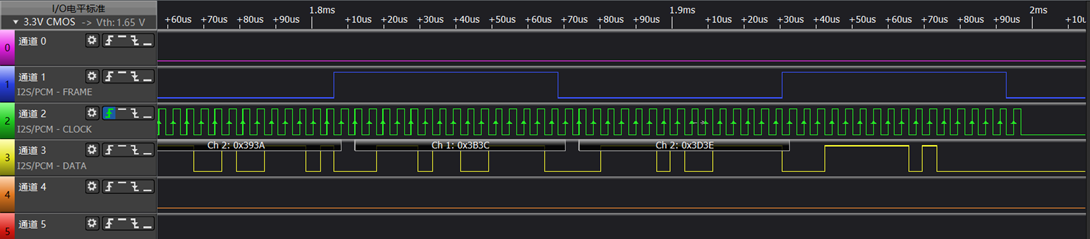

4.3.4 下載驗(yàn)證

程序下載運(yùn)行后,首先打印了系統(tǒng)各時(shí)鐘的頻率和示例名稱,I2S觸發(fā)中斷之后開始發(fā)送數(shù)據(jù),數(shù)據(jù)緩沖區(qū)有數(shù)據(jù)之后便不再觸發(fā):

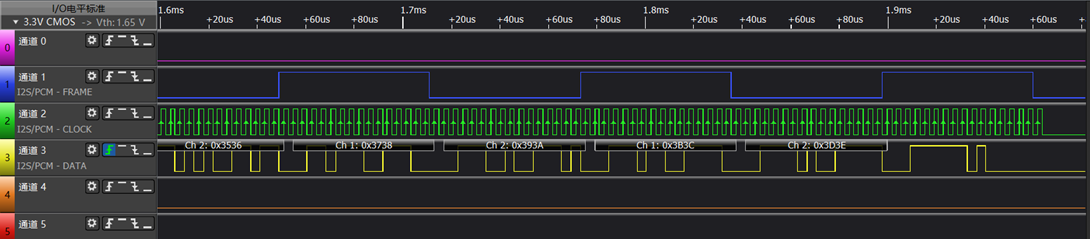

邏輯分析儀解析數(shù)據(jù)如下:

同樣的,首幀和尾幀的數(shù)據(jù)實(shí)際也已經(jīng)可以看到有數(shù)據(jù)脈沖信號(hào),未解析屬于硬件初始化特性(FIFO填充)或解析器同步延遲原因,不影響實(shí)際音頻功能。

5總結(jié)

W55MH32的I2S接口為數(shù)字音頻應(yīng)用提供了強(qiáng)大而靈活的解決方案。通過(guò)與SPI模塊共享硬件資源,它既實(shí)現(xiàn)了專用音頻接口的高性能,又保持了設(shè)計(jì)的經(jīng)濟(jì)性。支持多種音頻標(biāo)準(zhǔn)和數(shù)據(jù)格式使其能夠與絕大多數(shù)音頻編解碼器無(wú)縫協(xié)作,滿足從消費(fèi)電子到專業(yè)音頻設(shè)備的各種需求。

WIZnet是一家無(wú)晶圓廠半導(dǎo)體公司,成立于1998年。產(chǎn)品包括互聯(lián)網(wǎng)處理器iMCU?,它采用TOE(TCP/IP卸載引擎)技術(shù),基于獨(dú)特的專利全硬連線TCP/IP。iMCU?面向各種應(yīng)用中的嵌入式互聯(lián)網(wǎng)設(shè)備。

WIZnet在全球擁有70多家分銷商,在香港、韓國(guó)、美國(guó)設(shè)有辦事處,提供技術(shù)支持和產(chǎn)品營(yíng)銷。

香港辦事處管理的區(qū)域包括:澳大利亞、印度、土耳其、亞洲(韓國(guó)和日本除外)。

審核編輯 黃宇

-

WIZnet

+關(guān)注

關(guān)注

3文章

20瀏覽量

42431 -

音頻傳輸

+關(guān)注

關(guān)注

0文章

48瀏覽量

12264 -

I2S

+關(guān)注

關(guān)注

1文章

72瀏覽量

42778

發(fā)布評(píng)論請(qǐng)先 登錄

音頻總線I2S協(xié)議:I2S收發(fā)模塊FPGA的仿真設(shè)計(jì)

「正點(diǎn)原子NANO STM32開發(fā)板資料連載」第三十五章 USB 虛擬串口實(shí)驗(yàn)

音頻接口I2S實(shí)驗(yàn)

模擬電路網(wǎng)絡(luò)課件 第三十五節(jié):負(fù)反饋放大電路的穩(wěn)定問題

基于FPGA和AD1836的I2S接口設(shè)計(jì)

I2S接口工作原理_I2S接口介紹

數(shù)字接口I2S數(shù)據(jù)傳輸模式和應(yīng)用框圖

stm32 讀取sd卡圖片顯示_「正點(diǎn)原子STM32Mini板資料連載」第三十五章 漢字顯示實(shí)驗(yàn)...

【正點(diǎn)原子FPGA連載】第三十五章高速AD/DA實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開發(fā)指南_V2.1

基于I2S接口的Linux內(nèi)核音頻技術(shù)

科普小課堂 | 5分鐘讀懂I2S、SPDIF數(shù)字音頻傳輸協(xié)議

從藍(lán)牙音頻模塊中了解I2S的主端和從端功能應(yīng)用

第三十五章 I2S——音頻傳輸接口

第三十五章 I2S——音頻傳輸接口

評(píng)論