大家好,談到同步復位和異步復位,那咱們就不得不來聊一聊復位這個詞了。在數字邏輯電路設計中,電路通過復位來啟動,復位猶如數字電路的“起搏器”。那在設計中,主要會出現以下三種類型的,一是無復位:天生就強壯著,上電就啟動;二是異步復位:好心人路過,隨便踢了一腳,起搏了,這完全沒有心理準備,隨時都有可能復活啊;三是同步復位:專業救援隊,手按住胸口,不起博按住不放啊。直到聽到“砰砰”聲才離開,非常關鍵,必須要按住一會會。

那下面咱們就來詳細聊聊這三種類型。

一、無復位

沒見過這樣寫代碼的,竟然沒有復位,老師都說數字電路離不開復位的,沒有復位,寄存器怎么賦初值啊?沒有確定的初值,這電路怎么工作呢?

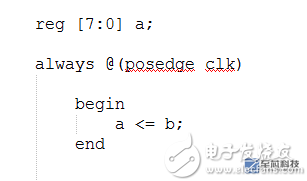

其實,不用擔心,FPGA上電之后,寄存器初始值默認為“0”,當然,也可以人為的賦初值。下面為無復位的代碼舉例:

reg [7:0] a;

always @(posedge clk)

begin

a <= b;

end

如果沒有復位信號,省了很多資源,編譯和布線時間也縮短不少,如果規模很大,對提高設計整體性能也是有幫助的。但是在數字電路設計中,我們很少不用復位電路。到是我們經常利用FPGA這個特性,自己產生內部復位電路。

二、異步復位

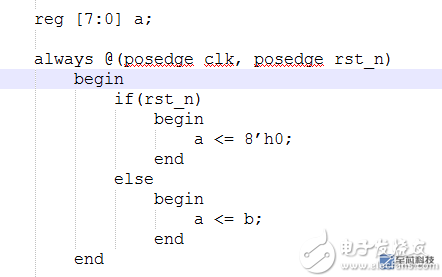

異步復位電路描述:在always語句中添加復位信號在敏感量列表中,即可實現異步復位。下面為異步復位的代碼舉例以及電路圖舉例:

reg [7:0] a;

always @(posedge clk, posedge rst_n)

begin

if(rst_n)

begin

a <= 8’h0;

end

else

begin

a <= b;

end

end

異步復位的缺點:

異步復位對復位信號要求很嚴格的,不然隨便一個毛刺就會把電路給復位掉的。

另外,異步復位信號依賴于FPGA內部的傳導延時,因此,在微小的電壓或溫度差異下,設計都有可能輸出錯誤,設計的可移植性也很差。上面不是說了嘛,這隨便一腳提過來,有時候能感覺到,有時候感覺不到啊。冬天穿個大棉襖,就得使個大勁才能提醒。

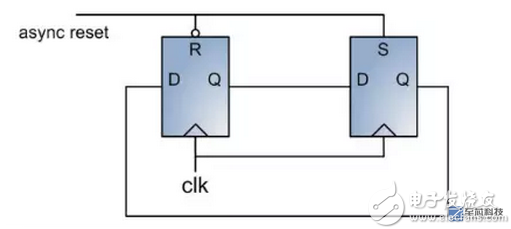

正因為對不同寄存器延遲是不同的,所以容易引發間斷性設計問題。怎么理解呢?

如圖所示,2 bit的移位寄存器組成一個環,復位后,左邊寄存器清零,右邊寄存器置位,而且都在同一上升沿觸發,所以,如果左邊寄存器上升沿來的時候,復位信號已經釋放掉了,但是右邊寄存器還處于復位狀態,這個時候數據就錯誤。

異步復位的優點:

異步復位不依賴于時鐘。所以如果時鐘是外部輸入的,而且時鐘有可能丟失,例如處于省電模式時,只能使用異步復位。

另外一個優勢是設計更快的物理實現。相對于同步復位,異步復位有更寬松的時序約束。從而布局布線工具使用更少的時間便可達到約束條件。

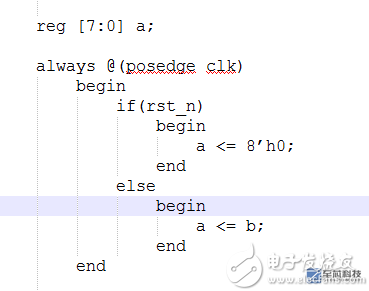

三、同步復位

同步復位就是非常專業,不留一點馬虎,和他的名字一樣,只在時鐘的有效沿發生,所以一個有效的同步信號,至少要維持一個時鐘周期(把你叫不醒,是不會停的)。由于僅僅在時鐘的有效沿有效,所以可以濾除復位信號上的毛刺,電路可靠性好很多。下面為同步復位的代碼舉例:

reg [7:0] a;

always @(posedge clk)

begin

if(rst_n)

begin

a <= 8’h0;

end

else

begin

a <= b;

end

end

所以,總結一下。其優點是“彌補了異步復位的所有缺點”,其缺點是“沒有異步復位的優點“”。這個總結夠簡單吧。

總結

我們熟悉了3種復位方式,了解了他們的脾氣,那就總結一下,在我們平時設計中如何使用他們。

盡量用同步復位,如果你的規模不是特別大,雖然占有布線資源多一點,但是對系統可靠性還是有幫助的。

規模很大的時候,可以考慮混和復位方式,在什么場合呢?比如說設計中有多個IP核和功能模塊,要求有不同的復位方式,這個時候就要求混和復位方式,另外,還有電路延遲,大型電路中兩個模塊之間信號延遲可能超過10ns,如果時鐘周期為3ns,需要3個時鐘周期才能通過,所以,大型設計中完全同步是非常不容易的。如圖所示為一個復雜的混和復位樹。各種復位都用上了。

各位,加油,共同進步!

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614902 -

同步復位

+關注

關注

0文章

27瀏覽量

10848

發布評論請先 登錄

Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

簡談同步復位和異步復位

簡談同步復位和異步復位

評論