文章來源:半導(dǎo)體全解

原文作者:圓圓De圓

本文主要講述芯片(光刻、注入、薄膜、刻蝕)四大工藝。

這一篇文章介紹幾種芯片加工工藝,在Fab里常見的加工工藝有四種類型,分別是圖形化技術(shù)(光刻)?摻雜技術(shù)?鍍膜技術(shù)和刻蝕技術(shù)。

具體工藝包括光刻(lithography)、離子注入(ion implantation)?快速退火(rapid thermal process, RTP)?等離子體增強(qiáng)化學(xué)氣相沉積(plasma enhanced chemical vapor deposition, PECVD)?濺射(sputtering)?干法刻蝕和濕法腐蝕等?

一、圖形化技術(shù)(光刻)

圖形化技術(shù)一般指光刻工藝,它是半導(dǎo)體技術(shù)得以迅猛發(fā)展的最重要推力之一,起始于印刷技術(shù)中的照相制版技術(shù)?

光刻技術(shù)讓人們得以在微納尺寸上通過光刻膠呈現(xiàn)任何圖形,并與其它工藝技術(shù)結(jié)合后將圖形轉(zhuǎn)移至材料上,實(shí)現(xiàn)人們對(duì)半導(dǎo)體材料與器件的各種設(shè)計(jì)和構(gòu)想?

光刻技術(shù)使用的光源對(duì)圖形精度有直接的影響,光源類型一般有紫外?深紫外?X射線以及電子束等,它們對(duì)應(yīng)的圖形精度按上述順序依次提升?

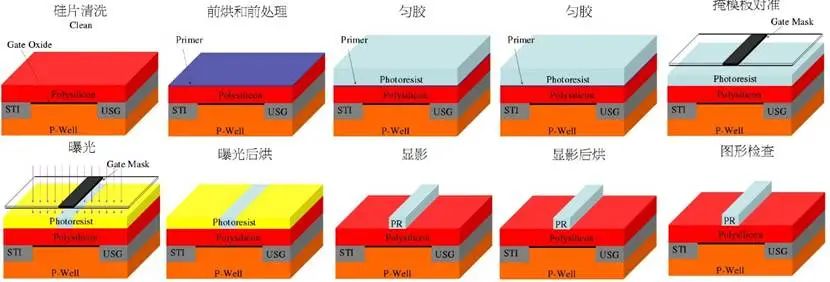

標(biāo)準(zhǔn)的光刻工藝流程如下圖所示,包括表面處理?勻膠?前烘?曝光?曝光后烘烤?顯影?堅(jiān)膜和檢查等步驟?

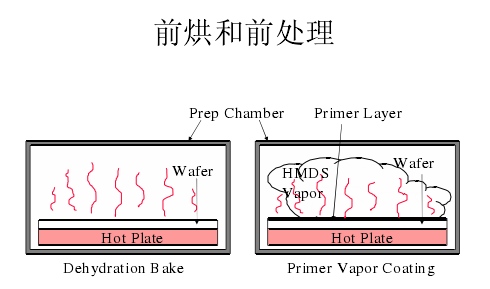

基片表面通常會(huì)吸附空氣中的H20分子,這對(duì)光刻效果很不利,所以首先需要對(duì)基片進(jìn)行脫水處理,這就是烘烤?對(duì)于表面為親水性的基片,它們與疏水的光刻膠之間的附著力不足,這樣會(huì)引發(fā)光刻膠脫落或圖形移位等問題,所以需要在表面涂一層增黏劑?

目前應(yīng)用較多的增黏劑是六甲基乙硅氮烷(hexa-methyl-disilazane, HMDS)與三甲基甲硅烷基二乙胺(tri-methyl-silyl-diethyl-amine, TMSDEA)?

表面處理完成后,開始勻涂光刻膠?勻膠后的光刻膠厚度除了與光刻膠本身的黏性有關(guān)外,還受勻膠時(shí)所采用的轉(zhuǎn)速影響,一般可粗略地認(rèn)為,光刻膠厚度與轉(zhuǎn)速的平方根成反比?

勻膠結(jié)束后,需要通過烘烤使光刻膠的溶劑揮發(fā)出來,這樣可以進(jìn)一步提高光刻膠的黏附力,該過程即前烘?

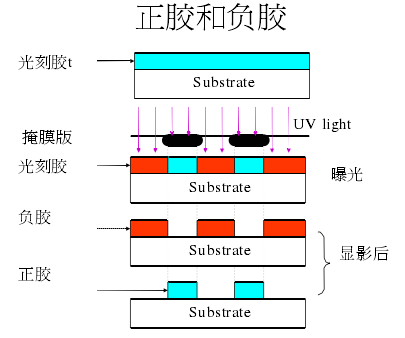

上述步驟一切就緒后,就來到了曝光環(huán)節(jié)?光刻膠有正膠和負(fù)膠之分,兩者曝光后的性質(zhì)恰好相反?

以正膠舉例,未經(jīng)曝光的光刻膠不溶于顯影液,曝光后則易溶于顯影液?曝光時(shí),光源透過有圖形的掩膜版照射到勻膠后的基片上,使光刻膠圖形化受光?

通常情況下,在曝光前需將基片與掩膜版對(duì)準(zhǔn),以精準(zhǔn)控制曝光位置?曝光時(shí)長須嚴(yán)格把握,過長或過短都會(huì)導(dǎo)致圖形失真?

曝光后,有時(shí)需要再烘烤一下基片,以消除駐波的影響,但這一步驟不是必須的,可跳過它直接進(jìn)行顯影?

將基片放于顯影液中令曝光的光刻膠溶解的過程就是顯影,目的是把掩膜版上的圖形準(zhǔn)確地復(fù)制到光刻膠上?顯影時(shí)長也須嚴(yán)格把握,時(shí)間太短顯影不徹底,太長則圖形失真?

接下來是堅(jiān)膜,通過進(jìn)一步的烘烤使光刻膠薄膜更牢固地黏附在基片表面,還可增加膠膜的抗刻蝕能力,堅(jiān)膜溫度一般略高于前烘溫度?最后,利用顯微鏡檢查圖形是否符合預(yù)期?

經(jīng)過其它工藝將圖形轉(zhuǎn)移至材料上后,光刻膠便完成它的使命,需要將其去掉?去膠有濕法和干法兩種,前者利用溶解能力強(qiáng)的有機(jī)溶劑(一般采用丙酮)將膠膜溶解,后者利用氧等離子體將膠膜刻蝕去除?

二、摻雜技術(shù)

摻雜技術(shù)在半導(dǎo)體技術(shù)里也是不可或缺的,它可以根據(jù)需要改變半導(dǎo)體材料的電學(xué)特性?常見的摻雜方式一般有兩種,分別是熱擴(kuò)散和離子注入?

行業(yè)中常采用了離子注入的摻雜方式,涉及離子注入和RTP兩種工藝?

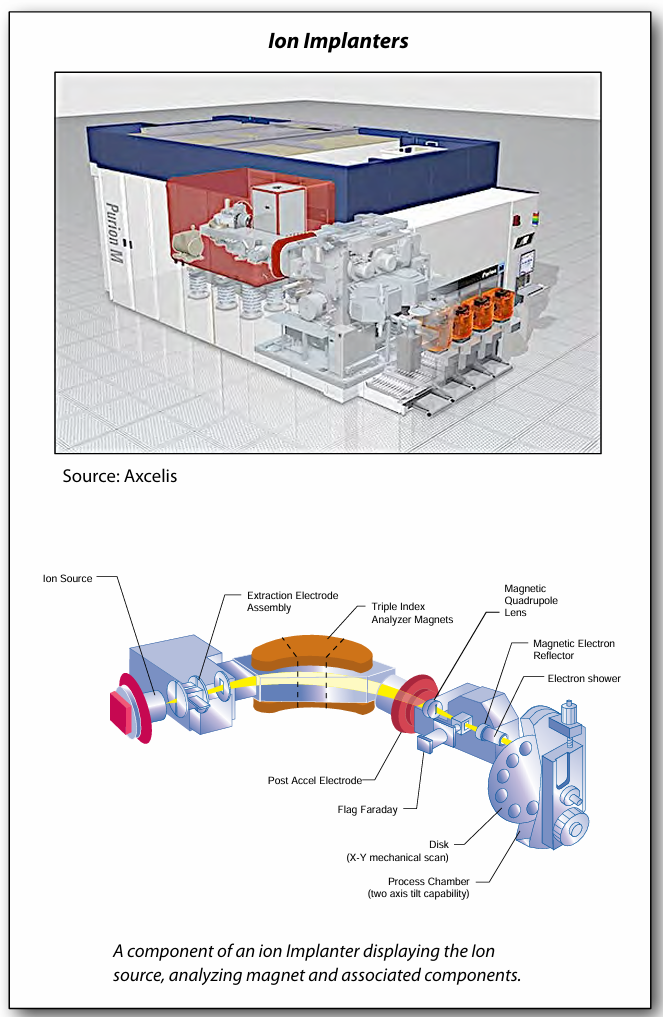

(1)離子注入

離子注入是利用高能離子直接轟擊半導(dǎo)體基片實(shí)現(xiàn)摻雜的?與熱擴(kuò)散相比,離子注入有著諸多優(yōu)點(diǎn)?待注入的離子是利用質(zhì)量分析器篩選的,確保了高摻雜純度?在整個(gè)注入過程,基片一般保持室溫或稍高一點(diǎn)的溫度,可選用的掩蔽膜有很多,如二氧化硅(SiO2)?氮化硅(Si3N4)和光刻膠等,這使自對(duì)準(zhǔn)掩蔽技術(shù)具有很高的靈活性?

離子注入的劑量可精確控制,注入后雜質(zhì)離子在同一平面內(nèi)的分布十分均勻,注入結(jié)果的重復(fù)性也很高?

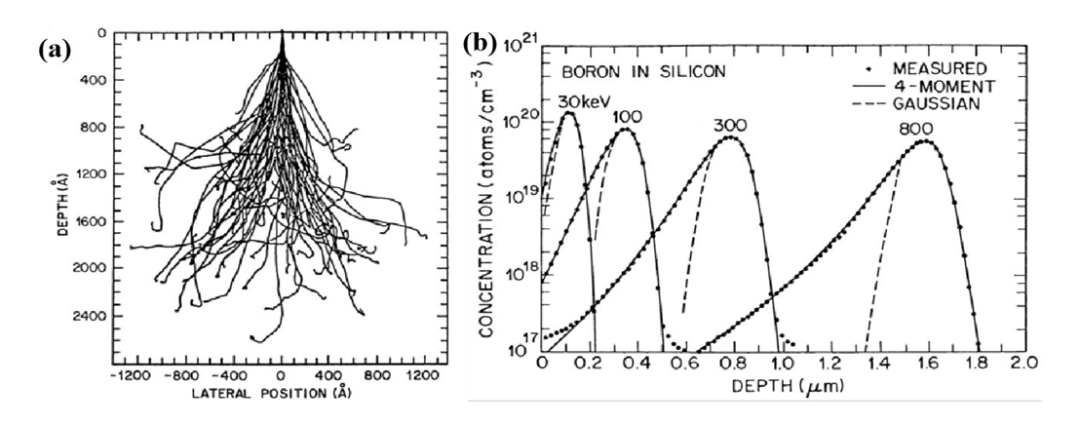

離子注入的深度由注入離子的能量決定,通過控制離子的能量和劑量,可操控注入后雜質(zhì)離子在基片中的分布,還可以連續(xù)多次地實(shí)施不同方案的注入,借此獲得各種形態(tài)的雜質(zhì)分布?值得注意的是,在基片是單晶的情況下,若離子注入的方向與基片的晶向平行,將出現(xiàn)溝道效應(yīng),即一部分離子會(huì)順著溝道運(yùn)動(dòng),注入深度會(huì)變得難以控制,為避免溝道效應(yīng)的出現(xiàn),通常使單晶基片的主軸方向偏離注入方向7°左右,或在基片表面覆蓋一層無定形介質(zhì)層?

下圖展示了若干離子注入后的雜質(zhì)分布曲線,經(jīng)四次不同能量與劑量的注入方案后,最后得到的分布在縱深方向上已較為均勻?經(jīng)溝道效應(yīng)修正后,合成分布的均勻性得到了進(jìn)一步提高?

雖然離子注入有許多優(yōu)點(diǎn),但也不可避免地存在缺點(diǎn),比如對(duì)基片的晶體結(jié)構(gòu)損傷較為嚴(yán)重?高能量的離子注入到基片內(nèi)部后,通過碰撞將能量傳遞給基片原子核及其電子,使其脫離晶格束縛進(jìn)入間隙,從而形成間隙一空位缺陷對(duì)?

損傷嚴(yán)重時(shí),基片晶體中某些區(qū)域的結(jié)構(gòu)可能遭到徹底的破壞而變成無序的非晶區(qū)?

晶格損傷對(duì)半導(dǎo)體材料的電學(xué)性質(zhì)影響極大,如降低載流子遷移率,減少非平衡載流子的壽命等?最重要的是,注入的雜質(zhì)絕大多數(shù)都處在不規(guī)則的間隙位置,無法形成有效摻雜?因此,離子注入后必須修復(fù)晶格損傷與電激活雜質(zhì)?

(2)快速退火(RTP)

熱退火是最有效的修復(fù)離子注入帶來的晶格損傷和電激活雜質(zhì)的方法?

在高溫下,基片晶體里的間隙——空位缺陷對(duì)會(huì)因復(fù)合而消失;非晶區(qū)也會(huì)從與單晶區(qū)的交界面開始,以固相外延的方式重結(jié)晶?為防止基片材料在高溫下被氧化,熱退火過程需要在真空或惰性氣體環(huán)境下進(jìn)行?

傳統(tǒng)熱退火所需時(shí)間較長,會(huì)導(dǎo)致雜質(zhì)擴(kuò)散嚴(yán)重而形成再分布?RTP工藝的出現(xiàn)解決了這一問題,它可在縮短退火時(shí)間的前提下很大程度地完成晶格損傷的修復(fù)與雜質(zhì)的電激活?

根據(jù)熱源的不同,RTP分為以下幾種類型:掃描電子束?脈沖電子束與離子束?脈沖激光?連續(xù)波激光與寬帶非相干光源(鹵燈?石墨加熱器?電弧燈)等,其中寬帶非相干光源的應(yīng)用最為廣泛?它們都可以在剎那間將基片加熱到所需溫度,在短時(shí)間內(nèi)完成退火,有效地降低了雜質(zhì)的擴(kuò)散程度?

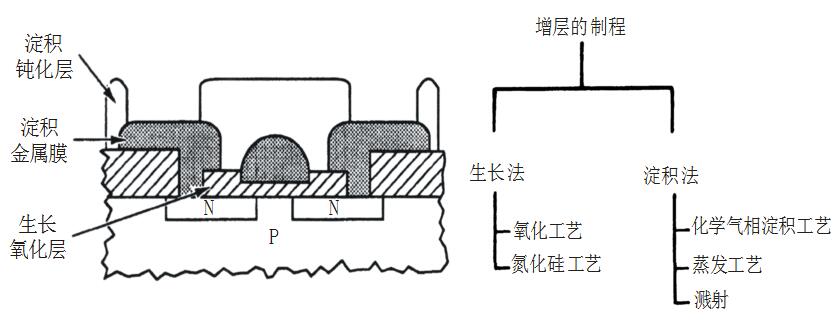

三、鍍膜技術(shù)

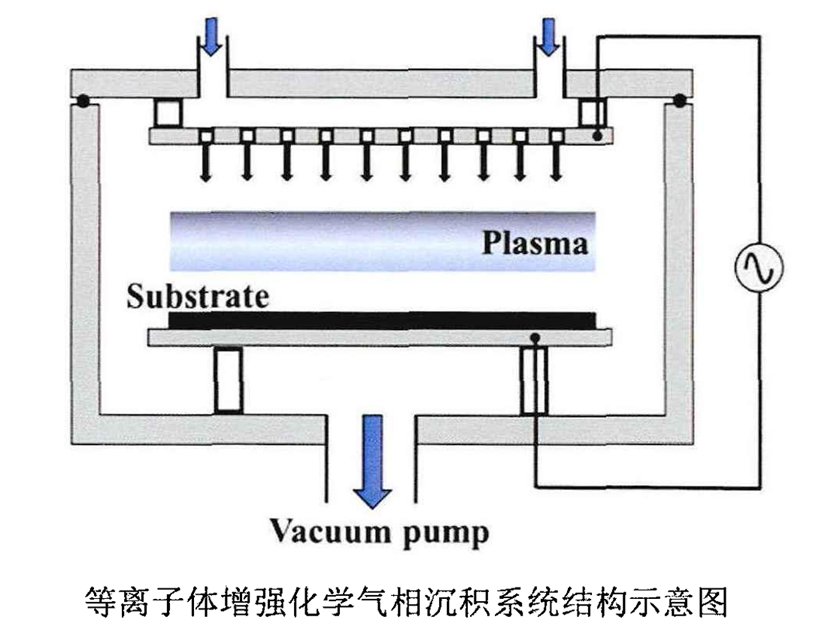

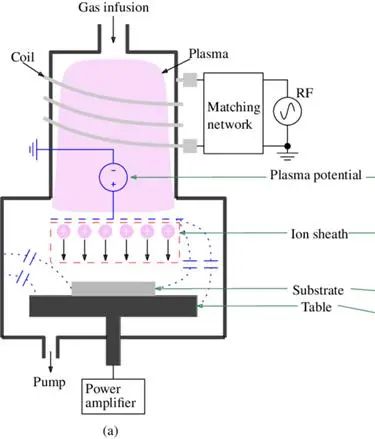

(1)等離子體增強(qiáng)化學(xué)氣相沉積(PECVD)

PECVD是化學(xué)氣相沉積(chemical vapor deposition, CVD)鍍膜方法的其中一種,此外還有另外兩種,分別是常壓CVD(atmospheric pressure CVD, APCVD)與低壓CVD(low pressure CVD, LPCVD)?

目前,PECVD是三種類型中應(yīng)用較為廣泛的,PECVD利用射頻(radio frequency, RF)等離子體引發(fā)和保持化學(xué)變化,而且該化學(xué)變化在非高溫環(huán)境下就可以進(jìn)行,所以薄膜沉積溫度低,沉積速率高,其設(shè)備示意圖如下圖所示?

這種方式得到的薄膜具有突出的附著性與電學(xué)性質(zhì)?很低的微孔密度?很高的均勻性以及較強(qiáng)的小尺寸填充能力?

影響PECVD鍍膜質(zhì)量的因素有襯底溫度?氣流速度?氣壓?RF功率和頻率等?

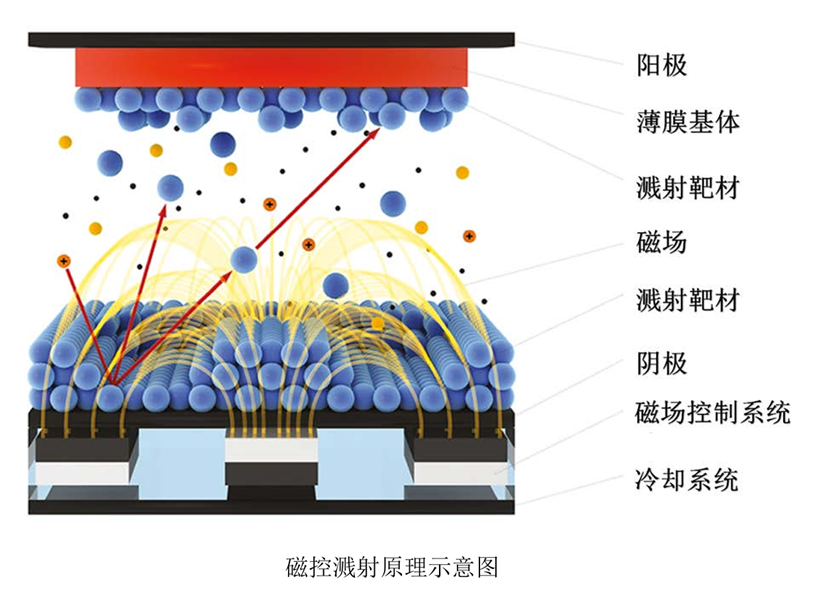

(2)濺射

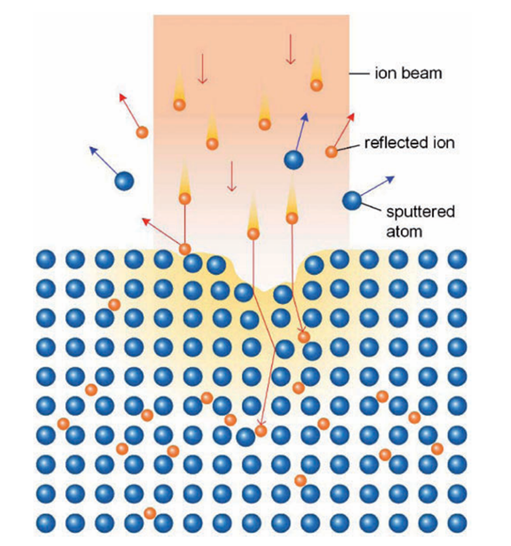

濺射是一種物理氣相沉積(physical vapor deposition, PVD)鍍膜方法?

帶電離子[一般為氬離子(Ar+)]在電場中加速后具備了一定的動(dòng)能,它們被引向目標(biāo)靶材并碰撞靶分子,使其脫離靶材而得以濺射出來?

這些分子也帶有一定強(qiáng)度的動(dòng)能,它們向襯底方向運(yùn)動(dòng)并在襯底上沉積?以上就是濺射鍍膜的過程,其設(shè)備示意圖如所示?

常用的濺射電源有直流和射頻兩種,直流濺射可直接應(yīng)用于金屬等導(dǎo)電性良好的材料,而對(duì)于絕緣體材料,則只能通過射頻濺射的方式才能實(shí)現(xiàn)鍍膜?

普通濺射的沉積速率較低,工作氣壓較高,所鍍薄膜的質(zhì)量不佳,磁控濺射的出現(xiàn)較為理想地解決了這個(gè)問題?它利用外加磁場使離子的運(yùn)動(dòng)軌跡由直線變成繞磁場方向螺旋前進(jìn)的曲線,延長了離子的運(yùn)動(dòng)軌跡,提升了與靶分子的碰撞效率,也即提升了濺射效率,使沉積速率升高,工作氣壓降低,因而鍍膜質(zhì)量得到了很大的提升?

四、刻蝕技術(shù)

刻蝕有干法與濕法兩種方式,前者不使用溶液,后者使用特定的溶液,兩種刻蝕工藝因此而得名?

一般情況下,刻蝕之前需要通過光刻制備掩蔽層(可以直接由光刻膠充當(dāng))以保護(hù)不需刻蝕的區(qū)域?

(1)干法刻蝕

常用的干法刻蝕一般有電感耦合等離子體(inductively coupled plasma, ICP)刻蝕?離子束刻蝕(ion beam etching, IBE)和反應(yīng)離子刻蝕(reactive ion etching, RIE)等三種類型?

在ICP刻蝕中,輝光放電產(chǎn)生的等離子體里存在大量的化學(xué)活性很強(qiáng)的游離基(游離態(tài)的原子?分子或原子團(tuán)等),它們會(huì)與目標(biāo)材料發(fā)生化學(xué)反應(yīng)生成揮發(fā)性產(chǎn)物,這樣便達(dá)到了刻蝕目的;

IBE是利用高能離子(來自于惰性氣體的電離)直接轟擊目標(biāo)材料表面實(shí)現(xiàn)刻蝕的,這是一個(gè)物理過程;

RIE可被視作前面兩者的結(jié)合,將IBE所用的惰性氣體改為ICP刻蝕所用的氣體,就變成了RIE?

干法刻蝕設(shè)備示意圖如圖所示?

對(duì)于干法刻蝕而言,縱向刻蝕速率遠(yuǎn)遠(yuǎn)大于橫向刻蝕速率,即縱橫比高,可以精確地復(fù)制掩蔽層上的圖形?但干法刻蝕對(duì)掩蔽層也有一定的刻蝕效果,選擇性(對(duì)目標(biāo)材料與掩蔽層的刻蝕速率之比)較差,尤其是IBE,可能會(huì)對(duì)材料表面無選擇地全部刻蝕?

(2)濕法腐蝕

通過將目標(biāo)材料放于可與之發(fā)生化學(xué)反應(yīng)的溶液(即腐蝕液)里實(shí)現(xiàn)刻蝕效果的方式叫作濕法腐蝕?

這種刻蝕方式操作簡單?成本低廉?選擇性好,但縱橫比很低,掩蔽層邊緣下面受保護(hù)的材料會(huì)遭受腐蝕,不如干法刻蝕精準(zhǔn)?

為減少低縱橫比帶來的負(fù)面影響,需要選擇合適的腐蝕速率?影響腐蝕速率的因素有腐蝕液濃度?腐蝕時(shí)間和腐蝕液溫度等?

-

芯片制造

+關(guān)注

關(guān)注

10文章

688瀏覽量

29732 -

光刻

+關(guān)注

關(guān)注

8文章

347瀏覽量

30691 -

加工工藝

+關(guān)注

關(guān)注

0文章

37瀏覽量

11022

原文標(biāo)題:一文了解芯片(光刻、注入、薄膜、刻蝕)四大工藝

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

【「大話芯片制造」閱讀體驗(yàn)】+芯片制造過程工藝面面觀

【「大話芯片制造」閱讀體驗(yàn)】+ 芯片制造過程和生產(chǎn)工藝

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測

霍爾IC芯片的制造工藝介紹

集成電路應(yīng)用四大技術(shù)比較

動(dòng)力電池pack生產(chǎn)工藝流程_動(dòng)力電池PACK四大工藝介紹

微流控芯片五大優(yōu)點(diǎn)及四大缺點(diǎn)分析

拜騰工廠四大工藝車間已經(jīng)開始建設(shè),計(jì)劃2019年10月正式量產(chǎn)

芯片制造四大基本工藝

不只依賴光刻機(jī)!芯片制造的五大工藝大起底!

芯片制造的四大工藝介紹

芯片制造的四大工藝介紹

評(píng)論