在日常PCB設(shè)計中,我們經(jīng)常會看到整版大面積鋪銅,看起來既專業(yè)又美觀,好像已經(jīng)成了“默認(rèn)操作”。但你真的了解這樣做的后果嗎?尤其是在電源類板子和高速信號板中,鋪銅可不是越多越好,處理不好反而會影響電氣性能甚至埋下安全隱患!

今天我們就來詳細(xì)聊聊——

不同類型PCB該怎么鋪銅?

鋪銅距離對阻抗的影響有多大?

如何正確設(shè)置銅皮間距?

電源類PCB:鋪銅≠屏蔽,反而可能是“雷區(qū)”!

電源板電流大、電壓高,我們在設(shè)計時經(jīng)常需要預(yù)留爬電間距,尤其是高壓與低壓之間更要嚴(yán)格區(qū)分。此時如果大面積鋪銅,很多時候會變成碎銅,這些碎銅不但起不到屏蔽作用,反而可能成為干擾源。

建議:

電源類PCB鋪銅要慎重,不要盲目整版鋪銅,優(yōu)先考慮安全間距與EMC設(shè)計。

高速PCB:銅皮與阻抗線的“微妙關(guān)系”

高速信號講究阻抗控制,如果你隨意把銅皮鋪得太近,就可能大幅改變線的阻抗,從而導(dǎo)致信號反射、失真、EMI等問題。

實驗驗證:

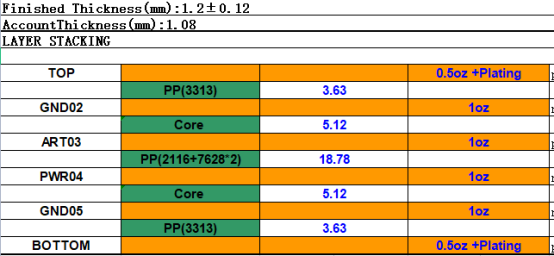

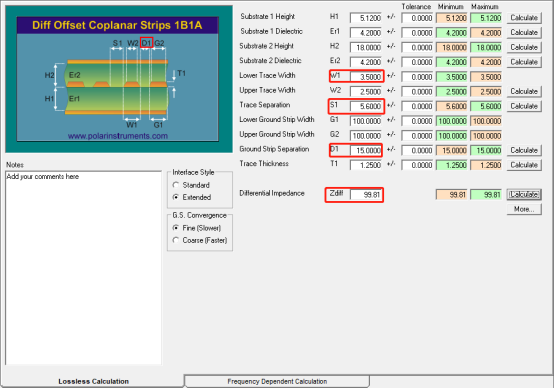

我們使用以下疊層結(jié)構(gòu)進(jìn)行仿真分析:

圖1:疊層結(jié)構(gòu) 我們計算了表層與內(nèi)層100Ω差分線的線寬和線距:

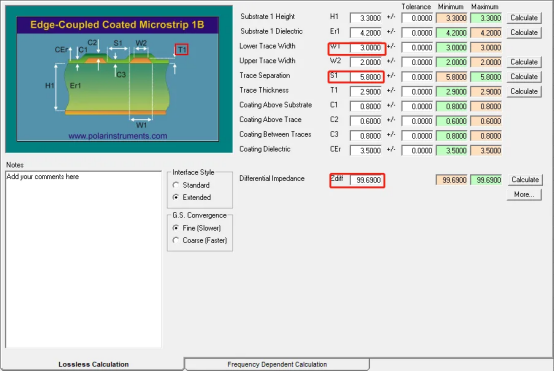

圖2:表層計算結(jié)果

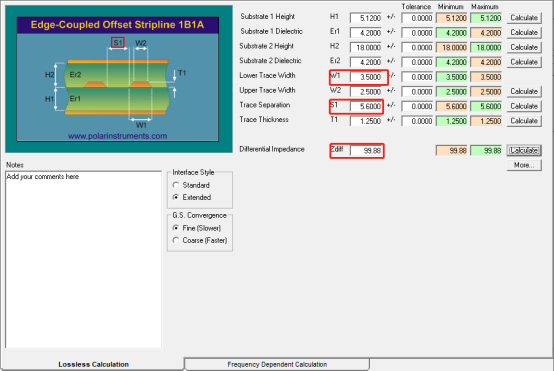

圖3:內(nèi)層計算結(jié)果

表層差分線寬/距為 3mil/5.8mil,內(nèi)層為 3.5mil/5.6mil。

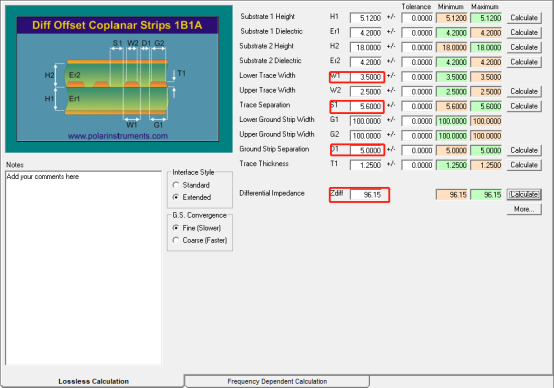

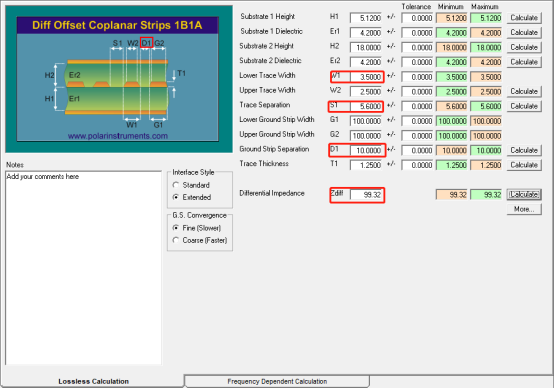

然后我們模擬在差分線兩側(cè)鋪上銅皮的情況,銅皮距離為5mil,看看對阻抗的影響:

圖4、圖5:銅皮距離5mil下的阻抗變化 結(jié)果: 不論外層還是內(nèi)層,差分阻抗都下降了約 3Ω!

間距設(shè)置多少才合適?我們繼續(xù)測試!

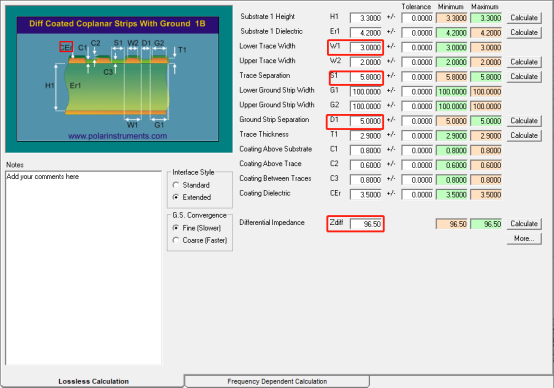

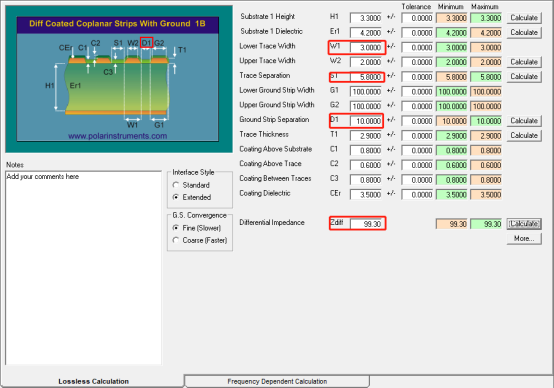

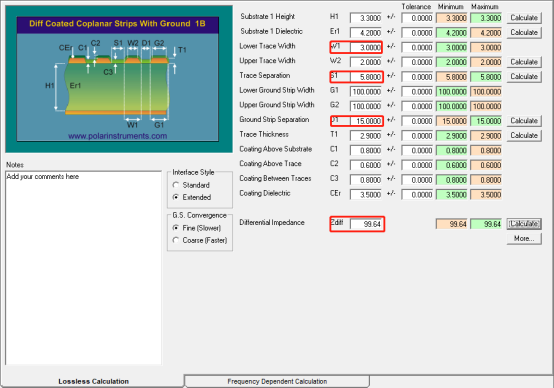

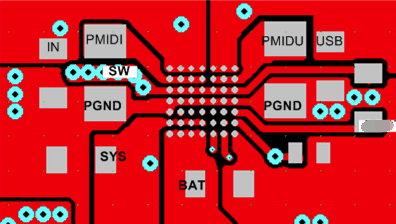

進(jìn)一步仿真銅皮離差分線 10mil和15mil 時的影響:

圖6 ~ 圖9:間距變化下的仿真對比

結(jié)論非常直觀:

距離10mil時,仍有約0.5Ω的下降

距離15mil時,阻抗變化可忽略不計!

實戰(zhàn)建議總結(jié):

銅皮與阻抗線的間距至少15mil以上

1、空間允許時建議設(shè)置為20mil更保險

2、避免整版鋪銅,可使用網(wǎng)格或小塊鋪銅方式補強

3、關(guān)注DRC規(guī)則設(shè)置,提前預(yù)警銅皮距離

寫在最后

別再把鋪銅當(dāng)“裝修工程”了!真正專業(yè)的高速PCB設(shè)計,關(guān)鍵在于每一個細(xì)節(jié)處理。你可能看不到它,但信號完整性、EMC表現(xiàn)卻會如實反映每一次輕率鋪銅的代價。

本文凡億教育原創(chuàng)文章,轉(zhuǎn)載請注明來源!

-

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4815瀏覽量

90862 -

高速信號

+關(guān)注

關(guān)注

1文章

248瀏覽量

18240 -

PCB鋪銅

+關(guān)注

關(guān)注

0文章

10瀏覽量

7403

原文標(biāo)題:高速PCB鋪銅到底怎么鋪?99%工程師都忽視了這幾點!

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

為什么那么多PCB設(shè)計師,選擇鋪銅?非鋪不可?

表底層鋪銅對PCB設(shè)計有何意義

表底層鋪銅對PCB的優(yōu)劣之處

表底層鋪銅對PCB是否有幫助?到底有沒有必要?

PCB鋪銅對電路的好處

pcb電源層需要鋪銅嗎?

PCB板設(shè)計時,鋪銅有什么技巧和要點?

為什么那么多PCB設(shè)計師,選擇鋪銅?非鋪不可?

高速PCB鋪銅到底怎么鋪

高速PCB鋪銅到底怎么鋪

評論