我知道,我對(duì)與電子有關(guān)的所有事情都很著迷,但不論從哪個(gè)角度看,今天的現(xiàn)場(chǎng)可編程門陣列(FPGA),都顯得“鶴立雞群”,真是非常棒的器件。如果在這個(gè)智能時(shí)代,在這個(gè)領(lǐng)域,想擁有一技之長(zhǎng)的你還沒(méi)有關(guān)注FPGA,那么世界將拋棄你,時(shí)代將拋棄你。

作為純數(shù)字電路的FPGA,實(shí)現(xiàn)平方根是比較麻煩的。畢竟硬件不支持這種算法。

好在廠家的IP核中有相關(guān)的平方根IP庫(kù),所以用起來(lái)也很方便。

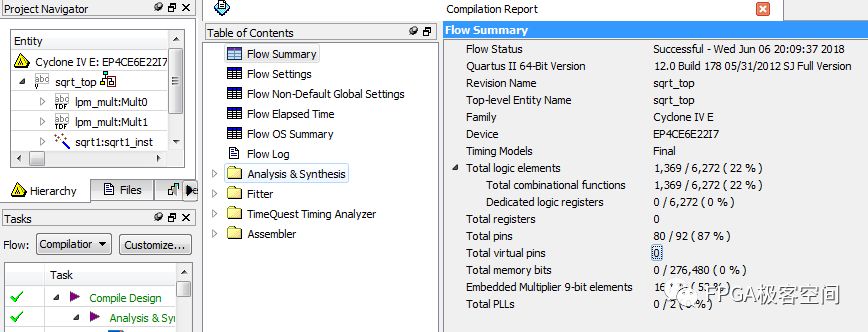

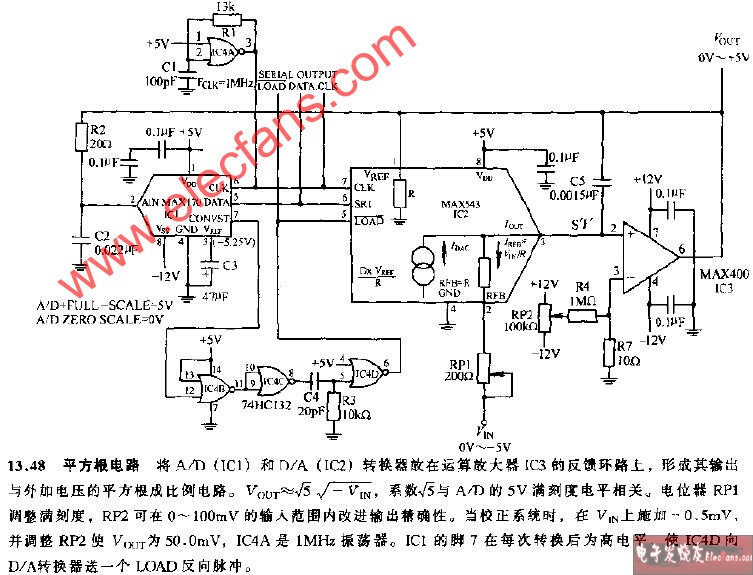

上圖是在QUARTUS下調(diào)用庫(kù)中的IP核,綜合適配后的資源使用情況,邏輯單元使用的1369個(gè),占總資源的22%,片上硬件乘法器使用了16個(gè)。可以說(shuō)是在資源有限的情況下,使用資源量還是很大的。

前幾篇文章中,我們介紹了使用CORDIC算法計(jì)算三角函數(shù)sin和cos的值。計(jì)算三角函數(shù)sin和cos的值是利用CORDIC算法的旋轉(zhuǎn)模式來(lái)進(jìn)行的。而在向量模式下,可以使用CORDIC算法計(jì)算平方根。

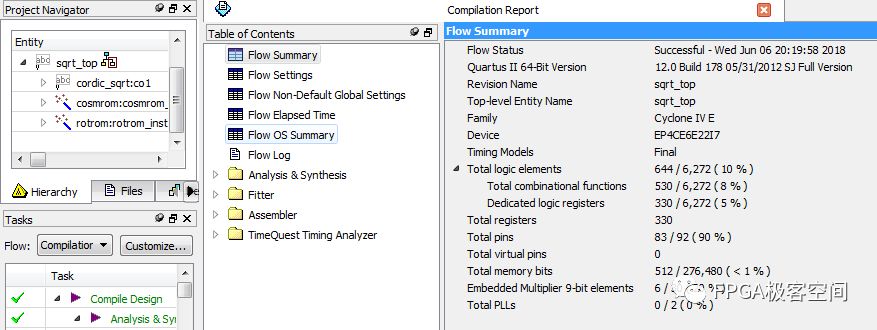

如圖,使用CORDIC算法計(jì)算平方根,F(xiàn)PGA資源的使用情況。邏輯單元使用了10%,乘法器使用的6個(gè),片上ram只是用的不到1%。可以說(shuō)在資源有限的情況下,是非常好的選擇 。但是要注意,算法本身可使用流水線操作,也可使用其他方式操作,計(jì)算周期要根據(jù)迭代的次數(shù)決定,迭代次數(shù)越大,計(jì)算越精確,同樣,計(jì)算的周期也越長(zhǎng)。

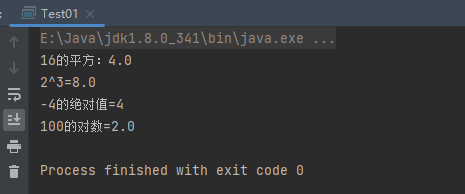

上圖是迭代16次后的結(jié)果,可以清楚地看到,輸入xi,yi,輸出sqrt_out,結(jié)果非常精確。在時(shí)序不是很緊的情況下,可以使用這種方法。

具體詳細(xì)的算法,可根據(jù)之前介紹的CORDIC算法自行推理。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21982瀏覽量

614568 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1637瀏覽量

81639 -

乘法器

+關(guān)注

關(guān)注

9文章

211瀏覽量

37847

原文標(biāo)題:FPGA中的平方根

文章出處:【微信號(hào):ALIFPGA,微信公眾號(hào):FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

如何打印浮動(dòng)閥以及平方根和平方根函數(shù)?

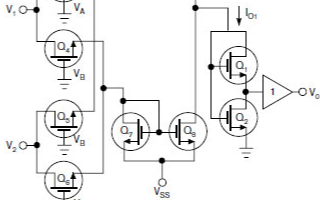

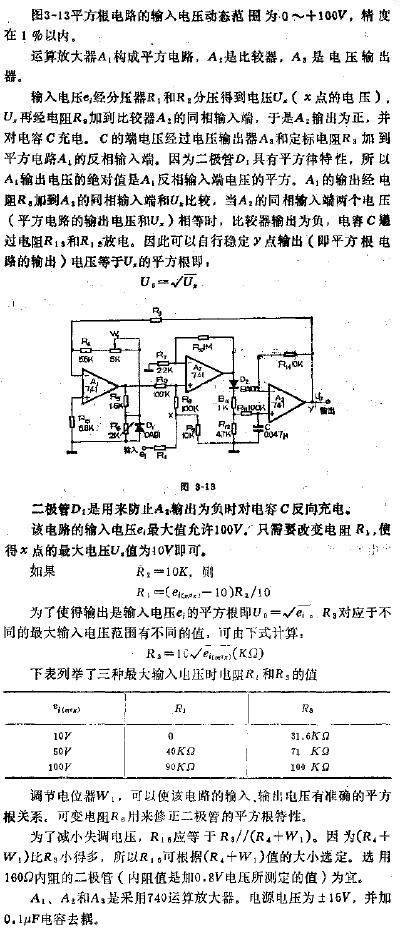

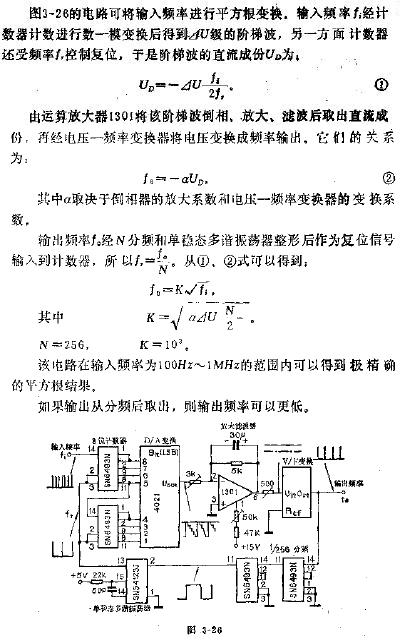

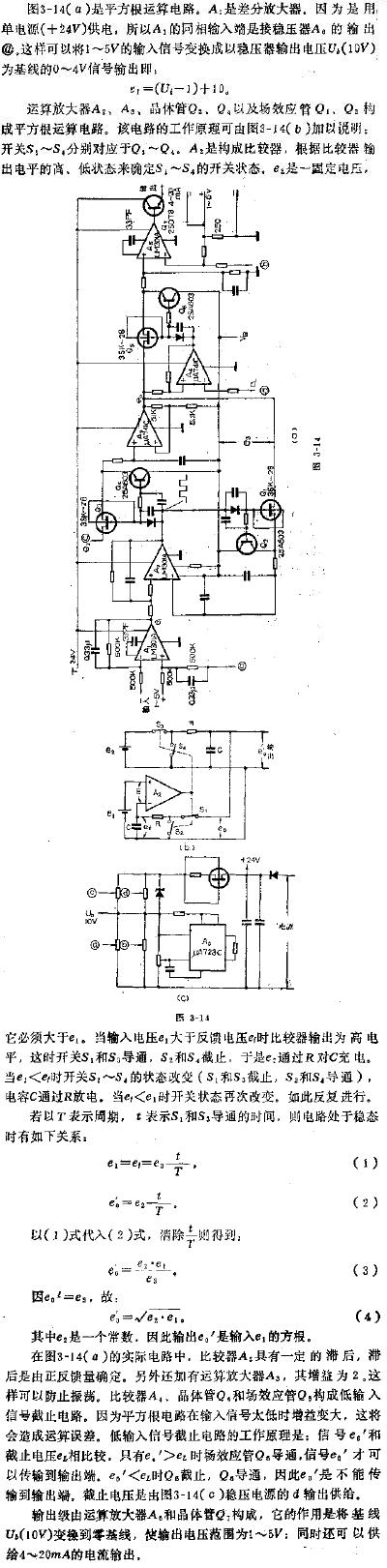

請(qǐng)問(wèn)怎樣去設(shè)計(jì)平方根計(jì)算模擬電路?

MCU裸系統(tǒng)下快速平方根實(shí)現(xiàn)相關(guān)資料推薦

數(shù)字信號(hào)處理平方根VHDL代碼

平方根模式下的AD532模擬處理器電路

采用MOSFET器件實(shí)現(xiàn)模擬平方根計(jì)算裝置的設(shè)計(jì)

MCU裸系統(tǒng)下快速平方根實(shí)現(xiàn)

純數(shù)字電路的FPGA,實(shí)現(xiàn)平方根是比較麻煩的

純數(shù)字電路的FPGA,實(shí)現(xiàn)平方根是比較麻煩的

評(píng)論