RAS:Row Address Strobe,行地址選通脈沖;

CAS:Column Address Strobe,列地址選通脈沖;

tRCD: RAS to CAS Delay,RAS至CAS延遲;

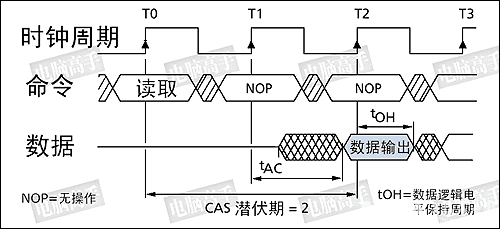

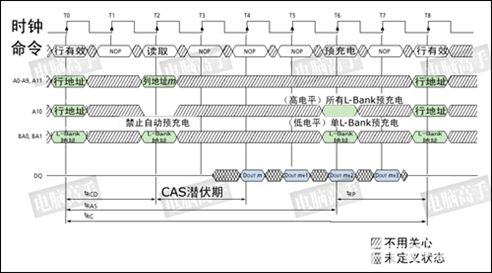

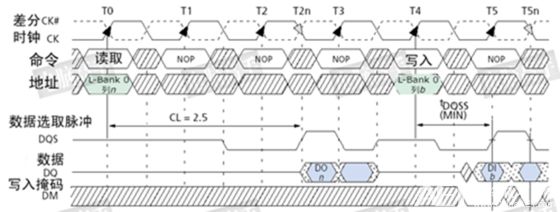

CL: CAS Latency,CAS潛伏期(又稱讀取潛伏期),從CAS與讀取命令發出到第一筆數據輸出的時間段;

RL:Read Latency,讀取潛伏期;

tAC: Access Time from CLK,時鐘觸發后的訪問時間,從數據I/O總線上有數據輸出之前的一個時鐘上升沿開始到數據傳到I/O總線上止的這段時間;

tWR: Write Recovery Time,寫回,保證數據的可靠寫入而留出足夠的寫入/校正時間,被用來表明對同一個bank的最后有效操作到預充電命令之間的時間量;

BL: Burst Lengths,突發長度,突發是指在同一行中相鄰的存儲單元連續進行數據傳輸的方式,連續傳輸所涉及到存儲單元(列)的數量就是突發長度(SDRAM),在DDR SDRAM中指連續傳輸的周期數;

Precharge:L-Bank關閉現有工作行,準備打開新行的操作;

tRP:Precharge command period,預充電有效周期,在發出預充電命令之后,要經過一段時間才能允許發送RAS行有效命令打開新的工作行;

AL:Additive Latency,附加潛伏期(DDR2);

WL:Write Latency,寫入命令發出到第一筆數據輸入的潛伏期;

tRAS: Active to Precharge Command,行有效至預充電命令間隔周期;

tDQSS: WRITE Command to the first corresponding rising edge of DQS,DQS相對于寫入命令的延遲時間;

邏輯Bank

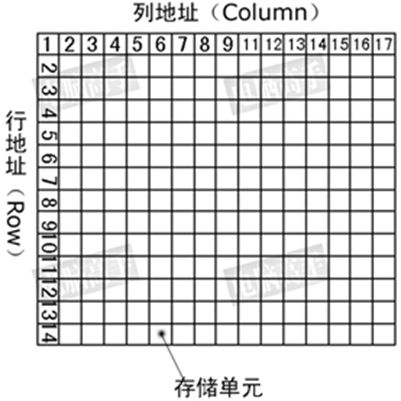

SDRAM的內部是一個存儲陣列,要想準確地找到所需的存儲單元就先指定一個(row),再指定一個列(Column),這就是內存芯片尋址的基本原理。

芯片位寬

SDRAM內存芯片一次傳輸率的數據量就是芯片位寬,那么這個存儲單元的容量就是芯片的位寬(也是L-Bank的位寬);

存儲單元數量=行數*列數(得到一個L-Bank的存儲單元數量)*L-Bank的數量也可用M*W的方式表示芯片的容量,M是該芯片中存儲單元的總數,單位是兆(英文簡寫M,精確值是1048576),W代表每個存儲單元的容量,也就是SDRAM芯片的位寬,單位是bit;

DDR SDRAM內部存儲單元容量是芯片位寬(芯片I/O口位寬)的一倍;

DDR2 SDRAM內部存儲單元容量是芯片位寬的四倍;

DDR3 SDRAM內部存儲單元容量是芯片位寬的八倍;

DDR4 SDRAM內部存儲單元容量是芯片位寬的八倍。

-

SDRAM

+關注

關注

7文章

441瀏覽量

56127 -

DDR

+關注

關注

11文章

731瀏覽量

66527 -

內存芯片

+關注

關注

0文章

127瀏覽量

22414

原文標題:【博文連載】DDR掃盲——DDR中的名詞解析

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Allegro高速PCB設計DDR存儲器模塊布局布線設計思路解析

美國UL安全認證名詞術語解析

DDR2名詞解釋

離子二次電池名詞解析

筆記本名詞解析---3G、TD、WCDMA

基于FPGA的DDR3協議解析邏輯設計

DDR布線在PCB設計中的應用解析

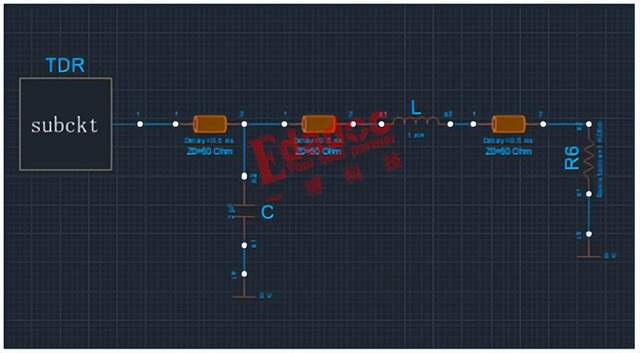

解析DDR設計中容性負載補償的作用

PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用

DDR中的名詞解析

DDR中的名詞解析

評論