低壓差線性穩(wěn)壓器(LDO)最大的優(yōu)點(diǎn)之一是它們能夠衰減開關(guān)模式電源產(chǎn)生的電壓紋波。這對(duì)鎖相環(huán)(PLL)和時(shí)鐘等信號(hào)調(diào)節(jié)器件在內(nèi)的數(shù)據(jù)轉(zhuǎn)換器尤為重要,因?yàn)樵肼曤娫措妷簳?huì)影響性能。我的同事Xavier Ramus在博客中介紹了噪音對(duì)信號(hào)調(diào)節(jié)設(shè)備的不利影響:減少高速信號(hào)鏈電源問(wèn)題。然而,電源抑制比(PSRR)仍然通常被誤認(rèn)為單一的靜態(tài)值。在這篇文章中,我將嘗試說(shuō)明什么是PSRR以及影響它的變量有哪些。

什么是PSRR?

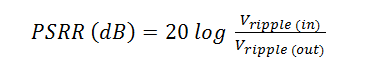

PSRR是許多LDO數(shù)據(jù)手冊(cè)中的公共技術(shù)要求。它規(guī)定了某個(gè)頻率的AC元件從輸入到LDO輸出的衰減程度。公式1表示PSRR為:

(1)

該等式告訴您衰減越高,每分貝的PSRR值越高。(應(yīng)該指出的是,一些供應(yīng)商會(huì)使用負(fù)號(hào)來(lái)表示衰減。大多數(shù)供應(yīng)商,包括德州儀器都不這樣用。)

在數(shù)據(jù)手冊(cè)的電氣特性表中找到頻率為120Hz或1kHz的PSRR并不罕見。但是,單獨(dú)使用此規(guī)范可能對(duì)確定指定LDO是否符合您的過(guò)濾要求沒(méi)有多大幫助。讓我們來(lái)看看為什么這么說(shuō)。

確定您的應(yīng)用程序的PSRR

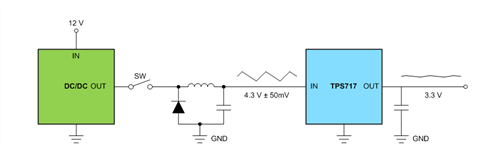

圖1展示了一個(gè)從12V電源軌調(diào)節(jié)4.3V的DC / DC轉(zhuǎn)換器,。其次是TPS717,一款高PSRR LDO,用于調(diào)節(jié)3.3V電源軌。在4.3V電源軌上,開關(guān)產(chǎn)生的紋波達(dá)到±50mV。LDO的PSRR將決定TPS717輸出端的紋波量。

圖1:使用LDO來(lái)過(guò)濾開關(guān)噪聲

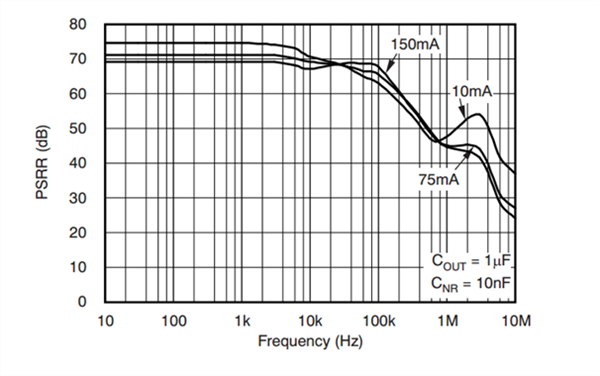

為了確定衰減程度,您必須首先知道波紋在哪個(gè)頻率出現(xiàn)。假設(shè)這個(gè)例子頻率為1MHz,因?yàn)樗锰幱诔S瞄_關(guān)頻率范圍的中間。您可以看到,指定為120Hz或1kHz的PSRR值無(wú)助于此分析。相反,您必須參考圖2中的PSRR圖。

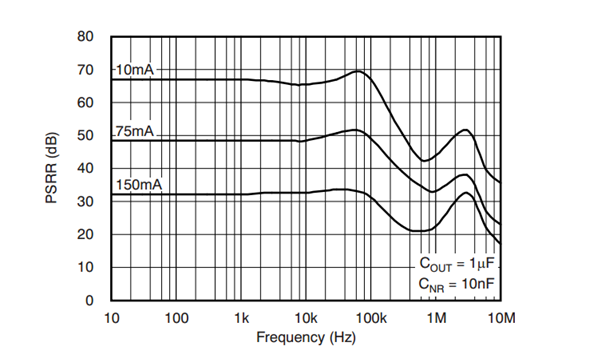

圖2:VIN- VOUT= 1V時(shí),TPS717的PSRR曲線

在下列條件下,1MHz時(shí)的PSRR指定為45dB:

-

IOUT= 150mA

-

VIN– VOUT= 1V

-

COUT= 1μF

假設(shè)這些條件符合你自己的條件。在這種情況下,45dB相當(dāng)于178的衰減系數(shù)。您可以預(yù)定輸入端的±50mV紋波在輸出端被壓縮至±281μV。

改變條件

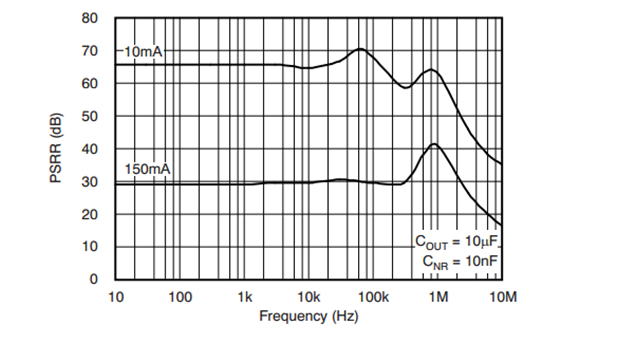

但假設(shè)您改變了條件,并決定將VIN- VOUTdelta降至250mV,以便更有效地進(jìn)行調(diào)節(jié)。然后您需要查看圖3中的曲線。

圖3:VIN - VOUT = 0.25V時(shí),TPS717的PSRR曲線

您可以看到,在所有其他條件保持不變的情況下,1MHz時(shí)的PSRR降至23dB,或者說(shuō)衰減系數(shù)為14。這是由于CMOS通道元件進(jìn)入三極管(或線性)區(qū)域; 也就是說(shuō),隨著VIN - VOUT三角接近壓差電壓,PSRR開始下降。(請(qǐng)記住,壓差電壓是關(guān)于輸出電流以及其他因素的函數(shù)。因此,較低的輸出電流會(huì)降低壓差并有助于提高PSRR。)

改變輸出電容也會(huì)有影響,如圖4所示。

圖4:VIN - VOUT = 0.25V,COUT =10μF時(shí),TPS717的PSRR曲線

將輸出電容從1μF增加到10μF,盡管VIN-VOUT增量保持在250mV,1MHz時(shí)的PSRR增加到了42dB。曲線中的高頻峰已經(jīng)向左移動(dòng)。這是由于輸出電容器的阻抗特性導(dǎo)致的。通過(guò)適當(dāng)調(diào)整輸出電容的大小,您可以調(diào)整或增加衰減,使之與特定的開關(guān)噪聲頻率一致。

轉(zhuǎn)動(dòng)所有旋鈕

只需調(diào)整VIN - VOUT和輸出電容,就可以改善特定應(yīng)用的PSRR。但這絕不是影響PSRR的唯一變量。表1展示了各種影響因素。

-

電容器

+關(guān)注

關(guān)注

64文章

6569瀏覽量

101990 -

PSRR

+關(guān)注

關(guān)注

0文章

216瀏覽量

39885 -

數(shù)據(jù)手冊(cè)

+關(guān)注

關(guān)注

95文章

6204瀏覽量

43534

發(fā)布評(píng)論請(qǐng)先 登錄

海洋儀器電源抑制比測(cè)試方案26800元起

開關(guān)電源的基礎(chǔ)知識(shí)題目及答案(免積分)

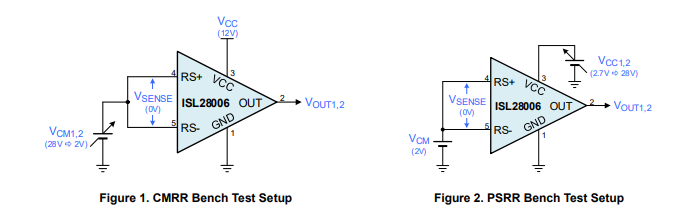

ISL28006:測(cè)量共模和電源抑制比

電源篇:想讓你的電路更穩(wěn)定、更高效嗎? LDO告訴你答案

LDO電路設(shè)計(jì)中的注意事項(xiàng) LDO和線性穩(wěn)壓器哪個(gè)更好

詳解LDO電路的電源抑制比

如何準(zhǔn)確計(jì)算電源引起的運(yùn)放輸出失調(diào)電壓?1200字搞定運(yùn)放電路選型之電源抑制比PSRR

LDO線性電源轉(zhuǎn)換芯片-LDO14005

電源多路復(fù)用器基礎(chǔ)知識(shí)

關(guān)于LDO基礎(chǔ)知識(shí):電源抑制比

關(guān)于LDO基礎(chǔ)知識(shí):電源抑制比

評(píng)論