和同學們一起交流程序定點化過程中的經驗,這對同學們的學習很有幫助。本堂課不講解具體的理論內容,而是從一個實際的文檔案例來說明定點化的復雜度和重要性。

定點化是程序走向實用的必經之路。

大多芯片都是在定點運算中發揮速度優勢。現在信號處理要求的實時性要求高,所以浮點程序定點化是必須完成的過程,還要保證性能幾乎沒有變化。

課程《數字信號處理》中有一章專門講這方面的知識,可見其有多重要。

先看看文檔內容吧!

1.設計與調試總結

1.1.有關verilog HDL

1.1.1.二進制補碼取反

既是雙目的減法運算符,也可演變為單目運算符得到原值的二進制補碼。

1.1.2.二維數組

假設對于一個位寬為wordsize,長度為memsize的二維數組由如下定義:

reg [wordsize-1:0] mem[memsize-1:0];

如果想單獨讀取二位數組中地址為addr的某個字,那么addr只能是模塊內部產生的變量,而不能是外部輸入。

1.1.3.帶符號移位操作符

使用verilog HDL語言中的帶符號移位運算符“>>>”和“<<<”時,需要設置變量為signed型,否則帶符號移位無效。

1.2.CIC經驗總結

1.2.1.CIC階數對下變頻器頻率響應的影響

實際測試表明5級的CIC濾波器的頻率響應性能大大好于3級CIC濾波器,由于1005#電臺有較嚴格的頻率響應指標,必須使用5級CIC濾波器。

1.2.2.CIC運算位寬的確定

CIC濾波器中由于存在積分單元,因此計算結果溢出在所難免。由于二進制補碼對數據的溢出能夠進行自動補償,所以如果數據采用補碼的形式進行運算,對積分器的溢出問題可以不用考慮。在多級CIC級聯的情況下,為了保證不至于因為寄存器溢出而導致的數據的丟失,需要對寄存器進行位數的擴展,這就涉及到寄存器最大長度的問題。

1.3.FIR經驗總結

1.3.1.FIR濾波器的設計

生成FIR濾波器的matlab語句為:

fir_coef = fir1(255,0.18,'low',chebwin(256,110));

使用窗函數法設計濾波器。

第一個參數是濾波器的階數。

第二個系數是截止頻率,這是一個介于0和1之間的數。假設實際截止頻率是F,采樣率是Fs,那么函數中第二個參數為 本文的FIR,截止頻率是電臺要求的3.2KHz,采樣率是36KHz。通過公式計算約為0.1778,因此設為0.18,即實際截止頻率比3.2KHz稍大。因為之后的DSP處理還有帶通濾波器,將會把上截止頻率嚴格限制在3.2KHz。但是該值也不可以太大,截止頻率越大,就會有更多的噪聲進入音頻信號,從而使電臺的靈敏度指標惡化。

第三個參數是濾波器類型,可以設為低通濾波器low,高通濾波器high和帶通濾波器bandpass。

第四個參數是窗函數的類型,默認為漢明(Hamming)窗,同樣還可以設計為KAISER或者切比雪夫窗。本文中的FIR采用切比雪夫窗。切比雪夫窗的使用方法是CHEBWIN(N+1,R),其中N是FIR的階數,R是帶外抑制度,單位是dB。帶外抑制越高,電臺的靈敏度和阻塞指標越好。

上述內容是一位研究生所寫,從文檔中可以看出理論知識即使學的好,也需要在實踐中去應用。知識只有應用了才能得到真正的提高和理解。

休息一下!

沒有定點化的過程,

就很難完成實際的產品。

學過DSP和FPGA的人自然能明白!

-

二進制

+關注

關注

2文章

804瀏覽量

42168 -

信號處理

+關注

關注

48文章

1055瀏覽量

103930 -

程序

+關注

關注

117文章

3824瀏覽量

82490

原文標題:數字信號處理之信號處理仿真 第三章 程序定點化(1)

文章出處:【微信號:gh_30373fc74387,微信公眾號:通信工程師專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB與PCBA工藝復雜度的量化評估與應用初探!

基于紋理復雜度的快速幀內預測算法

請問對12.918做無損定點化,最小位寬是多少?

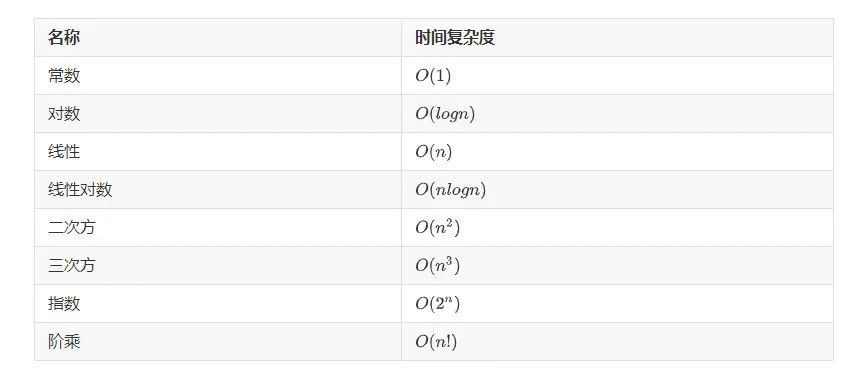

時間復雜度是指什么

本原LFSR序列的線性復雜度研究

設計復雜度攀升需要新的EDA工具來應對

浮點模型的定點化到產品級代碼的生成

圖像復雜度對信息隱藏性能影響分析

根據實例來介紹程序定點化的面目和定浮點轉換的概念詳細資料概述

根據實例來介紹程序定點化的復雜度和重要性

根據實例來介紹程序定點化的復雜度和重要性

評論