FPGA系統(tǒng)的復(fù)雜度越來(lái)越高,所以FPGA必須采用適當(dāng)?shù)?a target="_blank">電源管理技術(shù),來(lái)設(shè)計(jì)針對(duì)FPGA系統(tǒng)的電源。

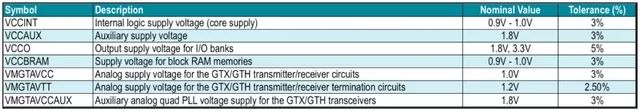

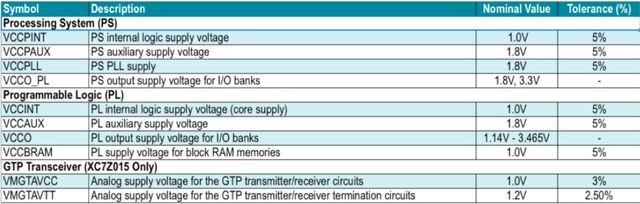

FPGA通常需要幾個(gè)電壓供電。根據(jù)應(yīng)用的不同,主輸入電源可以采用背板電源、隔離電源、非隔離電源,甚至是電池供電的方式。這些主輸入通常產(chǎn)生一個(gè)中間DC電壓來(lái)為FPGA的主電壓供電。這些中間電壓通常為5V或12V的DC電壓。表1和表2中列出了FPGA的某些典型電壓軌。

表1 Virtex 7FPGA的電源要求

表2 Zynq 7000系列片上系統(tǒng) (SoC) 的電源要求

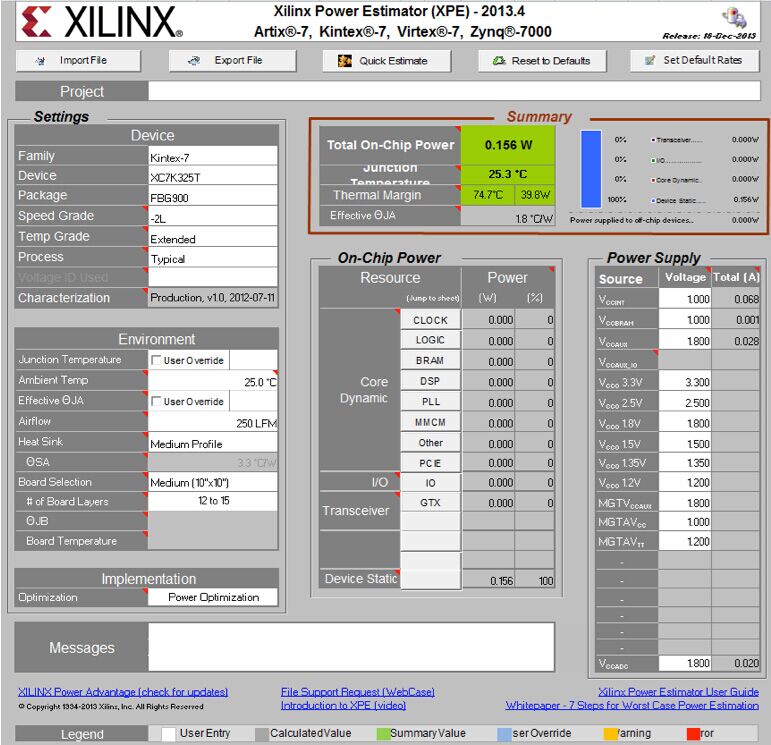

Xilinx功率估算器

為每個(gè)電壓確定合適的電流是一件比較棘手的工作,原因在于電流的范圍可以從幾百毫安到60A,甚至更高。如果事先進(jìn)行規(guī)劃的話,情況就會(huì)完全不同,事先規(guī)劃可以避免對(duì)電源的過(guò)度設(shè)計(jì)和設(shè)計(jì)的不充份,從而導(dǎo)致必須推倒重來(lái)等錯(cuò)誤。FPGA廠家提供了精確的FPGA功耗計(jì)算工具,可根據(jù)客戶對(duì)FPGA的使用方式來(lái)估算出最差情況下的功耗。

圖1中顯示的Xilinx功率估算器 (XPE),涵蓋了數(shù)個(gè)Xilinx FPGA系列。借助于這款工具,客戶可以選擇正在使用的部件,并且輸入時(shí)鐘和配置信息,來(lái)確定電源需求,并且根據(jù)估算值來(lái)選擇合適的器件。

圖1 Xilinx功率估算器 (XPE)

設(shè)計(jì)注意事項(xiàng)

注意事項(xiàng)1

在選擇一款符合FPGA應(yīng)用需要的電源時(shí),必須將很多因素考慮在內(nèi)。成本、尺寸,以及效率,始終是電源設(shè)計(jì)過(guò)程中需要注意的因素。不過(guò),在FPGA應(yīng)用中,某些電源將會(huì)有不同的要求。內(nèi)核電源通常需要在線路、負(fù)載和溫度范圍內(nèi)保持更加嚴(yán)格的精度。某些電源,比如說(shuō)收發(fā)器,對(duì)于噪聲更加敏感,并且需要將它們的輸出保持在特定的噪聲閥值以下。還需注意的是,某些具有共模電壓的電源可組合在一起,并且可以用一個(gè)鐵氧體磁珠進(jìn)行隔離,以實(shí)現(xiàn)濾波或作為一個(gè)負(fù)載開(kāi)關(guān)。

注意事項(xiàng)2

當(dāng)進(jìn)行符合容限要求方面的設(shè)計(jì)時(shí),需要將全部的靜態(tài)和動(dòng)態(tài)運(yùn)行條件考慮在內(nèi)。首先,選擇一款基準(zhǔn)精度小于1%的穩(wěn)壓器,這為客戶預(yù)留了最大的設(shè)計(jì)裕量空間來(lái)處理負(fù)載瞬變等動(dòng)態(tài)運(yùn)行條件。

注意事項(xiàng)3

在設(shè)計(jì)高速收發(fā)器電源時(shí)還需謹(jǐn)慎,因?yàn)檫@些靈敏電源輸出的噪聲會(huì)使性能下降,并且增加抖動(dòng)。低壓降穩(wěn)壓器 (LDO) 是這些電源軌的理想選擇。不過(guò),當(dāng)需要更高電流時(shí),只要輸出紋波的典型值在10kHz至80MHz頻率范圍內(nèi)保持在10mVpk-pk以下,就可以使用開(kāi)關(guān)電源。專用FPGA數(shù)據(jù)表將包含與收發(fā)器需求相關(guān)的詳細(xì)技術(shù)規(guī)格。

注意事項(xiàng)4

電源排序是FPGA電源設(shè)計(jì)時(shí)的另外一個(gè)重要方面。由于FPGA系統(tǒng)中需要多個(gè)電源供電,如圖推薦的電源順序在啟動(dòng)時(shí)汲取最小電流,這反過(guò)來(lái)防止了對(duì)器件的損壞。圖2中顯示的是針對(duì)Virtex 7系列FPGA上的邏輯電路和收發(fā)器電源的建議加電電源序列。針對(duì)Zynq 7000系列SoC的處理器排序顯示在圖3中。

圖2針對(duì)Virtex 7 FPGA的推薦加電序列

其中,VCCINT and VMGTAVCC可同時(shí)加電,只要它們?cè)赩MGTAVTT之前啟動(dòng),它們的加電順序可以互換。

圖3建議用于Zynq 7000系列SoC的加電序列

對(duì)于Xilinx 7/Zynq 7000系列器件來(lái)說(shuō),這些電源必須具有一個(gè)線性上升,并且必須在0.2ms至50ms的周期范圍內(nèi)加電,而對(duì)于Xilinx Ultrascale FPGA系列器件來(lái)說(shuō),這個(gè)周期范圍在0.2ms到40ms之間。建議斷電順序與加電順序相反。

電源解決方案

一旦已經(jīng)估算出合適的電流,并且全部設(shè)計(jì)注意事項(xiàng)已知的話,電源設(shè)計(jì)人員可以開(kāi)始器件選型。有幾個(gè)選項(xiàng)可供選擇,諸如低壓降穩(wěn)壓器 (LDO)、開(kāi)關(guān)模式電源 (SMPS) 和集成模塊,它們都具有不同的優(yōu)缺點(diǎn)。例如,由于其簡(jiǎn)單性和低輸出噪聲,LDO是某些較低電流FPGA電源的理想選擇。而LDO的缺點(diǎn)在于,它們的效率不高,并且會(huì)在較高電流時(shí),通過(guò)導(dǎo)通晶體管大量散熱。它們通常適用于那些功率較低的應(yīng)用,以及那些要求低噪聲的應(yīng)用。

當(dāng)需要的電流值大于2安培,并且效率更為重要的話,設(shè)計(jì)人員可以選擇開(kāi)關(guān)電源 (SMPS)。這些器件在單相位配置中的效率可以達(dá)到90%以上,并且提供高達(dá)30A的電流。與LDO相比,它們的設(shè)計(jì)工作復(fù)雜,并且在較輕負(fù)載時(shí)的效率不太高,不過(guò)它們更加靈活,并且在較高電流時(shí)的效率較高。

電源模塊,比如說(shuō)LMZ31506電源 (simple switcher),可以將一個(gè)DC/DC轉(zhuǎn)換器、功率金屬氧化物場(chǎng)效應(yīng)晶體管 (MOSFET)、一個(gè)屏蔽電感器,和無(wú)源組件集成在一個(gè)薄型四方扁平無(wú)引線 (QFN) 封裝內(nèi)。由于全部組件已經(jīng)集成在一個(gè)封裝內(nèi),并且僅需最少的外部組件,這樣可以減少設(shè)計(jì)時(shí)間。

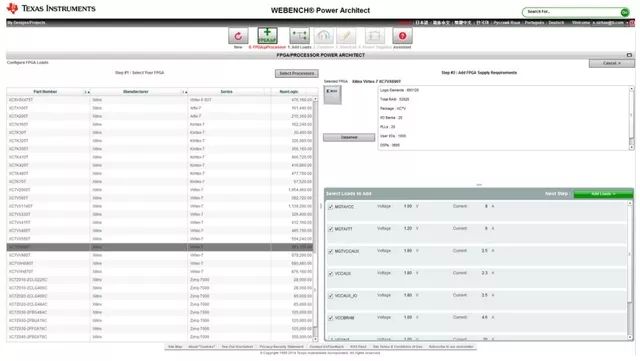

Webench FPGA架構(gòu)設(shè)計(jì)工具

Webench FPGA架構(gòu)設(shè)計(jì)工具(圖4)是一款十分有用的工具,能夠幫助電源設(shè)計(jì)人員在幾分鐘內(nèi)構(gòu)建多個(gè)FPGA電源輸出。這個(gè)工具包含新上市的FPGA的詳細(xì)電源需求。在這款工具中,你只需選擇正在使用的FPGA,并且將電流調(diào)整到需要的水平上,而這款工具將自動(dòng)形成一份綜合性的設(shè)計(jì)報(bào)告。

圖4 Webench FPGA架構(gòu)設(shè)計(jì)工具

-

FPGA

+關(guān)注

關(guān)注

1646文章

22054瀏覽量

618801 -

電源管理

+關(guān)注

關(guān)注

117文章

6440瀏覽量

146164 -

Xilinx

+關(guān)注

關(guān)注

73文章

2185瀏覽量

125433

原文標(biāo)題:FPGA電源設(shè)計(jì)指南

文章出處:【微信號(hào):gh_873435264fd4,微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA電源簡(jiǎn)介

FPGA電源設(shè)計(jì)的幾個(gè)基本步驟

如何測(cè)試FPGA的供電電源

FPGA應(yīng)用的電源模塊的選擇案例

FPGA電源系統(tǒng)設(shè)計(jì)

如何來(lái)選擇合適電源逆變器的隔離架構(gòu)

大規(guī)模現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)開(kāi)發(fā)系統(tǒng)電源設(shè)計(jì)研究

基于Virtex24 FPGA的圖像融合系統(tǒng)

適用于 FPGA、GPU 和 ASIC 系統(tǒng)的電源管理

基于FPGA的三相變頻電源系統(tǒng)設(shè)計(jì)

如何來(lái)設(shè)計(jì)針對(duì)FPGA系統(tǒng)電源

如何來(lái)設(shè)計(jì)針對(duì)FPGA系統(tǒng)電源

評(píng)論