說明:B.4版的Wishbone手冊本節(jié)內(nèi)容寫的比較繁瑣,因此沒有像前文一樣繼續(xù)翻譯。

數(shù)據(jù)組織是指數(shù)據(jù)的傳送順序。目前常見的32為處理器的數(shù)據(jù)總線粒度為1字節(jié),在傳送時,一個32位數(shù)據(jù)的最高字節(jié)可以放在數(shù)據(jù)總線的最低8位傳送,也可以放在數(shù)據(jù)總線的最高8位傳送,因此出現(xiàn)了大端和小端兩種數(shù)據(jù)組織方法。大端是指一個數(shù)據(jù)的最高位放在數(shù)據(jù)總線的最低位傳送或者放在地址較小的存儲器位置存儲;小端是指一個數(shù)據(jù)的最高位放在數(shù)據(jù)總線的最高位傳送或者放在地址較高的存儲器位置存儲。Wishbone同時支持大端和小端兩者數(shù)據(jù)組織方式。當數(shù)據(jù)總線的粒度和寬度相同時,大端和小端是一樣的。

大端模式

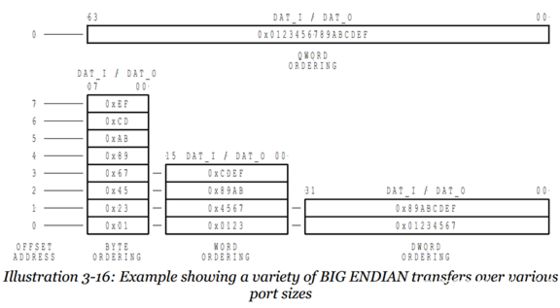

所謂的大端模式(Big-endian),是指數(shù)據(jù)的高字節(jié),保存在內(nèi)存的低地址中,而數(shù)據(jù)的低字節(jié),保存在內(nèi)存的高地址中,這樣的存儲模式有點兒類似于把數(shù)據(jù)當作字符串順序處理:地址由小向大增加,而數(shù)據(jù)從高位往低位放;

例子:

|

0000430: e684 6c4e 0100 1800 53ef 0100 0100 0000 0000440: b484 6c4e 004e ed00 0000 0000 0100 0000 |

在大端模式下,前32位應(yīng)該這樣讀: e6 84 6c 4e ( 假設(shè)int占4個字節(jié))

記憶方法: 地址的增長順序與值的增長順序相反

圖20 一個大端的例子

小端模式

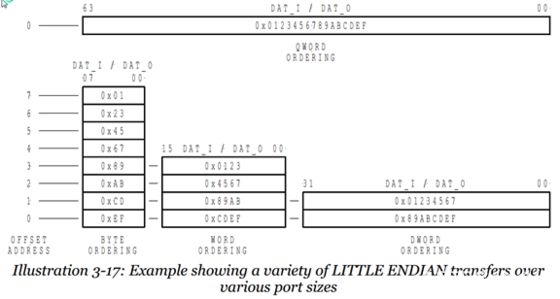

所謂的小端模式(Little-endian),是指數(shù)據(jù)的高字節(jié)保存在內(nèi)存的高地址中,而數(shù)據(jù)的低字節(jié)保存在內(nèi)存的低地址中,這種存儲模式將地址的高低和數(shù)據(jù)位權(quán)有效地結(jié)合起來,高地址部分權(quán)值高,低地址部分權(quán)值低,和我們的邏輯方法一致。

例子:

|

0000430: e684 6c4e 0100 1800 53ef 0100 0100 0000 0000440: b484 6c4e 004e ed00 0000 0000 0100 0000 |

在小端模式下,前32位應(yīng)該這樣讀: 4e 6c 84 e6( 假設(shè)int占4個字節(jié))

記憶方法: 地址的增長順序與值的增長順序相同

圖21 一個小端的例子

現(xiàn)狀

目前Intel的80x86系列芯片是唯一還在堅持使用小端的芯片,ARM芯片默認采用小端,但可以切換為大端;而MIPS等芯片要么采用全部大端的方式儲存,要么提供選項支持大端——可以在大小端之間切換。另外,對于大小端的處理也和編譯器的實現(xiàn)有關(guān),在C語言中,默認是小端(但在一些對于單片機的實現(xiàn)中卻是基于大端,比如Keil 51C),Java是平臺無關(guān)的,默認是大端。在網(wǎng)絡(luò)上傳輸數(shù)據(jù)普遍采用的都是大端。[

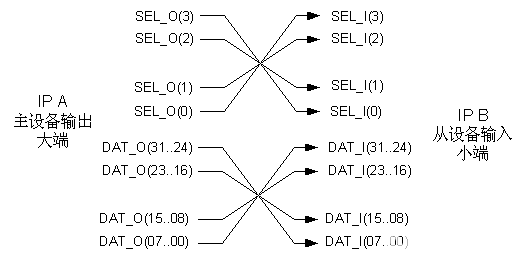

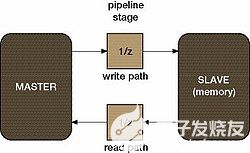

這兩者數(shù)據(jù)組織方式在一般文獻中都可以找到。總線標準只定義接口的通信協(xié)議,而數(shù)據(jù)的組織本質(zhì)上取決于主設(shè)備和從設(shè)備的設(shè)計。有時需要將大端和小端的接口互聯(lián)起來,圖22給出了將數(shù)據(jù)組織為大端的IP A和數(shù)據(jù)組織為大端的IP B相連的情形。IP A和IP B的數(shù)據(jù)總線寬度都是32為,粒度為8位。

圖22 大端和小端的接口互聯(lián)

-

存儲器

+關(guān)注

關(guān)注

38文章

7637瀏覽量

166531 -

數(shù)據(jù)總線

+關(guān)注

關(guān)注

2文章

62瀏覽量

17843

發(fā)布評論請先 登錄

wishbone總線

基于WISHBONE總線的FLASH閃存接口設(shè)計

基于Wishbone片上總線的IP核的互聯(lián)

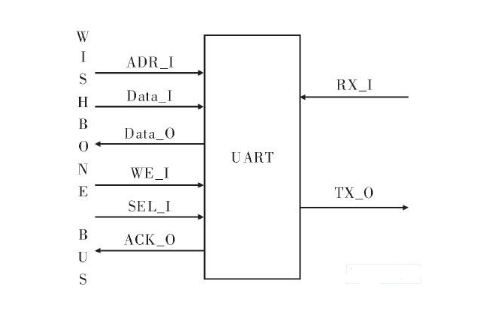

基于Wishbone總線的UART IP核設(shè)計

基于WISHBONE總線的FLASH閃存接口設(shè)計

基于WISHBONE總線的通用接口控制器

Wishbone總線實現(xiàn)UART IP核設(shè)計

基于FPGA的SDX總線與Wishbone總線接口設(shè)計

基于AMBA與WISHBONE的SoC總線橋KBar控制器的設(shè)計

Wishbone一般總線規(guī)范的共同特點

Wishbone總線周期之復(fù)位操作

Wishbone總線的異步周期結(jié)束路徑

一個簡單的Wishbone從設(shè)備的RTL代碼

Wishbone總線的主要特征概括

Wishbone II交易總線:速度的另一個等級

Wishbone總線周期之數(shù)據(jù)組織

Wishbone總線周期之數(shù)據(jù)組織

評論