大家好,又到了每日學習的時間了,今天我們來聊一聊基于fpga設計9/7小波變換原理。

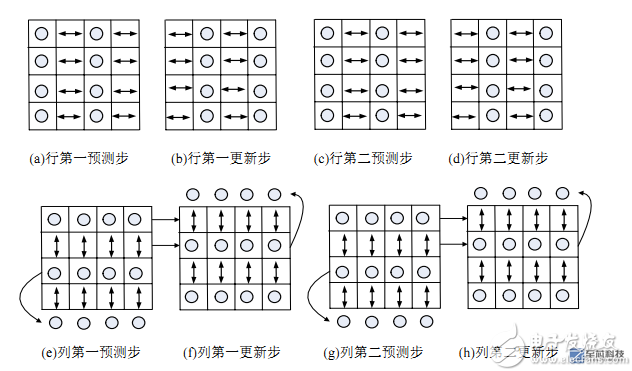

9/7小波變換包括行變換,列變換。

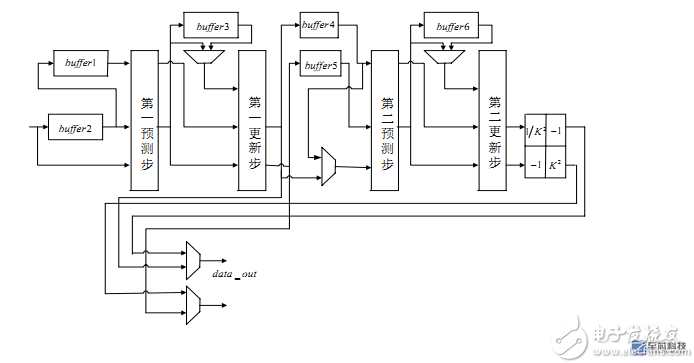

期中行變換包括第一步行變換,第一步行更新,第二步行變換,第二步行更新。

列變換包括第一步列變換,第一步列更新,第二步列變換,第二步列更新。

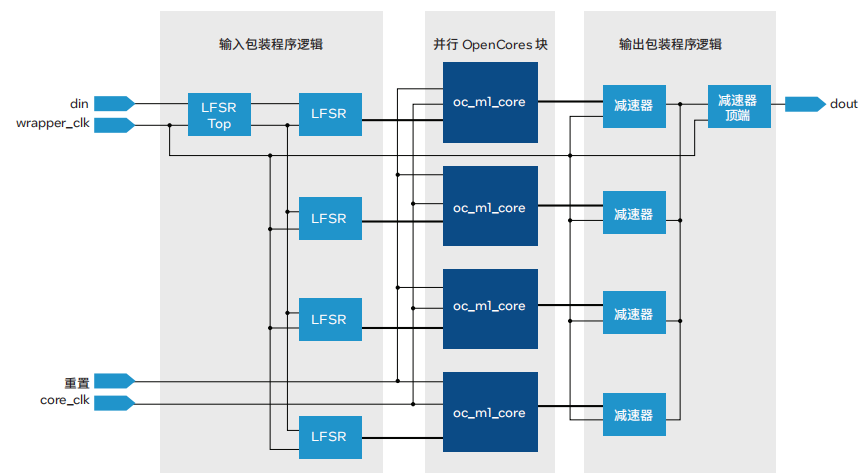

期中第二步行更新后要進行列變換,在這里要進行串行轉并行。

最后解交織部分是把低頻信息放在一起,高頻信息放在一起。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1644文章

21989瀏覽量

615214

發布評論請先 登錄

相關推薦

熱點推薦

Altera Stratix 10和Agilex 7 FPGA的電源管理及配置問題案例

本文主要基于 Altera Stratix 10 和 Agilex 7 FPGA 在客戶實際應用中遇到的電源管理及配置問題,系統梳理了典型故障案例、解決方案與調試建議。

Altera Agilex 7 M系列FPGA正式量產出貨

近日,全球 FPGA 創新技術領導者 Altera 宣布, Agilex 7 M 系列 FPGA 正式量產出貨,這是現階段業界領先的集成高帶寬存儲器,并支持 DDR5 和 LPDDR5 存儲器技術

進群免費領FPGA學習資料!數字信號處理、傅里葉變換與FPGA開發等

進群免費領FPGA學習資料啦!小編整理了數字信號處理、傅里葉變換與FPGA開發等FPGA必看資料,需要的小伙伴可以加小助手(微信:elecfans123)或進 QQ 群:9135011

發表于 04-07 16:41

無橋PFC變換器綜述

]回顧單級PFC變換器拓撲的解決方案,文獻[6]回顧了基于高頻隔離變換器的單相PFC變換器拓撲的實現方案,文獻[7]對提高電能質量的AC-DC變換

發表于 03-13 13:50

開發一款通過心電信號同步6路PPG脈搏波信號同步采集,遇到的幾個技術問題求解

采用集成模塊方案,比如模擬前端AFE4405和ADS1293,模擬前端總共7通道SPI,后處理器的通信采用片選還是用FPGA做7個SPI接口,

目前主要擔心點是SPI片選會影響數據同步采集。

3、如果

發表于 12-26 07:11

傅立葉變換的基本概念 傅立葉變換在信號處理中的應用

和離散傅里葉變換。 傅里葉變換的核心思想是將一個復雜的信號或函數表示為多個不同頻率的正弦波和余弦波的疊加。這樣,原本在時域或空間域中難以分析的復雜信號,就可以在頻域中清晰地看到其組成的

5CGTFD7D5F27C7N Intel/Altera可編程邏輯器件(CPLD/FPGA)

Altera 的Cyclone? V系列FPGA,型號5CGTFD7D5F27C7N,一篇文章帶你解讀,該型號的基本屬性。

傅里葉變換與圖像處理技術的區別

)轉換到頻域的數學工具。它基于傅里葉級數的概念,即任何周期函數都可以表示為不同頻率的正弦波和余弦波的疊加。對于非周期信號,傅里葉變換提供了一種將信號分解為不同頻率成分的方法。 在圖像處理中,傅里葉

基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡

板卡基于6U VPX標準結構,包含一個XCVU9P 高性能FPGA,一片XCZU7EV FPGA,用于 IO擴展接口,雙路HPC FMC擴展高速AD、DA、光纖接口等。是理想應用于高性

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成塊,支持8.0Gb/s數據速率的PCI Express 3.0。本文介紹了7系列FPGA PCIe Gen3的應用接口及

電源變換電路

1、輸出端Vo在2~9V之間連續可調或步進可調。(20分)

2、在Vo=5V時,負載電流不小于500mA。(20分)

3、在Vo=5V,Io=500mA時,電源變換電路的效率不低于40%。(20分

發表于 09-28 11:00

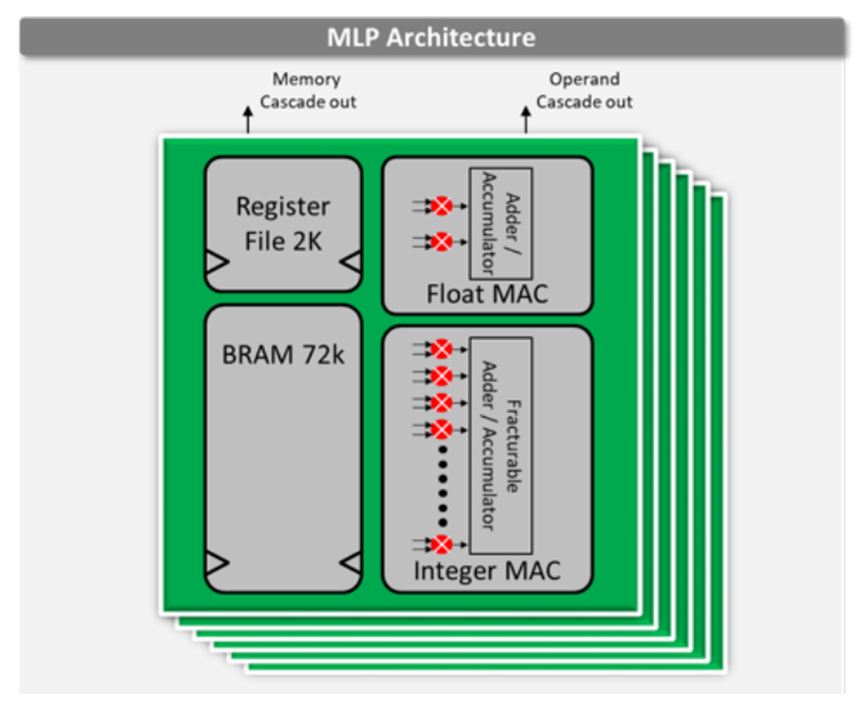

基于Achronix Speedster7t FPGA器件的AI基準測試

Achronix半導體公司推出了為AI優化的Speedster7t系列FPGA芯片,該系列包含專門針對AI工作負載的強化計算引擎。隨著AI在各個領域變得普遍,在FPGA芯片上部署AI應用的需求促使了

談一談FPGA設計中的功率計算

隨著工藝技術的越來越前沿化, FPGA器件擁有更多的邏輯、存儲器和特殊功能,如存儲器接口、 DSP塊和多種高速SERDES信道,這些發展不斷地對系統功率要求提出挑戰。

功率計算的關鍵是兩方面:靜態

發表于 07-31 22:37

簡談基于fpga設計9/7小波變換原理

簡談基于fpga設計9/7小波變換原理

評論