靜電放電(ESD)現(xiàn)象從一開始就存在。我們第一次接觸ESD往往是在孩童時(shí)代,在干燥的冬日觸碰金屬門把手時(shí),會有種觸電的感覺——這就是靜電放電。這種短暫的不適感通常對人類來說不是問題,但是即使是少量的ESD也有可能會損毀敏感電路。

手機(jī)設(shè)計(jì)人員一直都面臨著何時(shí)以及如何解決這一自然現(xiàn)象的挑戰(zhàn)。系統(tǒng)級ESD保護(hù)為何如此重要?怎樣提高移動設(shè)備中系統(tǒng)級ESD保護(hù)的測試模型和戰(zhàn)略?

1ESD模型和波形的測試

人體和衣服一天可存儲500 V至2,500 V靜電電荷,但是人類只能感受到3,000至4,000 V的ESD脈沖。這遠(yuǎn)高于電子電路受損的水平,即使人類無法檢測到。

設(shè)計(jì)人員必須從多方面解決ESD問題,對組件制造商來說,是在其設(shè)計(jì)階段和設(shè)計(jì)工作結(jié)束之時(shí)。簡而言之,ESD保護(hù)需要一種多層面方案。

通常,集成電路(IC)制造商按照ESD行業(yè)標(biāo)準(zhǔn)設(shè)計(jì)、測試和驗(yàn)證其IC。這可防止在IC生產(chǎn)或在PC板上組裝時(shí)出現(xiàn)物理損壞。針對ESD,通常進(jìn)行的兩種測試包括:

人體模型(HBM)。這種測試模擬人體通過接觸IC釋放所積累的靜電的ESD事件。采用一個(gè)帶電的100 pF電容和一個(gè)1.5 k?放電電阻進(jìn)行模擬。

帶電設(shè)備模型(CDM)。這種測試模擬在生產(chǎn)設(shè)備和工藝中發(fā)生的充電和放電事件。設(shè)備在一些摩擦工藝中或靜電感應(yīng)過程中獲得電荷,然后突然接觸到一個(gè)接地物體或表面。

雖然設(shè)備級測試有助于衡量IC的ESD穩(wěn)健性,但系統(tǒng)級測試可衡量現(xiàn)場的電子設(shè)備保護(hù)(即原始設(shè)備制造商[OEM]設(shè)備或終端產(chǎn)品)。

為了更好地了解最終產(chǎn)品所需的ESD保護(hù),OEM應(yīng)采用系統(tǒng)級ESD方法進(jìn)行設(shè)計(jì),然后按照國際電工委員會(IEC)ESD標(biāo)準(zhǔn)61000-4-2測試最終產(chǎn)品。IEC 61000-4-2被視為終端產(chǎn)品ESD測試和評級的行業(yè)標(biāo)準(zhǔn)。該測試可確定系統(tǒng)對現(xiàn)場外部ESD事件的易損性。

下圖比較了三種脈沖的能量和峰值電流:

系統(tǒng)級IEC 61000-4-2

設(shè)備級HBM

設(shè)備級CDM

IEC ESD事件脈沖顯然更強(qiáng),因此系統(tǒng)中的設(shè)備更加難以通過。盡管設(shè)備級測試(HBM和CDM)比較有用,且可提供ESD穩(wěn)健性的基準(zhǔn),但在系統(tǒng)級IEC測試期間并不總是能夠確定生存性。

為進(jìn)一步展示這一概念,下表顯示了組件測試和系統(tǒng)級IEC測試之間的差異。大家可以看到,差異很大,系統(tǒng)應(yīng)力水平更高。總而言之:較之于設(shè)備級設(shè)計(jì),系統(tǒng)設(shè)計(jì)必須滿足更嚴(yán)苛的要求。

2測試不充分的問題

在開發(fā)階段進(jìn)行系統(tǒng)級ESD測試可能會是個(gè)問題。例如,測試評估/不完整板組件上的ESD并不能代表所有情況。這些組件的結(jié)果并不保證完整系統(tǒng)的最終結(jié)果。

設(shè)備級ESD測試(即HBM和CDM)旨在通過適當(dāng)?shù)腅SD控制在工廠生成適合分立式組件的可重復(fù)且可再現(xiàn)的結(jié)果。這就是所謂的ESD保護(hù)區(qū)(EPA)。然而,這些測試并不是為了解決現(xiàn)實(shí)世界中EPA范圍之外的全部產(chǎn)品級ESD事件。

3實(shí)現(xiàn)產(chǎn)品穩(wěn)健性的關(guān)鍵:系統(tǒng)級ESD

相反,ESD穩(wěn)健型系統(tǒng)設(shè)計(jì)的關(guān)鍵是要考慮ESD在系統(tǒng)中的影響。為了獲得系統(tǒng)級視角,設(shè)計(jì)人員必須了解并解決以下問題:

系統(tǒng)級應(yīng)力事件及其對整個(gè)產(chǎn)品的影響。設(shè)備級ESD測試結(jié)果只能為系統(tǒng)ESD設(shè)計(jì)提供非常少的信息,因?yàn)樗鼈儫o法反映電子設(shè)備在IEC ESD事件期間經(jīng)歷了什么。

系統(tǒng)中板級相互作用,以及在ESD應(yīng)力作用下與電子部件外部接觸的引腳瞬態(tài)行為。

高效的表征化方法(如組件級傳輸線路脈沖(TLP)數(shù)據(jù)),用于分析IC、板和系統(tǒng)的相互作用。

系統(tǒng)級ESD保護(hù)戰(zhàn)略取決于物理設(shè)計(jì)、產(chǎn)品要求和產(chǎn)品成本。

4最佳方法:系統(tǒng)高效ESD設(shè)計(jì)(SEED)

系統(tǒng)高效ESD設(shè)計(jì)(SEED)是一種系統(tǒng)級方法,考慮了系統(tǒng)中所有組件的瞬態(tài)響應(yīng)。SEED方法還包括對IC引腳上PC板外部端口施加的IEC應(yīng)力的物理影響。

SEED是一種實(shí)現(xiàn)板載和片上ESD保護(hù)的協(xié)同設(shè)計(jì)方法。利用SEED,您可以分析和實(shí)現(xiàn)系統(tǒng)級ESD穩(wěn)健性。該方法要求對ESD應(yīng)力事件期間外部ESD脈沖之間的相互作用、完整的系統(tǒng)級板設(shè)計(jì)以及設(shè)備引腳特性有一個(gè)全面的了解。

SEED方法是實(shí)現(xiàn)對稱且穩(wěn)健的系統(tǒng)級ESD保護(hù)的最佳方法。如下圖所示,SEED利用以下信息設(shè)計(jì)系統(tǒng)級ESD保護(hù):

準(zhǔn)靜態(tài)TLP電流電壓(I-V)曲線數(shù)據(jù)

瞬態(tài)模擬

S參數(shù)PC板數(shù)據(jù)

IC I-V電路測量

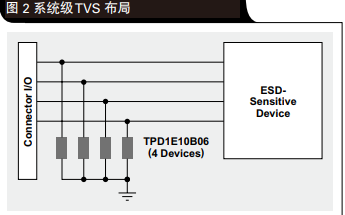

PC板的ESD保護(hù)為一級保護(hù),可防止對IC或系統(tǒng)造成物理損壞,片上保護(hù)發(fā)揮二級保護(hù)的作用。SEED的基本概念旨在防止具有損壞性質(zhì)的ESD脈沖抵達(dá)內(nèi)部IC引腳,通過執(zhí)行和分析ESD系統(tǒng)級模擬可實(shí)現(xiàn)適當(dāng)?shù)南到y(tǒng)級ESD設(shè)計(jì)。

眾所周知,在手機(jī)設(shè)計(jì)中戰(zhàn)略性地實(shí)現(xiàn)ESD至關(guān)重要,這樣做可縮短設(shè)計(jì)工程周期時(shí)間,減少ESD故障和研發(fā)開支。在后續(xù)的微信中,我們將深入探討ESD保護(hù)組件以及減少ESD對移動RF設(shè)計(jì)影響的不同戰(zhàn)略并解釋如何利用模擬和建模確定系統(tǒng)級ESD保護(hù)。

-

IC

+關(guān)注

關(guān)注

36文章

6102瀏覽量

178541 -

ESD保護(hù)

+關(guān)注

關(guān)注

0文章

450瀏覽量

27428 -

移動設(shè)備

+關(guān)注

關(guān)注

0文章

513瀏覽量

55131

原文標(biāo)題:告警!您的RF設(shè)備需要系統(tǒng)級ESD保護(hù)

文章出處:【微信號:Qorvo_Inc,微信公眾號:Qorvo半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

ESD保護(hù)策略解析

ESD保護(hù)界線新技術(shù)

USB2.0數(shù)據(jù)接口ESD保護(hù)

保護(hù)元件免受ESD的方法

板級ESD保護(hù)器件的關(guān)鍵屬性

ESD事件保護(hù)的系統(tǒng)級設(shè)計(jì)方法有哪幾種?

ESD保護(hù)時(shí)怎樣維持USB信號完整性

系統(tǒng)級ESD/EMI保護(hù)指南

TI:系統(tǒng)級 ESD 電路保護(hù)設(shè)計(jì)考慮因素

系統(tǒng)級ESD電路保護(hù)設(shè)計(jì)需要考慮因素?系統(tǒng)級和器件級的ESD有什么區(qū)別?

ESD的保護(hù)機(jī)理和主要測試模式有哪些?

ESD的3種模型和RF PA ESD保護(hù)方案介紹

系統(tǒng)級ESD保護(hù)為什么重要?怎樣提高ESD保護(hù)的測試模型和戰(zhàn)略?

系統(tǒng)級ESD保護(hù)為什么重要?怎樣提高ESD保護(hù)的測試模型和戰(zhàn)略?

評論