問:我購買了一個雙通道ADC,并配置成數字下變頻器。但現在有人說其實我有四個轉換器!!!難道是我買數據轉換器時沒留神參加了“買一贈一”活動?

答:自從第一枚單片式硅基模數轉換器(ADC)誕生以來,ADC技術一直緊跟硅加工技術快速發展的步伐。

這些年來,硅加工技術已發展到非常高的程度,現在已經能采用經濟的方式設計具有很多強大數字處理功能的ADC。早先的ADC設計使用的數字電路非常少,主要用于糾錯和數字驅動器。新一代GSPS(每秒千兆樣本)轉換器(也稱為RF采樣ADC)利用成熟的65 nm CMOS技術實現,可以集成許多數字處理功能來增強ADC的性能。當采樣速率(在GSPS范圍內)較高時,龐大的數據負載(每秒比特數)也隨之而來。就以AD9680為例,這是一款14位、1.25 GSP S/1GSPS/820 MSPS/500 MSPS JESD204B雙通道模數轉換器。在達到最高采樣速率1.25 GSPS時,ADC數據流為:

14 bits × 2 converter channels × 1.25 Gbps = 35 Gbps

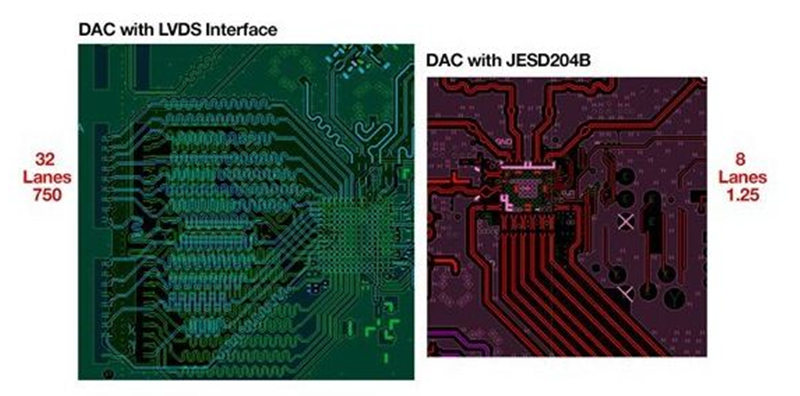

這樣的數據量將需要使用大量的LVDS路由通道來提取數字數據。為便于實現如此龐大的吞吐量,JESD204B標準應運而生。JESD204B是一種高速數據傳輸協議,采用8位/10位編碼和加擾技術,旨在確保足夠的信號完整性。針對JESD204B標準,總吞吐量變為

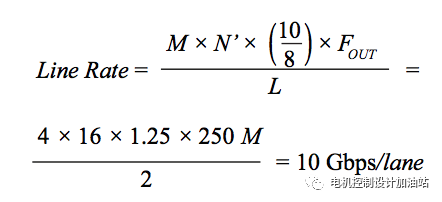

通過使用JESD204B標準,以每通道12.5 Gpbs對四個高速串行通道上的數據吞吐量進行劃分。將其與LVDS接口(其中線路速率電容約為1 Gbps/通道)比較,芯片可能需要超過28對!快速查閱AD9680數據手冊可以發現,就連設置鏈路都要面對一大堆字母組合。早先的LVDS ADC比較易于實現,而新一代JESD204B ADC則稍微復雜一些。如果考慮到內部數字下變頻器(DDC)的設置,則會更加復雜。盡管如此,ADC設置主要取決于三個字母:

L = 每條JESD204B鏈路的通道數M = 每條JESD204B鏈路的轉換器數F = 每條JESD204B鏈路中每幀數據的8位字節數

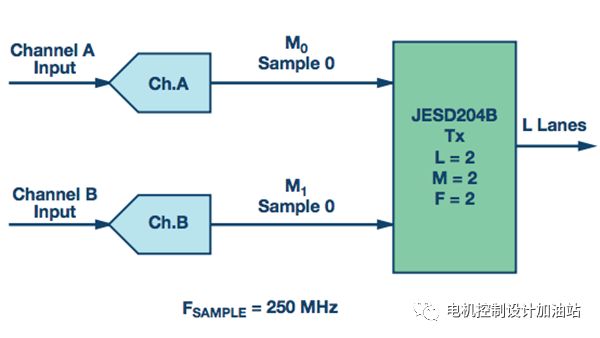

就以AD9250為例,這是一款14位、250 MSPS JESD204B雙通道模數轉換器。圖1顯示了AD9250采用默認設置的框圖。

圖1. 設置AD9250。

在此設置中,由于AD9250中沒有其他數字處理任務,所以JESD204B鏈路(JESD204B發射器)一目了然。對于JESD204B鏈路來說,通道A為轉換器“0”( M0 ),而通道B為轉換器“1”(M1),這就意味著“M”的值為2。此設置的總線路速率為

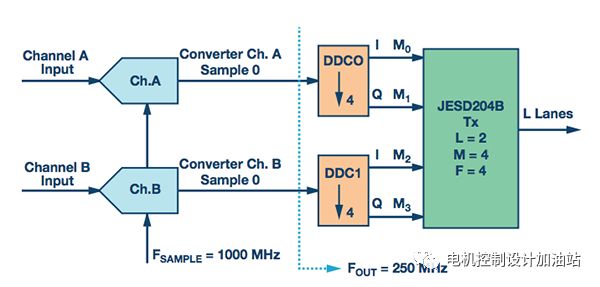

將其與采樣速率為1 GSPS的AD9680進行比較—在后面這種情況下,有兩個數字下變頻器(DDC)用于復數(I/Q)設置。圖2顯示AD9680使用數字下變頻器(DDC)對1 GSPS采樣數據進行4倍抽取。因此,輸出采樣速率(FOUT)為250 MSPS。

圖2. 設置AD9860-1000,兩個DDC設為4倍抽取。

從圖2中可以明顯看出,AD9680可以通過內部數字下變頻器(DDC)有效降低采樣速率。由于每個DDC輸出一個16位數據流,此時實際的(物理的)轉換器位流已與JESD204B字母湯中的“M”參數互不相干。依照標準,M為每條鏈路的轉換器數。

在修改后的情形中,“M”變成一個“虛擬”轉換器的參數。雖然從物理上看AD9680只有兩個ADC通道(A與B),但是當DDC啟用復數輸出模式后,就會有四個不同的(16位)數據流通向JESD204B接口。對于JESD204B接口來說,這就相當于此時有四個轉換器在發送位流。所以,“M = 4”或轉換器乘法發揮了作用。在這種情況下,輸出線路速率變為:

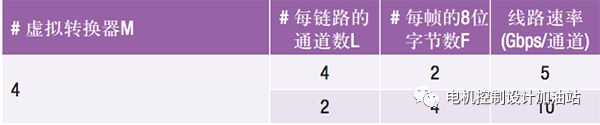

這里可以明顯看出AD9680 JESD204B接口的靈活性,因為其提供了兩個可用選項,具體取決于接收邏輯(ASIC或FPGA)對線路速率的可接受性。表1列出了圖2所示AD9680設置中JESD204B接口的可用選項。

表1. AD9680 ADC的JESD204B輸出接口配置選項

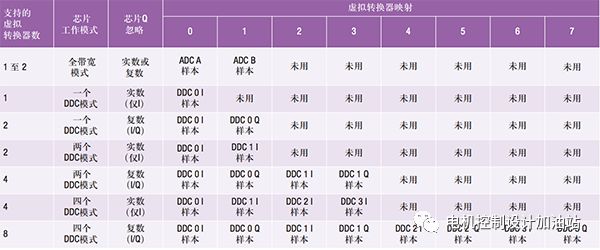

對于雙通道ADC(如集成四個DDC的AD9680),表2顯示了用于各種配置的虛擬轉換器映射。

表2. AD9680 ADC的JESD204B輸出接口配置選項

-

轉換器

+關注

關注

27文章

9001瀏覽量

151257 -

變頻器

+關注

關注

253文章

6834瀏覽量

149201 -

DDC

+關注

關注

2文章

95瀏覽量

37602

原文標題:說變就變!通過DDC魔法乘以ADC的虛擬通道數

文章出處:【微信號:motorcontrol365,微信公眾號:電機控制設計加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

JESD204B串行接口時鐘的優勢

FPGA高速數據采集設計之JESD204B接口應用場景

FPGA高速數據采集設計之JESD204B接口應用場景

JESD204B協議介紹

JESD204B的優勢

基于JESD204B高速數據傳輸協議 通過DDC魔法乘以ADC的虛擬通道數

JESD204B SystemC module 設計簡介(一)

JESD204B標準及演進歷程

JESD204B協議相關介紹與具體應用實例

JESD204B使用說明

為便于實現如此龐大的吞吐量,JESD204B標準應運而生

為便于實現如此龐大的吞吐量,JESD204B標準應運而生

評論