一,JESD204B應(yīng)用的優(yōu)缺點(diǎn)

接觸過FPGA高速數(shù)據(jù)采集設(shè)計(jì)的朋友,應(yīng)該會聽過新術(shù)語“JESD204B”。這是一種新型的基于高速SERDES的ADC/DAC數(shù)據(jù)傳輸接口。隨著ADC/DAC的采樣速率變得越來越高,數(shù)據(jù)的吞吐量越來越大,對于500MSPS以上的ADC/DAC,動(dòng)輒就是幾十個(gè)G的數(shù)據(jù)吞吐率,如果依舊采用傳統(tǒng)的CMOS和LVDS已經(jīng)很難滿足設(shè)計(jì)要求,因此“JESD204B”應(yīng)運(yùn)而生。現(xiàn)在各大廠商的高速ADC/DAC上基本都采用了這種接口。

與LVDS及CMOS接口相比,JESD204B數(shù)據(jù)轉(zhuǎn)換器串行接口標(biāo)準(zhǔn)可提供一些顯著的優(yōu)勢,比如更簡單的布局以及更少的引腳數(shù)。也因此它獲得了更多工程師的青睞和關(guān)注,它具備如下系統(tǒng)級優(yōu)勢:

1、更小的封裝尺寸與更低的封裝成本:JESD204B不僅采用8b10b編碼技術(shù)串行打包數(shù)據(jù),而且還有助于支持高達(dá)12.5Gbps的數(shù)據(jù)速率。顯著減少數(shù)據(jù)轉(zhuǎn)換器和FPGA上所需的引腳數(shù),從而可幫助縮小封裝尺寸,降低封裝成本;

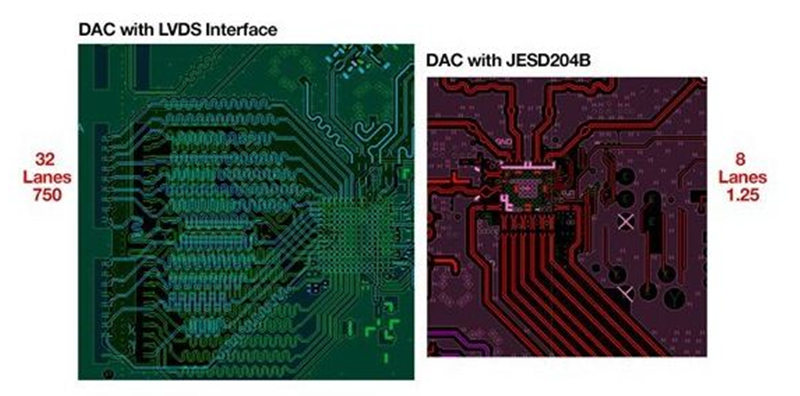

2、簡化的PCB布局與布線:更少的引腳數(shù)可顯著簡化PCB布局與布線,因?yàn)殡娐钒迳系穆窂礁佟S捎趯児芾淼男枨蠼档停虼瞬季趾筒季€可進(jìn)一步簡化。這是因?yàn)閿?shù)據(jù)時(shí)鐘嵌入在數(shù)據(jù)流中,并在接收器中與彈性緩沖器結(jié)合,無需通過“波形曲線”來匹配長度。下方圖片是JESD204B接口對簡化PCB布局有多大幫助的實(shí)例;

3、高靈活布局:JESD204B對畸變要求低,可實(shí)現(xiàn)更遠(yuǎn)的傳輸距離。這有助于將邏輯器件部署在距離數(shù)據(jù)轉(zhuǎn)換器更遠(yuǎn)的位置,以避免對靈敏模擬器件產(chǎn)生影響;

4、更簡單的時(shí)序控制;

5、滿足未來需求:該接口能夠自適應(yīng)不同數(shù)據(jù)轉(zhuǎn)換器分辨率。對于未來模數(shù)轉(zhuǎn)換器(ADC)及數(shù)模轉(zhuǎn)換器(DAC)而言,無需對TX/RX電路板進(jìn)行物理上的重新設(shè)計(jì)。

圖:LVDSDAC的PCB布局(左);采用JESD204B的相同DAC的PCB布局(右)

下表是JESD204B、LVDS接口之間的對比:

既然JESD204B接口的優(yōu)點(diǎn)如此多,這是不是意味著大家都要選取JESD204B接口了呢?

不一定。與LVDS接口相比,JESD204B的缺點(diǎn)是具有更長的絕對時(shí)延,這對于有些應(yīng)用來說是不可接受的。

盡管JESD204B可提供很多優(yōu)勢,但有些應(yīng)用要求極短的時(shí)延,最好是無時(shí)延。一個(gè)很好的實(shí)例是電子戰(zhàn)中使用的信號屏蔽器。該設(shè)備不僅要求絕對時(shí)延,而且需要最大限度地降低任何可能的延遲。

對于這種應(yīng)用,依舊應(yīng)該考慮使用LVDS接口,因此它沒有在JESD204B上進(jìn)行數(shù)據(jù)串行化的延遲。

二,JESD204B協(xié)議相關(guān)介紹

1、什么是JESD204B協(xié)議

該標(biāo)準(zhǔn)描述的是轉(zhuǎn)換器與其所連接的器件(一般為FPGA和ASIC)之間的數(shù)GB級串行數(shù)據(jù)鏈路,實(shí)質(zhì)上,具有高速并串轉(zhuǎn)換的作用。

2、使用JESD204B接口的原因

a.不用再使用數(shù)據(jù)接口時(shí)鐘(時(shí)鐘嵌入在比特流中,利用恢復(fù)時(shí)鐘技術(shù)CDR)

b.不用擔(dān)心信道偏移(信道對齊可修復(fù)此問題,RX端FIFO緩沖器)

c.不用再使用大量IO口,布線方便(高速串行解串器實(shí)現(xiàn)高吞吐量)

d.多片IC同步方便

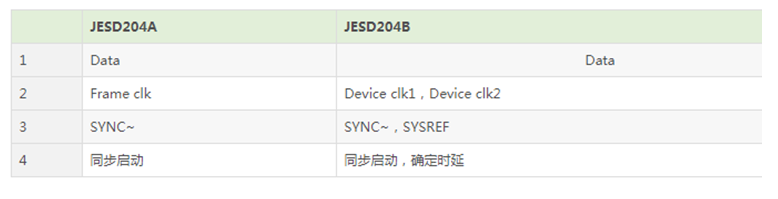

JESD204A和JESD204B參數(shù)對比如下圖所示:

3、關(guān)鍵變量

M:converters/device,轉(zhuǎn)換器(AD/DA)數(shù)量

L:lanes/device(link),通道數(shù)量

F:octets/frame(perlane),每幀的8位字節(jié)數(shù)

K:frames/multiframe,每個(gè)多幀的幀數(shù)

N:converterresolution,轉(zhuǎn)換器分辨率

N’:totalbits/sample,4的倍數(shù),N’=N+控制和偽數(shù)據(jù)位。

S:samples/converter/framecycle,每個(gè)轉(zhuǎn)換器每幀發(fā)送的樣本數(shù)。當(dāng)S=1時(shí),幀時(shí)鐘=采樣時(shí)鐘

CS:controlbits/sample

CF:controlwords/framecycle/device(link),通常只在HD=1時(shí)使用。

4、subclass0~2確定延遲

subclass0:不支持確定延遲;

subclass1:SYSREF,(AD9370支持的是子類1,IP核默認(rèn)也是子類1),利用確定延遲來對齊多片IC;

subclass2:SYNC~。

5、subclass1的三個(gè)階段

A、第一階段,代碼組同步(CGS)

a、RX將SYNC~引腳拉低,發(fā)出一個(gè)同步請求。

b、TX從下一個(gè)符號開始,發(fā)送未加擾的/K28.5/符號(每個(gè)符號10位)。

c、當(dāng)RX接收到至少4個(gè)無錯(cuò)誤的連續(xù)/K28.5/符號時(shí),RX同步,然后將SYNC~引腳拉高。

d、RX必須接收到至少4個(gè)無錯(cuò)誤8B/10B字符,否則同步將失敗,鏈路留在CGS階段。

e、CGS階段結(jié)束,ILAS階段開始。

注意:

a、串行數(shù)據(jù)傳輸沒有接口時(shí)鐘,因此RX必須將其數(shù)位及字邊界與TX串行輸出對齊。RX向TX發(fā)送~SYNC請求信號,讓其通過所有信道發(fā)送一個(gè)已知的重復(fù)比特序列K28.5。RX將移動(dòng)每個(gè)信道上的比特?cái)?shù)據(jù),直到找到4個(gè)連續(xù)的K28.5字符為止。此時(shí),它不僅將知道比特及字邊界,而且已經(jīng)實(shí)現(xiàn)了CGS。

b、RX~SYNC的輸出必須與RX的幀時(shí)鐘同步,同時(shí)要求TX的幀時(shí)鐘與~SYNC同步(可通過~SYNC復(fù)位TX的幀時(shí)鐘計(jì)數(shù)器來實(shí)現(xiàn))。

c、不能使用交流耦合。

B、第二階段,初始通道同步(ILAS):

a、在JESD204B中,發(fā)送模塊捕捉到SYNC~信號的變換,在下一個(gè)本地多幀(LMFC)邊界上啟動(dòng)ILAS。

b、ILAS主要對齊鏈路的所有通道,驗(yàn)證鏈路參數(shù),以及確定幀和多幀邊界在接收器的輸入數(shù)據(jù)流中的位置。

c、ILAS由4個(gè)多幀組成。每個(gè)多幀最后一個(gè)字符是多幀對齊字符/A,第一,三,四個(gè)多幀以/R字符開始,以/A字符結(jié)束。接收器以各通道的最后一個(gè)字符/A對齊接收器內(nèi)各通道內(nèi)各多幀的末尾。

d、這些特定的控制字符只用于初始通路對齊序列中,而不用在數(shù)據(jù)傳輸?shù)娜魏纹渌A段。CGS和ILAS階段不加擾。

e、RX模塊中的FIFO吸收信道偏移。

C、第三階段,數(shù)據(jù)傳輸階段:

沒有控制字符,獲取鏈路全帶寬。利用字符替換來監(jiān)視數(shù)據(jù)同步,多幀計(jì)數(shù)器LMFC。

6.Deviceclk

系統(tǒng)基準(zhǔn)時(shí)鐘,提供采樣時(shí)鐘,JESD204B時(shí)鐘,幀串行器時(shí)鐘。產(chǎn)生幀時(shí)鐘和多幀時(shí)鐘。器件時(shí)鐘用來捕捉SYSREF,并完成幀和多幀時(shí)鐘的前沿相位對齊。子類1中,多幀時(shí)鐘周期必須是器件時(shí)鐘的整數(shù)倍。ADC/DAC/FPGA可運(yùn)行于不同速率,但必須同源且頻率相關(guān)。

7、同步對齊過程

發(fā)送器和接收器各維護(hù)一個(gè)多幀計(jì)數(shù)器(LMFC),所有發(fā)送器和接收器連接到一個(gè)公共(源)SYSREF,這些器件利用SYSREF復(fù)位其LMFC,這樣所有LMFC應(yīng)互相同步(在一個(gè)時(shí)鐘周期內(nèi))。

SYSREFsignal(DeviceSubclass1):

a、確定時(shí)延(小于1個(gè)多幀時(shí)鐘周期)。

b、對齊和器件時(shí)鐘同源,LMFC周期的整數(shù)倍,在DeviceClk沿變化時(shí)采樣SYSREF信號,確定時(shí)延,對齊多幀和幀時(shí)鐘。SYSREF用于對齊所有收發(fā)器件LMFC相位。

SYNC~signal:

同步請求信號。接收端:與接收器幀時(shí)鐘同步。CGS后在接收端LMFC邊沿拉高。釋放SYNC(所有器件都會看到)后,發(fā)送器在下一次(TX)LMFC繞回0時(shí)開始ILAS。如果F*K設(shè)置適當(dāng),大于(發(fā)送器編碼時(shí)間)+(線路傳播時(shí)間)+(接收器解碼時(shí)間),則接收數(shù)據(jù)將在下一個(gè)LMFC之前從接收器的SERDES傳播出去。接收器將把數(shù)據(jù)送入FIFO,然后在下一個(gè)(RX)LMFC邊界開始輸出數(shù)據(jù)。發(fā)送器SERDES輸入與接收器FIFO輸出之間的已知關(guān)系稱為確定性延遲。

三,JESD204B具體應(yīng)用實(shí)例

1、相控陣?yán)走_(dá)下行同步采集技術(shù)應(yīng)用

多通道數(shù)據(jù)的同步采集是數(shù)字相控陣?yán)走_(dá)下行數(shù)據(jù)接收和處理要解決的關(guān)鍵問題。提出了支持JESD204B協(xié)議的模數(shù)轉(zhuǎn)換器和支持JESD204B協(xié)議的FPGA軟核相結(jié)合的設(shè)計(jì)方案。利用JESD204B協(xié)議的確定性延遲特性,只要保證通道間下行數(shù)據(jù)的相互延遲不超過一個(gè)多幀時(shí)鐘周期,通過關(guān)鍵控制信號的設(shè)計(jì)和處理,通道間可以實(shí)現(xiàn)數(shù)據(jù)的同步,有效控制板內(nèi)多片ADC之間進(jìn)行同步采樣,從而解決數(shù)字相控陣?yán)走_(dá)下行數(shù)據(jù)因采集帶來的相位一致性問題。

2、雷達(dá)多通道同步采集實(shí)現(xiàn)

該設(shè)計(jì)是一種軟硬件結(jié)合的簡化方案,通過合理設(shè)計(jì)硬件、設(shè)計(jì)SYSREF信號的扇出控制邏輯,在一定采樣率范圍內(nèi)滿足JESD204B協(xié)議ADC多片多通道之間采樣點(diǎn)相對時(shí)延固定,從而確保各通道采集信號相位一致。JESD204B協(xié)議支持的確定性延遲特性保證了設(shè)計(jì)實(shí)現(xiàn)。驗(yàn)證方案的測試電路采用Xilinx K7系列FPGA控制兩片AD9694(采樣率320Msps)同步采集,證實(shí)設(shè)計(jì)方案滿足應(yīng)用需求。

3、雷達(dá)視頻信號同步傳輸設(shè)計(jì)與實(shí)現(xiàn)

以寬帶測向接收機(jī)中多波束比幅測向?yàn)楸尘?設(shè)計(jì)了基于JESD204B協(xié)議的高速背板視頻信號同步傳輸方案。時(shí)鐘、JESD204B協(xié)議參數(shù)的設(shè)計(jì)合理,實(shí)現(xiàn)了2塊多通道視頻幅度采集板與1塊數(shù)據(jù)處理板之間線速率為6.25Gbps的高速同步傳輸,解決了多波束比幅測向前多通道視頻信號傳輸同步問題。

4、高速ADC應(yīng)用與研究

在成像設(shè)備、通信、雷達(dá)、工業(yè)儀器儀表等需要實(shí)時(shí)傳輸大量數(shù)據(jù)的行業(yè)中,要求其數(shù)模轉(zhuǎn)換器的采樣率越來越高、數(shù)據(jù)位越來越大、帶寬越來越寬、傳輸速率越來越快。這對高速數(shù)據(jù)采集傳輸系統(tǒng)提出了更高的要求。傳統(tǒng)的ADC大多使用并行總線進(jìn)行數(shù)據(jù)傳輸,隨著采樣率的提高,捕獲數(shù)據(jù)量的激增,并行總線的吞吐率需大大提升,這就要增加輸出數(shù)據(jù)線的位數(shù),而位數(shù)的增加需要占用大量的芯片管腳,使芯片和PCB的小型化難以實(shí)現(xiàn)并且在大量高速數(shù)據(jù)信號走線的同時(shí)控制電壓噪聲也是難以做到的。

與傳統(tǒng)的并行總線傳輸ADC相比,使用高速串行總線傳輸?shù)腁DC具有非常明顯的優(yōu)勢,其中所需的信號傳輸線大大減少,總線傳輸速率也明顯提升,并且在提高數(shù)據(jù)傳輸速率的同時(shí)節(jié)省了布線空間,同時(shí)也降低了芯片功耗。使用高速串行總線傳輸?shù)腁DC不僅在體積、功耗和數(shù)據(jù)傳輸速率都比并行總線傳輸?shù)腁DC更具優(yōu)勢。在高速數(shù)據(jù)采集傳輸系統(tǒng)中,串行總線傳輸?shù)腁DC已成為今后的發(fā)展趨勢。在研究了高速串行傳輸技術(shù)后,設(shè)計(jì)了基于JESD204B協(xié)議的串行總線技術(shù)的ADC,并設(shè)計(jì)了基于此協(xié)議的高速ADC采樣電路,該模數(shù)轉(zhuǎn)換芯片支持JESD204BSubclass1工作模式,通過FMC接口與高性能FPGA的GTH接口相連接收ADC采樣后的數(shù)據(jù),最終通過PCIE金手指與PC端進(jìn)行傳輸。

5、JESD204B協(xié)議中自同步加解擾電路設(shè)計(jì)與實(shí)現(xiàn)

作為JEDEC最新修訂的AD/DA串行傳輸協(xié)議,JESD204B采用自同步擾碼對數(shù)據(jù)鏈路層原始信號進(jìn)行隨機(jī)化轉(zhuǎn)換,有效地避免了雜散頻譜產(chǎn)生,減少了物理層誤碼概率.基于經(jīng)典狀態(tài)機(jī)結(jié)構(gòu)對JESD204B協(xié)議中自同步加擾及解擾電路進(jìn)行設(shè)計(jì)實(shí)現(xiàn),根據(jù)協(xié)議中自同步擾碼的原理細(xì)節(jié),提出了一種加擾與解擾狀態(tài)電路的設(shè)計(jì)方案,最終對該方案進(jìn)行實(shí)現(xiàn)、仿真與綜合.仿真與綜合結(jié)果表明該方案充分兼容協(xié)議控制信號,功能完全符合協(xié)議要求,增強(qiáng)了加解擾電路的穩(wěn)定性與容錯(cuò)性,同時(shí)提高了電路的處理效率,可應(yīng)用于JESD204B高速串行接口電路設(shè)計(jì)中。

以上就是關(guān)于JESD204B的應(yīng)用場景的介紹,明德?lián)P可承接基于JESD204B的高速數(shù)據(jù)傳輸項(xiàng)目,若想了解更多,可聯(lián)系。

-

FPGA

+關(guān)注

關(guān)注

1644文章

22009瀏覽量

616591 -

adc

+關(guān)注

關(guān)注

99文章

6671瀏覽量

548726 -

JESD204B

+關(guān)注

關(guān)注

6文章

82瀏覽量

19552

發(fā)布評論請先 登錄

JESD204B生存指南

LTC6953具有11個(gè)輸出并支持JESD204B/JESD204C協(xié)議的超低抖動(dòng)、4.5GHz時(shí)鐘分配器技術(shù)手冊

AD9680 JESD204B接口的不穩(wěn)定會導(dǎo)致較大的電流波動(dòng),怎么解決?

使用jesd204b IP核時(shí),無法完成綜合,找不到jesd204_0.v

JESD204B有專用于ADC/DAC和FPGA或ASIC的接口嗎?

JESD204B使用說明

調(diào)試ADS52J90板卡JESD204B接口遇到的問題求解

使用JESD204B接口,線速率怎么計(jì)算?

使用JESD204B如何對數(shù)據(jù)進(jìn)行組幀?

ADC16DX370 JESD204B串行鏈路的均衡優(yōu)化

AFE77xx DAC JESD204B調(diào)試

從JESD204B升級到JESD204C時(shí)的系統(tǒng)設(shè)計(jì)注意事項(xiàng)

AFE77 JESD204B 調(diào)試手冊

JESD204B協(xié)議相關(guān)介紹與具體應(yīng)用實(shí)例

JESD204B協(xié)議相關(guān)介紹與具體應(yīng)用實(shí)例

評論