基于0.35 μm Si CMOS 平面工藝制定了放大器單芯片集成的工藝流程。為了進一步降低放大器的噪聲系數,在制作放大器中SiGe 器件時,采用鈦硅合金(TiSi2)來減小晶體管基極電阻。由于沒有使用占片面積大的螺旋電感,最終研制出的SiGe HBT LNA 芯片面積僅為0.282 mm2。測試結果表明,在工作頻帶0.2-1.2 GHz 內,LNA 噪聲系數低至2.5 dB,增益高達26.7 dB,輸入輸出端口反射系數分別小于-7.4 dB 和-10 dB。

1 引言

低噪聲放大器(LNA)是射頻/微波通訊裝置中的核心組件,它位于接受機的前端,好的噪聲性能可以提高接受機的靈敏度和擴大動態范圍(SFDR)的上限,足夠的增益保障放大微弱的接收信號,因此要求放大器提供優異的噪聲和增益特性。

與混合集成LNA 相比,單片集成LNA 具有重復生產能力好、電路損耗少,結構緊湊和功耗低等一系列優點,可以大大縮小通訊設備的體積和成本。

從目前報道的有關單片集成LNA文獻來看,國內研制的LNA 性能較弱,仍處于起步階段,缺乏成熟的開發經驗,與國外存在一定差距;并且早期采用III-V 器件實現的較多,但是III-V 器件不能與成熟的Si 平面工藝兼容,不利于集成,導致成本高,而SiGe HBT 克服了這個缺點,不但具有高集成度和優越的性價比,還具有優良的頻率特性、增益特性和噪聲特性,因此SiGe HBT 非常適于作單片集成LNA 的有源器件。

本文采用SiGe HBT 研制出一款單片集成寬帶LNA,給出了放大器設計的基本思路,基于0.35 μmSi CMOS 平面工藝制定了放大器單芯片集成的工藝流程,并最終研制出一款SiGe HBT LNA。本研究結果對我國設計開發射頻/微波單片集成LNA,尤其對設計開發基于Si CMOS 工藝的單片集成LNA具有重要意義。

2 單片集成SiGe HBT LNA 的電路結構及設計

2.1 電路結構

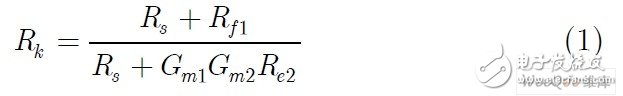

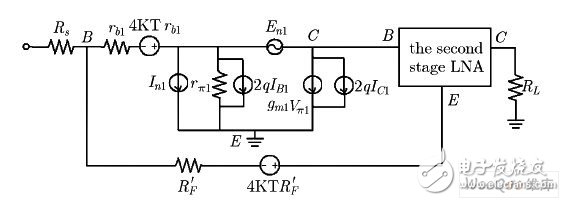

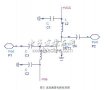

為了制作方便和減小芯片面積,本文設計的LNA 采用復合型電阻負反饋結構,沒有使用占片面積大的螺旋電感。圖1 是本文設計的SiGe HBTLNA的電路結構圖。圖中Q1,Q2和Q3是SiGe HBT,其中Q2 和Q3 構成一個達林頓對,可以提高LNA 的系統增益。系統并聯反饋電阻(Rf1 和Re3a),局部并聯反饋電阻(Rf2)和局部串聯反饋電阻(Re2 和Re3b)構成復合型負反饋結構。

圖1 采用復合型電阻反饋結構的SiGe HBT LNA 電路結構示意圖

2.2 端口匹配

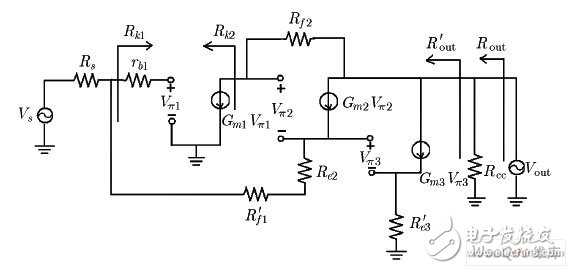

為了保障信號在整個射頻接收機中不失真的傳輸和降低信號傳輸能量的泄漏,LNA 需要具備良好的端口匹配。在本節中,將分析SiGe HBT LNA 的端口阻抗并進行優化。圖2 給出了圖1 中LNA 的交流等效電路。由于LNA 的信號傳輸能量泄漏主要發生在輸出端口,從圖中可以看出,從 Q1 輸出端看進去的輸出阻抗Rk 可表示為:

圖2 SiGe HBT LNA 的交流等效電路。

從Q3 輸出端看進去的輸出阻抗R'out 為:

式中GmD 是達林頓對的跨導。LNA 的輸出阻抗Rout可表示為:

在一定的偏置下,提供偏置電流的反饋電阻是定值,因此式(1)中的Rf1,式(2)-式(3)中的Rf2 和Rcc 是定值,并且LNA 中的3 個SiGe HBT 的跨導也是定值。分析式(3)可知,適當調整Re2,可改善Rout。圖3 給出了SiGe HBT LNA 的輸出阻抗Rout與Re2 的關系。從圖中可以看出,Rout 隨著Re2 的增大而增大,并且當Re2 為21Ω 時,Rout 達到50 Ω,LNA 輸出端口達到最佳匹配。

圖3 SiGe HBT LNA 的輸出阻抗Rout 與Re2 的關系

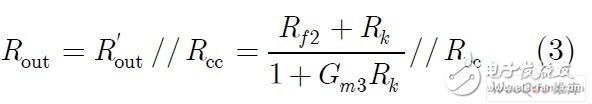

2.3 電路的噪聲特性

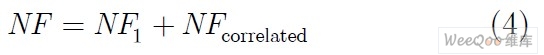

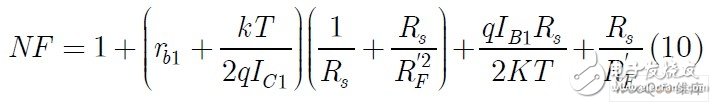

多級LNA 的噪聲性能主要決定于第1 級LNA的噪聲系數。考慮到本文設計的LNA 有多級反饋支路,因此分析系統噪聲系數還應該考慮反饋支路的噪聲。此時,放大器的系統噪聲系數可表示為:

其中NF1和NFcorrelated分別是第1 級放大器和反饋支路的噪聲系數。圖4 是SiGe HBT LNA 的小信號等效噪聲模型,其中rb1 是Q1 的基極電阻,En1 和In1分別是Q1 的等效噪聲電壓源和電流源。

圖4 SiGe HBT LNA 的小信號噪聲模型

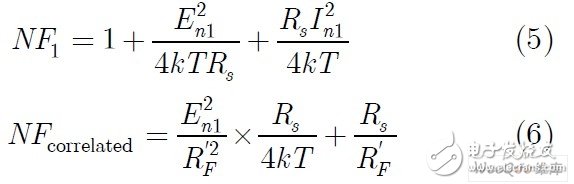

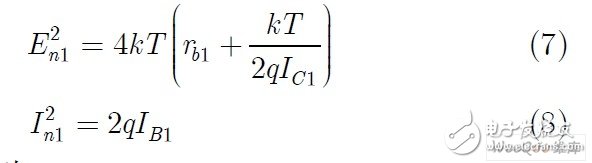

通過分析圖4 中等效噪聲模型, NF1 和NFcorrelated 可寫為:

其中k 是波爾茲曼常數,T 是室溫,En1 和In1 為:

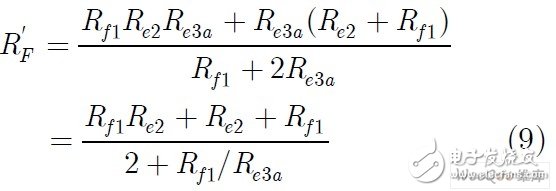

R‘F 可表示為:

式(7)和式(8)中,Rs 是系統源阻抗,在匹配良好時可認為是50 Ω,IC1 和IB1 分別為Q1 的集電極和基極電流。將式(5)-式(8)代入式(4),系統噪聲系數可表示為:

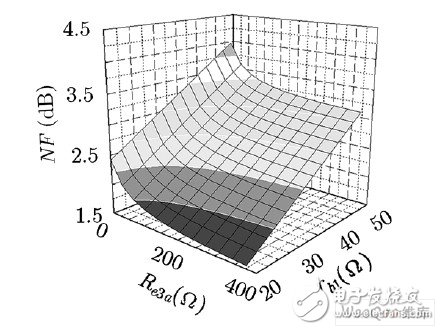

式中僅rb1 和R‘F 是變量,結合式(9)可知,在一定偏置下,提供Q1 基級電流的Rf1 是定值,同時由2.2節分析可知,獲得最佳輸出端口匹配時Re2 為21 Ω,因此rb1 和Re3a 是式(10)的自變量。圖5 為SiGe HBTLNA 的噪聲系數NF 隨rb1 和Re3a 的變化。可以看出,增大Re3a 可降低系統NF,考慮到Re3a 直接影響LNA 中Q3 的工作電壓,最終確定Re3a 為310Ω。

圖5 SiGe HBT LNA 的噪聲系數NF 與rb1、Re3a 的關系

另外,還可以通過減小rb1 降低噪聲系數,由于鈦硅合金(TiSi2)具有低電阻率以及良好的與硅材料吸附的能力,因此本文制作LNA 中的SiGe HBT 時,引入金屬鈦(Ti)形成鈦硅合金來減小rb1,結合實際工藝水平,確定rb1 為28 Ω。

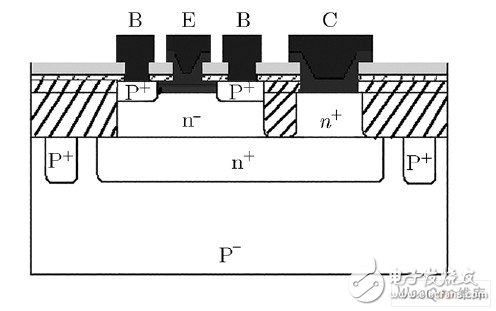

3 器件結構和電路制造

本文基于0.35 μm Si CMOS 平面工藝制定了放大器單芯片集成的工藝流程,并制作出一款單片集成SiGe HBT LNA。圖6 是SiGe HBT 的截面圖,考慮到工藝的難易程度,本文選用的SiGe HBT 結構為一種多晶硅發射極自對準結構。

圖6 SiGe HBT 的截面示意圖

工藝流程如下:

(1)選用電阻率為20Ω·cm 的P 型襯底硅片制作N+埋層,注入As,高溫退火推結,利用CVD 生長N? 外延層。

(2)生長氧化層。光刻隔離區,刻蝕隔離區氧化層和部分N? 外延層。光刻P+溝阻,B 離子注入。

高溫生長SiO2,表面平坦化。

(3)光刻穿透區,腐蝕去除穿透區氧化層。集電區擴P 穿透。在有源區利用MBE 差分外延SiGe 基區。外延之后,涂光刻膠,刻(有源區外)多晶硅。

(4)生長SiO2,淀積Si3N4,刻集電區、基區、發射區歐姆孔內Si3N4 和SiO2。淀積多晶硅,形成側墻,光刻基區,B 離子注入。光刻集電極和發射極。

(5)濺射金屬Ti,經過快速熱退火,形成鈦硅合金TiSi2,降低基區和發射區接觸電阻。TiSi2 形成以后,濺射多層金屬(TiW/AlCu),完成金屬互聯及反饋電阻制作。

(6)去膠,合金。

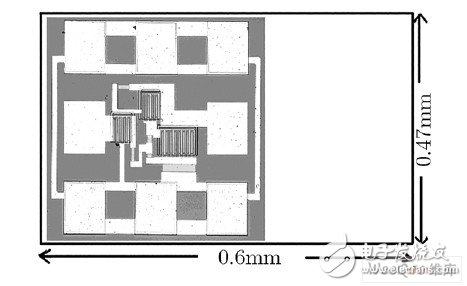

圖7 是最終完成的平面集成SiGe HBT LNA 芯片實物的顯微照片。LNA 芯片面積僅為0.282 mm2(0.6 mm×0.47 mm),比文獻[6]中單片集成SiGeHBT LNA 芯片面積小(0.78×0.66 mm2),這是因為沒有使用大面積的在片螺旋電感。

圖7 基于0.35-μm Si CMOS 平面工藝制作的單片集成SiGe HBT LNA 芯片圖

4 實驗結果

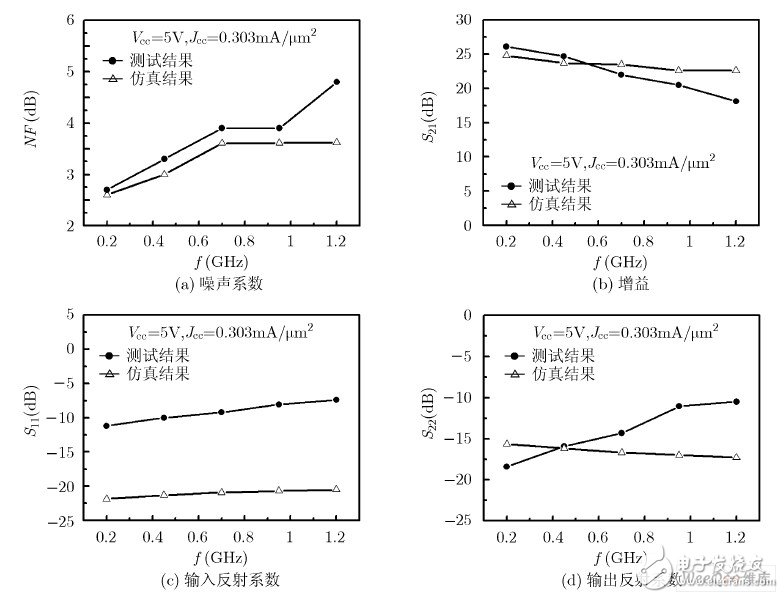

圖8 是本文研制的單片SiGe HBT LNA 仿真結果和測試結果對比。從圖8(a)和8(b)中可以看出,工作頻率從0.2 GHz 上升至1.2 GHz,噪聲系數始終小于4.8 dB,最小值低至2.5 dB,增益為18.1-26.7dB。在0.2-1.0 GHz 頻帶內,仿真結果較好地預測了實際測試結果。

圖8 單片SiGe HBT LNA 測試結果與仿真結果對比

圖8(c)展示了LNA 的輸出端口匹配情況。在整個頻帶內,輸入端口反射系數S11 的實測結果小于-7.4 dB,與仿真結果的偏離值保持在8 dB 左右。

原因可能是在實測中,LNA 的襯底損耗難免影響了輸入阻抗,使其偏離了設計時的預期值50 Ω。

圖8(d)給出了LNA 的輸出端口匹配情況。在整個頻帶內,輸出阻抗反射系數S22 的實測結果小于-10 dB。分析式(3)認為,系統輸出阻抗由LNA 的輸出電阻與偏置電阻并聯而成。在低頻時(0.2-0.4GHz),實際制作出的LNA 芯片襯底損耗與寄生效應修正了LNA 的輸出阻抗,使系統輸出阻抗實測值比仿真值更接近于理想值50 Ω,所以頻率較低時,實測結果優于仿真結果。隨著頻率進一步增大,放大器中電阻在高頻下不再是純實數電阻,其中偏置電阻的虛部值隨著頻率的增大而加劇影響系統輸出阻抗,使輸出阻抗實測值逐漸偏離50 Ω,所以在高頻時(0.4-1.2 GHz),仿真結果優于實測結果,并隨著頻率的增加,兩者差值增大。雖然圖8(c)和8(d)中端口阻抗的實測結果與仿真結果差別較大,但是在絕大部分頻帶范圍內還是小于-10 dB,顯示LNA 是具有良好的輸入輸出匹配。

5 結論

本文研制了一款具有多重電阻反饋結構的單片SiGe HBT 低噪聲放大器,通過靈活優化復合型反饋支路中的不同電阻,同時實現了低噪聲和良好端口匹配,解決了單一電阻反饋LNA 中的缺點,即需要花費巨大精力反復折中偏置、噪聲性能和端口匹配。基于0.35 μm Si CMOS 平面工藝,制定了放大器單芯片集成的工藝流程,并提出在制造SiGe 器件時,采用鈦硅合金(TiSi2)來減小rb1,達到進一步降低放大器噪聲的目的。基于上述工藝技術研制的單片SiGe HBT LNA 芯片面積僅為0.282 mm2。在端口匹配方面,雖然測試結果與仿真結果存在一定差異,但是其在大部分工作頻率范圍內仍小于-10 dB,因此本文研制出的LNA 匹配性能良好,并且仿真結果較好地預測了端口阻抗變化趨勢;噪聲系數和增益方面,測試結果與仿真結果符合較好,反映出設計方法和設計結構的正確性。

-

放大器

+關注

關注

145文章

14121瀏覽量

216649 -

電阻

+關注

關注

87文章

5615瀏覽量

174577 -

噪聲

+關注

關注

13文章

1139瀏覽量

47977

發布評論請先 登錄

寬帶低噪聲放大器噪聲分析

如何利用Cadence設計COMS低噪聲放大器?

低噪聲放大器介紹

利用Cadence設計COMS低噪聲放大器

低噪聲放大器設計的理論基礎

1.6GHz低噪聲放大器(特瑞仕)

3GHz CMOS低噪聲放大器優化設計

雙頻帶低噪聲放大器實現方案

CMOS基毫米波低噪聲放大器的研究

基于0.35 μmSi CMOS平面工藝設計了SiGe HBT低噪聲放大器

基于0.35 μmSi CMOS平面工藝設計了SiGe HBT低噪聲放大器

評論