在多媒體應用中,多媒體信息絕大部分是視頻數據和音頻數據,而數字化的視頻數據和音頻數據的數據量是非常龐大的。為了能夠及時完整地處理前端采集的數據,一般系統都采用高速DSP和大容量緩沖存儲器,且緩沖存儲器一般選用同步動態隨機存儲器(SDRAM)。由于DSP不能直接與SDRAM接口,而且SDRAM控制時序比較復雜,因此本文介紹如何利用電可擦除可編程邏輯器件實現TMS320C5402與SDRAM的接口。

1 、SDRAM結構和命令

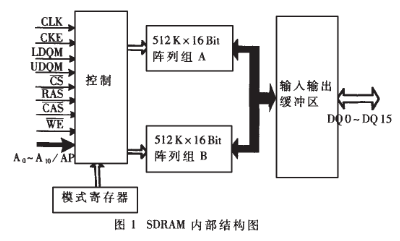

SDRAM是一種具有同步接口的高速動態隨機存儲器,本文選用的是Samsung公司512K×16Bit×2組的KM416S1120D。SDRAM的同步接口和內部流水線結構允許存儲外部高速數據,其內部結構框圖如圖1所示。

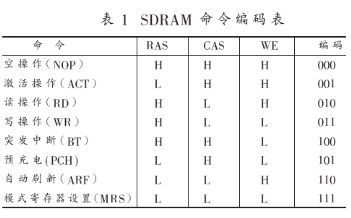

在具體操作SDRAM時,首先必須通過MRS命令設置模式寄存器,以便確定SDRAM的列地址延遲、突發類型、突發長度等工作模式;再通過ACT命令激活對應地址的組,同時輸入行地址;然后通過RD或WR命令輸入列地址,將相應數據讀出或寫入對應的地址;操作完成后用PCH命令或BT命令中止讀或寫操作。在沒有操作的時候,每32ms必須用ARF命令刷新數據(2048行),防止數據丟失。

2、 FLEX10K系列EPLD特點

FLEX10K系列EPLD是工業界第一個嵌入式的可編程邏輯器件,主要由嵌入式陣列塊(EAB)、邏輯陣列塊(LAB)、快速布線通道(FastTrack)和I/O單元組成,具有如下特點:

(1)片上集成了實現宏函數的嵌入式陣列和實現普通函數的邏輯陣列;

(2)具有10000~250000個可用門;

(3)支持多電壓I/O接口,遵守PCI總線規定,內帶JTAG邊界掃描測試電路;

(4)可快速預測連線延時的快速通道連續式布線結構;

(5)多達6個全局時鐘信號和4個全局清除信號;

(6)增強功能的I/O引腳,每個引腳都有一個獨立的三態輸出使能控制,都有漏極開路選擇。

3、 TMS320C5402和SDRAM接口設計

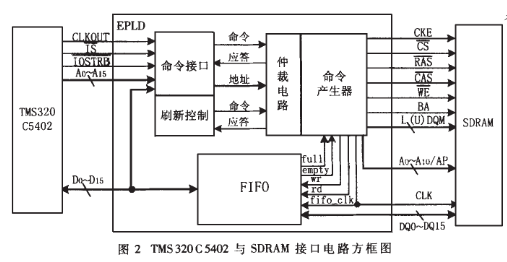

TMS320C5402和SDRAM接口電路方框圖如圖2所示。

命令接口主要對DSP送來的SDRAM的地址和操作命令進行解碼(命令編碼見表1);刷新控制主要對SDRAM數據刷新進行計時,確保32ms刷新2048行數據;仲裁電路主要對讀寫命令和刷新命令進行仲裁,杜絕同時操作,防止數據丟失;命令產生器主要用來產生控制SDRAM的各種時序,完成SDRAM的讀、寫和刷新,同時控制FIFO的讀、寫操作;FIFO是DSP與SDRAM之間的數據通道,深度為256,其作用是充分利用SDRAM的突發讀寫功能,提高系統速度,同時簡化DSP軟件設計。

3.1 命令接口和刷新控制電路設計

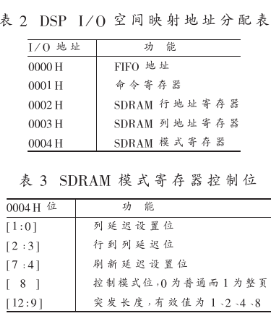

命令接口電路主要由命令寄存器、命令譯碼器、SDRAM行列地址鎖存器、模式寄存器組成。其中命令寄存器映射為DSP的I/O空間0001H,SDRAM行和列地址鎖存器分別映射為DSP的I/O空間0002H和0003H,模式寄存器映射為DSP的I/O空間0004H,具體控制命令和I/O地址分配如表2、表3所示。

DSP每次進行讀、寫操作時,首先向其I/O空間0002H和0003H寫入SDRAM行和列地址,然后向I/O空間0001H寫入控制命令,命令譯碼器根據命令寄存器中命令,譯碼后向仲裁電路發出讀寫請求。

刷新控制電路主要由1562計數器構成。由于TMS320C5402時鐘頻率為100MHz,SDRAM要求在32ms之內刷新2048行數據,因此該計數器計數值應小于:

32ms/2048/0.01μs=1562.5。當計數器計滿1562次時,刷新控制電路向仲裁電路發出刷新要求。

3.2 仲裁電路和命令產生器設計

仲裁電路接收命令接口模塊解碼的命令和刷新控制模塊的刷新請求,產生適當的控制命令,其中刷新請求的優先級較高。當來自DSP的命令和來自刷新控制模塊的刷新請求同時到達時,則首先執行刷新操作,然后執行來自DSP的命令。這樣可以防止SDRAM的數據丟失。由此可知,仲裁電路實質上是一個優先級選擇器。

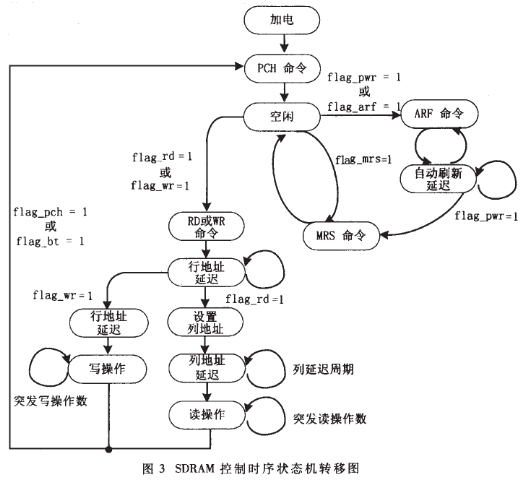

命令產生器主要產生SDRAM讀、寫和刷新的控制時序(具體時序可見參考文獻1)以及FIFO的讀寫控制信號,用以對SDRAM進行各種操作,其實質上是一個Mealy型狀態機,利用VHDL語言可以很方便地實現,其狀態轉移圖如圖3所示。

3.3 FIFO設計

FIFO電路是DSP與SDRAM進行數據交換的通道,通過FIFO電路可以很好地實現DSP對SDRAM的讀寫。FIFO電路被映射為DSP的I/O空間0000H(見表2),DSP對SDRAM的每次讀或寫,都對DSP的I/O空間0000H操作,簡化了DSP軟件設計。利用FLEX10K系列EPLD內部嵌入式陣列塊(EAB)和參數化模塊庫(LPM),可以很快地構造出256×16的FIFO電路,FIFO的設計比較簡單。VHDL描述具體如下(注意在程序開始處添加LPM庫):

FIFO256 CSFIFO

GENERIC MAP LPM_WIDTH <= 16;LPM_NUM-

WORDS <= 256;

PORT MAP data <= LPM_WIDTH-1 DOWNTO 0;

wreq <= wr;rreq <= rd;

clock <= clk50;clockx2 <= clk100;

clr <= clr;sclr <= sclr;

empty <= empty;full <= full;

q<=qLPM_WIDTH-1 DOWNTO 0;

由于EPLD通用、高速及價廉的特點,因此具有很好的實際應用前景,尤其適用于需要大容量高速緩沖存儲器的多媒體應用。

責任編輯:gt

-

SDRAM

+關注

關注

7文章

441瀏覽量

56077 -

存儲器

+關注

關注

38文章

7637瀏覽量

166537 -

可編程邏輯

+關注

關注

7文章

524瀏覽量

44599

發布評論請先 登錄

可編程邏輯器件

求一種可利用復雜可編程邏輯器件設計技術實現的專用鍵盤接口芯片方案

PLD可編程邏輯器件

可編程邏輯器件基礎及應用實驗指導書

什么是PLD(可編程邏輯器件)

基于可編程邏輯器件的數字電路設計

利用電可擦除可編程邏輯器件實現DSP與SDRAM接口設計

利用電可擦除可編程邏輯器件實現DSP與SDRAM接口設計

評論