引言

語音通信電臺是當今軍事指揮、工業調度和日常生產活動中主要的溝通設備,其通信質量與抗干擾能力將對國防和經濟建設產生直接影響。語音電臺抗干擾客觀評估系統(以下簡稱評估系統)通過數字信號處理算法比較在發送電臺端錄取的標準語音文件與在接收電臺端錄取的失真語音文件之間的信號特征,給出語音電臺的抗干擾性能參數。由于語音信號是按照每20 ms一個語片進行處理,故對語音信號的對準提出了較高的要求,為了達到較高的評估精度,對準誤差應小于1 ms。

為了滿足上述技術指標,本文采用當前剛剛興起的SOPC(System On a Programmable Chip)技術在FPGA(Field Programmable Gate Arr ay)平臺上設計了一種帶有時標的嵌入式語音信號錄取系統。本系統通過捕獲GPS(Global Positioning System)系統的授時信息和秒脈沖信號,觸發SOPC系統中NiosⅡ嵌入式軟核處理器進入外部中斷,調用中斷處理函數啟動音頻Codec芯片WM8731,對Line-in通道輸入的模擬語音信號進行48 KSPS采樣率、16 b采樣精度的錄取,將觸發錄取的時間信號作為時標與錄取得到的數據按照特定數據格式進行打包和封裝,并利用FAT文件系統將封裝好的數據存儲到SD卡(Secure Digital Card)中。由于GPS秒脈沖前沿可以達到微秒級精度,加之WM8731控制接口采用Verilog語言編寫,從而保證了絕對時間誤差遠遠小于1 ms的技術要求。

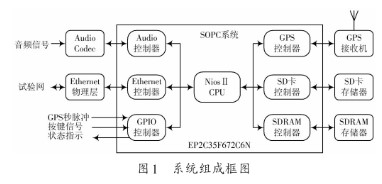

1、 系統組成

SOPC是基于可編程邏輯器件的可重構片上系統(SOC),它集成了硬核或軟核CPU、DSP、鎖相環、存儲器、I/O接口及可編程邏輯,由于具有設計靈活、研制周期短、開發成本低等優點,已經逐步應用在通信、工控、信號處理等諸多領域。

為了給評估系統提供高精度、帶有時標的語音數據源,本文采用SOPC技術在FPGA平臺設計了一套帶有時標的嵌入式語音信號錄取系統(以下簡稱錄取系統)。錄取系統由片上系統和外圍系統兩部分組成。片上系統包括:NiosⅡ嵌入式軟核處理器、GPS控制器、SD卡控制器、SDRAM控制器、Audio控制器、Ethernet控制器、GPIO控制器以及內部Avalon總線;外圍系統包括:GPS接收機M12MT、SD存儲卡、SDRAM存儲芯片、Audio Codec芯片WM8731、Ethernet物理層芯片DM9000A和傳輸變壓器以及按鍵和LED等輸入與顯示器件等。系統組成框圖如圖1所示。

2、 硬件結構設計

在FPGA平臺上設計SOPC系統為本文的核心工作。FPGA芯片選擇Altera公司CycloneⅡ系列的EP2C35F672C6N,其具有33 216個邏輯宏單元、105個M4K存儲單元、4個鎖相環以及475個通用I/O口。FPGA開發環境采用QuartusⅡ,嵌入式系統開發環境采用SOPC Buildero由于Nios Ⅱ嵌人式軟核CPU、SDRAM控制器、Ethernet控制器和GPIO控制器都是SOPC Builder中集成的通用IP核,直接調用即可,故本文不做詳細介紹,下面對GPS控制器、Audio控制器和SD卡控制器進行詳細介紹。

2.1 GPS授時系統的設計

本設計中所使用M12MT是一款5 V供電、RS 232電平NAEA 0183格式串行輸出、TTL電平秒脈沖(PPS)輸出型GPS模塊,由于FPGA芯片I/O口是3.3 V電平,故需要進行電平轉換,串口電平轉換采用美信(Maxim)公司生產的MAX3232芯片,秒脈沖信號由TI公司生產SN74AHC1G04單緩反向器芯片生成。

由于SOPC Builder中的UART核通信協議可以與GPS串口輸出協議兼容,故本設計中經過電平轉換的信號與片內UART核相連,其參數設為:波特率為9 600b/s、1個起始位,1個停止位,無校驗位。秒脈沖經電平轉換后與PIO控制器相連,其參數設為輸入模式、帶有中斷功能、邊沿觸發中斷、下降沿觸發中斷。

2.2 音頻采集系統的設計

為了達到較高的錄音品質,本設計中選用Wolfson公司生產的音頻Codec芯片WM8731,其最高可支持96 KSPS采樣率、24 b采樣精度的立體聲輸入/輸出。考慮到語音電臺抗干擾評估系統的特殊要求和存儲空間、處理速度等條件的限制,本設計中通過軟件設置,使WM8731工作在48 KSPS采樣率、16 b采樣精度、單聲道的工作模式下。

WM8731的控制接口和音頻數據接口分別采用I2C總線和I2S總線,由于控制總線數據量較少,加之I2C總線時序比較簡單,故采用程序控制PIO模擬I2C總線的方式對其進行控制;由于數據總線數據量較大,并且必須保證數據的完整性,本設計采用Verilog硬件描述語言編寫了一個Audio控制器,完成采樣控制、數據緩存以及與Avalon總線接口等功能。

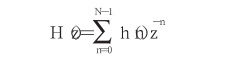

Audio控制器由有限狀態機(FSM)、數據緩存器(FIFO)和總線接口三部分組成,如圖2所示。FSM完成WM8731數據讀寫的控制、FIFO讀寫與存儲狀態控制以及總線接口控制。FIFO用來緩沖WM8731采集得到的數據,防止數據丟失,并使系統工作在異步模式,大大提高了CPU的工作效率。總線接口作為橋梁,用以連接NiosⅡ和FIFO。

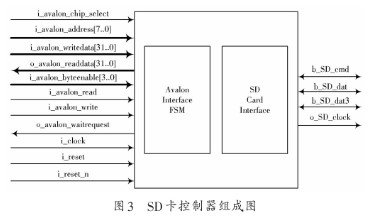

2.3 數據存儲系統的設計

為了實現大容量數據存儲,本采集系統選用當下比較流行SD卡作為存儲介質。由于SD卡采用的是串行讀寫方式,時序較為復雜,且其數據量較大,故采用Verilog編寫了SD控制器,其結構如圖3所示。Avalon Interface FSM與Avalon總線相連接,用來完成控制器與NiosⅡ處理器通信;SD Card Interface與SD卡相連,完成數據的串/并轉換和時序控制。

3、 軟件程序設計

本采集系統軟件在Nios EDS環境下進行開發,由于程序中只有一個線程,結構比較簡單,故并未采用操作系統。主程序在完成各個模塊初始化后進入等待狀態,GPS的串口數據、PPS觸發信號和按鍵觸發信號采用中斷形式,利用中斷服務子函數完成各項功能。

3.1 時間信息的解析

由于GPS接收機M12MT具有多種數據輸出格式,其中時間格式默認為為格林威治標準時間,故為了保證數據解析的正確性,在系統啟動后首先對GPS接收機進行初始化,使其時區設定為GMT+8,每秒鐘串口輸出一組數據,格式采用@@Eq形式。

由于UART控制器每收到1個字節即產生一個中斷,故NiosⅡ處理器首先需要對接收到的數據進行緩存,當收到5個字節后判斷是否是報頭,如果是報頭就繼續接收,否則計數器清零并重新進行緩沖。在報頭解析正確后,處理器將所有報文依次接收并存儲到緩沖區中,緩沖區中的前18位即是時間數據,其格式為mm,dd,yy,hh,mm,ss。

需要特別說明的有兩點:第一,由于每一秒的PPS信號早于串口數據的輸出,故處理器需要對接收到的時間加1 s,而后利用下一個PPS信號進行觸發;第二,GPS接收機在鎖定3顆以上衛星時時間數據才具有可靠性,故需要判斷報文中的fix標志位,如果fix位是1,這表明衛星已鎖定,時間信息可靠,PPS信號可以作為觸發信號。

3.2 采集數據的封裝

Audio控制器輸出的數據是按照采樣時刻先后順序生成的一系列二進制數值點,為了加入起始時刻的時間標志,同時便于評估系統進行后續處理,本錄取系統對采樣起始時刻和采樣數據進行封裝。首先將采樣數據封裝成WAV文件格式,加入相應的格式標志、采樣率、采樣精度、聲道數、數據長度等信息,然后再在WAV文件的前面加入二進制的時間信息形成DAT格式文件。評估系統通過DAT文件中的時間信息和WAV文件中的采樣率等信息即可計算出每個采樣點的絕對時間。

3.3 文件系統的引用

為了提高SD卡存儲的兼容性,便于通用計算機對SD卡的寫入和讀取,本錄取系統利用FAT文件系統對SD卡進行讀寫操作。由于處理器中沒有使用操作系統,故需要自己移植文件系統和編寫底層驅動函數。

本錄取系統中的文件系統采用層次結構設計,共分為3層,即硬件描述層(HAL)、功能層和應用層。硬件描述層完成SD卡檢測、控制命令的寫入、數據的讀寫等功能;功能層完成塊數據的讀寫、查找、替換等功能;應用層完成格式化、文件建立與刪除、文件寫入與讀出等功能。主函數調用應用層的功能函數即可完成對SD卡的文件操作。

4 、結論

本文介紹了一種利用SOPC技術在FPGA平臺上實現帶有時標的嵌入式語言信號錄取系統,不但論述了錄取系統的結構組成與工作原理,而且對GPS控制器、Audio控制器、SD卡控制器等硬件設計和GPS時間解析、采集數據的封裝、文件系統的引用等軟件編寫進行了詳細的介紹。經實際使用驗證,本錄取系統能夠在GPS時間觸發下完成語音信號的錄取,錄取得到的數據帶有時標信息,能夠滿足語音電臺抗干擾客觀評估系統的技術要求。

責任編輯:gt

-

FPGA

+關注

關注

1643文章

21974瀏覽量

614347 -

芯片

+關注

關注

459文章

52217瀏覽量

436527 -

sopc

+關注

關注

2文章

248瀏覽量

63142

發布評論請先 登錄

語音信號產生原理及應用

基于FPGA的語音信號實時處理

語音信號分析處理系統(Matlab實現)

語音信號的數字化噪聲抑制技術

如何DSP設計語音信號采集系統的論文說明

基于FPGA芯片和SOPC技術實現時標語音信號錄取系統的設計

基于FPGA芯片和SOPC技術實現時標語音信號錄取系統的設計

評論