圖像處理通常采用軟件或者數字信號處理器(DSP)實現。如果利用軟件實現,運行時會耗費較多的PC資源,而且算法越復雜時耗費的資源就越多,對于需要高速處理的情況不適用;而如果采用DSP實現,提高并行性的同時指令執行速度必然會提高,較高的指令速度可能導致系統設計復雜化,并增加功耗和成本。新一代的低功耗現場可編程門陣列(FPGA)憑借其強大的高速并行能力,日益成為高速實時圖像處理的主流器件。單精度浮點加法運算是數字圖像處理的最基礎的數據運算方式,在此介紹一種在FPGA上實現單精度浮點加法運算的方法。

1 IEEE 754單精度浮點數存儲格式分析

1.1 實數的IEEE 754表示形式

在計算機系統的發展過程中,曾經提出過多種方法表示實數,但是到目前為止使用最廣泛的是浮點數表示法。相對定點數而言,浮點數利用指數,使小數點的位置可以根據需要而上下浮動,從而可以靈活地表達更大范圍的實數。電子電氣工程師協會(Institute of Electricaland Electronics Engineers,IEEE)在1985年制定的IEEE754(IEEE Standard fOr Binary Floating-Point Arithme-tic,ANSI/IEEE Std 754-1985)二進制浮點運算規范,是浮點運算部件事實上的工業標準。一個實數V在IEEE754標準中可以用V=(-1)S×M×2E表示,說明如下:

(1)符號S決定實數是正數(S=0)還是負數(S=1),對于數值0的符號位特殊處理。

(2)有效數字M是二進制小數,M的取值范圍在1≤M《2或0≤M《1。

(3)指數E是2的冪,它的作用是對浮點數加權。

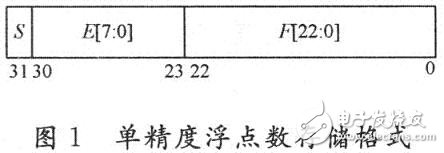

1.2 IEEE單精度浮點格式

浮點格式是一種數據結構,它規定了構成浮點數的各個字段。IEEE 754浮點數的數據位被劃分為3個字段,對3個字段參數進行編碼:

(1)一個單獨的符號位S直接編碼符號S。

(2)K位的偏置指數E編碼指數E,移碼表示。

(3)N位的小數.f編碼有效數字M,原碼表示。

IEEE單精度浮點格式共32位,包括3個構成字段:23位小數F,8為偏置指數E,1位符號S。將這些字段連續存放在一個32位字里,并對其進行編碼。其中O~22包含23位的小數F;23~30包含8位指數E;第31位包含符號S。如圖1所示。

2 單精度浮點加法器的設計與實現

2.1 單精度浮點加法器的算法設計

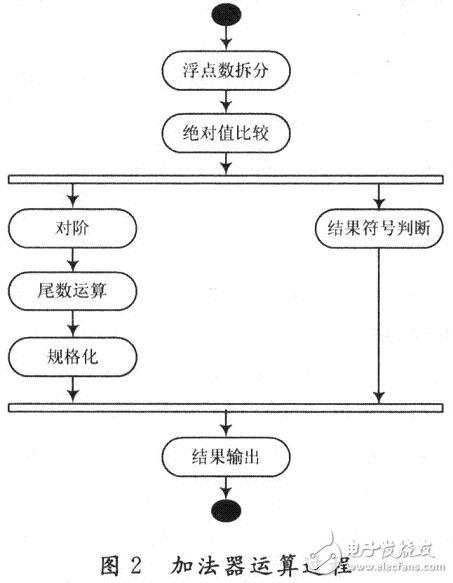

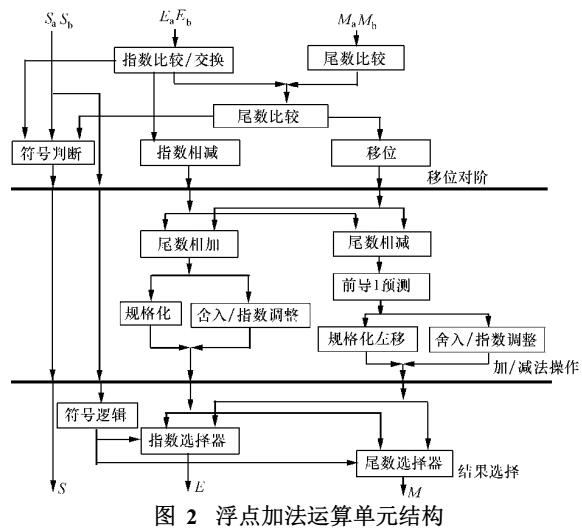

浮點加法器首先對浮點數拆分,得到符號、階碼、尾數。對拆分結果進行絕對值比較,得到大的階碼、階差和比較結果輸出。然后進行對階,通過移位小的尾數,得到相同大階。對尾數進行尾數加減運算,得到的結果進行規格化,最后結合規格化結果運算結果符號輸出,得到結果輸出。加法器運算過程如圖2所示。

2.2 單精度浮點加法器的實現

2.2.1 總體設計

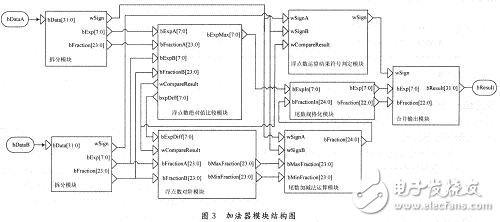

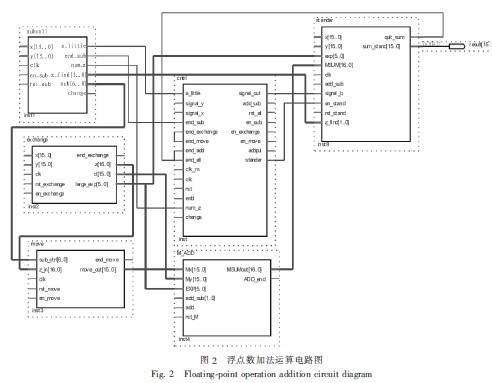

浮點加法器包括兩個浮點數拆分模塊、絕對值比較模塊、浮點數運算結果判定模塊、對階模塊、尾數加減運算模塊、尾數規格化模塊、合并輸出模塊。其中對階模塊包括尾數交換,尾數移位兩個子模塊;尾數加減運算模塊尾數運算符號判定,尾數加減兩個子模塊。兩個浮點數拆分模塊分別將兩個浮點數拆分成符號、階碼、尾數3部分,絕對值比較模塊通過對兩個浮點數的絕對值大小的比較得到大階,階差和絕對值比較結果,大階直接輸出;對階模塊然后實現對小階的尾數進行移位,將小階與大階對齊,并對尾數進行移位;尾數加減運算模塊判定尾數運算符號后,進行尾數運算;尾數規格化模塊對結果完成尾數規格化,同時調整階碼;最后結合浮點數運算結果判定模塊的符號輸出,經過合并輸出模塊,得到結果輸出。總體設計框圖如圖3所示。

2.2.2 各模塊設計實現說明

(1)拆分模塊。該模塊將輸入的浮點數拆分成符號位、價碼、尾數3部分。符號位信號wSign,指數位信號bExp[7:0],尾數位信號bFraction[23:0]。

(2)浮點數絕對值比較模塊。該模塊通過對輸入浮點的階碼及尾數的比較,相應得出wCompareResult,bExpDiff,bExpMax三種信號輸出。當bExpA≥bEx-pB時:wCompareResult=1,bExpDiff=bExpA-bEx-pB,bExpMax=bExp;當bExpA《bExpB時:wCom-pareResult=0,bExpDiff=bExpB-bExpA,bExpMax=bExpB。

(3)浮點數運算結果符號判定模塊。浮點數符號運算結果判別模塊通過操作數bDataA,bDataB符號位及wCompareResult信號的輸入判定運算結果數的輸出。

(4)浮點數對階模塊。對階模塊根據wCompare-Result的結果對輸入的操作數尾數bFractionA和bFractionB進行操作。當wCompareResult=1時,對bFractionB進行右移位,移位量為bExpDiff,并且將移位后的結果作為bMinFraction輸出,將bFractionA作為bMaxFraction直接輸出;反之對bFractionA進行右移位,移位量為bExpDiff,并且將移位后的結果作為bMinFraction輸出,將bFractionB作為bMaxFraction直接輸出。

(5)浮點數對階模塊。此模塊實現對階后的尾數的加減運算,然后輸出結果尾數的值。當wSignA,wSignB同號時,尾數bMaxFraction與bMinFraction相加的結果作為bFraction輸出;當wSignA,wSignB異號時,尾數bMaxFraction與bMinFraction相減的結果作為bFraction輸出。

(6)尾數規格化模塊。尾數bFractionIn[24:0]通過判定從左邊第一次不為0的位后,將此位數左移到第一位隱藏位,相應添加尾數補0,共計24位。同時,將階碼調整,再隱藏隱藏位,調整后的階碼和尾數以bExp,bFraction輸出。

(7)合并輸出模塊。將浮點數運算結果符號判定模塊的輸出信號wSign與尾數規格化模塊的輸出信號bExp,bFraction合并,得到輸出結果。

3 結 語

介紹一種在FPGA上實現的單精度浮點加法運算器,運算器算法的實現考慮了FPGA器件本身的特點,算法處理流程的拆分和模塊的拆分,便于流水設計的實現。該加法器在參與設計的多款CPCI總線圖形控制器圖形加速子系統上得到實際的應用和檢驗,在處理速度方面表現出很強的適用性。

-

dsp

+關注

關注

556文章

8148瀏覽量

355669 -

FPGA

+關注

關注

1643文章

21983瀏覽量

614907 -

軟件

+關注

關注

69文章

5134瀏覽量

89006

發布評論請先 登錄

verilog語音實現浮點運算

針對FPGA或ASIC部署的浮點算法

采用FPGA和MicroBlaze進行嵌入式系統設計

基于FPGA高精度浮點運算器的FFT設計與仿真

為什么研究浮點加法運算,對FPGA實現方法很有必要?

在FPGA上實現單精度浮點加法運算器算法的設計

在FPGA上實現單精度浮點加法運算器算法的設計

評論