引 言

同傳統的脈沖超寬帶(IR-UWB)相比,線性調頻超寬度(Chirp-UwB)以其發射效率高,頻帶選擇靈活,抗多徑能力強,容易實現模擬匹配檢測等突出優點,已逐漸成為超寬帶技術領域的研究熱點。

然而,對于寬帶Chirp-UWB信號的產生一直是個難題。利用直接數字合成(DDS)產生可以獲得高線性度、高穩定性的信號波形,但是由于模數轉換器(DAC)速度的限制以及輸出幅度受SINC衰落的影響,其輸出信號帶寬一般最高為100~200 MHz。利用模擬鎖相環(PLL)雖可以產生很寬的帶寬,可是受PLL自身惰性環節的影響,調頻時間慢,轉換速率低,且因其受鎖相精度及壓控振蕩器(VCO)電調線性度的影響,還需要進行非線性補償,這使電路趨于復雜。本文提出一種基于DDS+PLL的Chirp-UWB信號產生方案。該方案把頻率穩定度好,輸出頻率分辨率高,頻率轉換速度快,相位噪聲低的DDS與模擬PLL結合,取長補短,可以獲得高頻率分辨率、快的信號建立時間、低相位噪聲和寬輸出頻率范圍的高質量Chirp-UWB信號。

1 系統結構

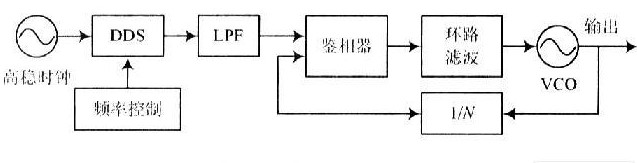

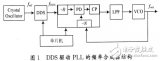

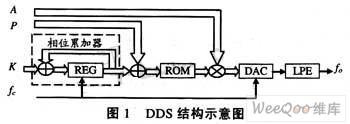

DDS結合PLL產生Chirp-UWB信號的系統結構如圖1所示。

本方案由DDS產生的窄帶Chirp信號作為PLL的參考信號。VCO產生的高頻振蕩經N分頻后,在鑒相器(PD)中與DDS產生的窄帶線性調頻信號進行相位比較。系統穩定后,VCO產生的高頻振蕩經N分頻后,其信號與DDS產生的窄帶chirp信號的掃頻線性度和頻率穩定度一致。在這個方案中,PLL實際起到了倍頻的作用,即將DDS輸出的高線性調頻信號進行了N倍的倍頻。由于DDS輸出頻率和帶寬可以編程控制,這種方式產生的Chirp-UWB帶寬是可控的,在設計上具有很大的靈活性。

2 系統設計與仿真

本系統主要由參考信號發生電路,鎖相環電路兩部分組成。對于鎖相環電路,射頻仿真軟件ADS提供有專門的元件庫(System-PLL components),可以利用其中的元件快速建立鎖相環的電路模型。然而,基于DDS產生的參考信號則由鋸齒波控制線性VCO來實現,只要合理設置參數,這種等效并不會影響系統性能。下面對電路的各部分的設計進行分析。

2.1 參考信號產生

參考信號的產生可通過數字正交上變頻芯片AD9857實現,中心頻率設為100 MHz,Chirp信號的帶寬設為7 MHz。利用ADS仿真時由鋸齒波控制線性VCO,即可產生一個窄帶Chirp信號作為鎖相環的輸入參考信號。

2.2 鑒相器和分頻器

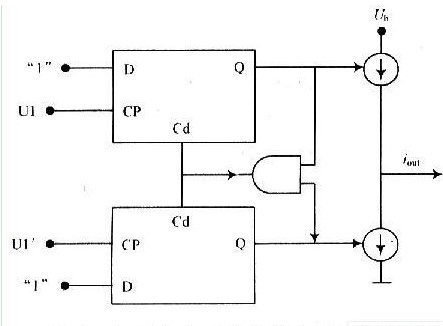

通常鎖相環芯片都同時集成鑒相器和分頻器,如ADI公司的ADF4106。該芯片鑒相器采用電荷泵輸出的鑒相器。圖2為一個電荷泵輸出鑒相器的原理圖。

這種鑒相器由兩個D觸發器、一個與門和兩個電流源構成,不僅可以鑒相,也可以鑒頻,同時由于它采用電流源輸出,克服了電壓輸出型鑒頻鑒相器增益變化的不足。該鑒相器的輸出電流與相位誤差關系為iout=Kdθe/Rb,其中:Rb為鑒相器電壓電流轉換器固有的跨阻。分頻器的作用是將VCO產生的輸出信號頻率除以N,然后輸入鑒相器與參考信號進行比較。仿真時,直接采用ADS提供的元件Divide by N來實現,設其分頻比N=70。

2.3 低通濾波器

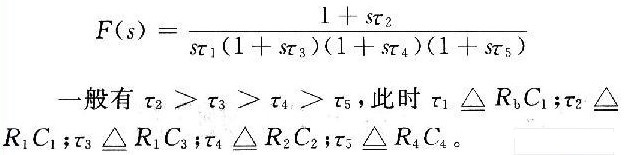

環路濾波器的設計是鎖相環設計的關鍵。本設計中需要跟蹤一個頻率斜升信號。根據鎖相原理,要跟蹤此類信號,必須二型以上環路。本設計中環路濾波器采用四階二型無源環路濾波器,由于電荷泵型鑒相器的輸出為電流,所以該環路等效于一個二階有源比例積分濾波器加兩級輔助濾波。輔助濾波用于濾除參考信號饋通。環路傳輸函數F(s)可以近似表示為:

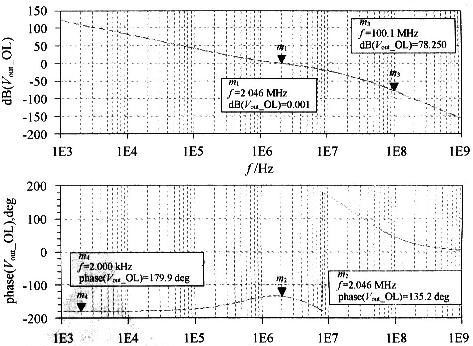

根據鑒相頻率為100 MHz,這里選擇截止頻率ft為2 MHz。根據穩定性原理,通常選擇5~10倍ω3,ω5為3~8倍ω4,而ω1的選取則是保證環路幅頻響應在ft處過零點。在ADS環境下,對模型中各元件大致設定一個初值及優化區間,然后進行優化設計,即可得到各元件值。最終鎖相環開環響應如圖3所示。

從圖3中可以看出,環路截止頻率為2 MHz,相位裕量為45°,在鑒相頻率100 MHz處,衰減為78 dB,這可以滿足穩定條件,且可以抑制參考頻率饋通。

2.4 壓控振蕩器

一個理想的VCO輸出周期信號,其周期信號的頻率與控制電壓Vcnt呈線性關系,即:

式中:ω0為VCO的自由振蕩頻率;KVCO為VCO增益(單位為rad/s/V)。

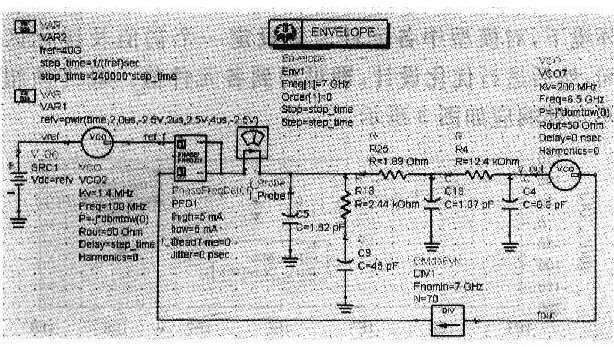

實際電路中,VCO的增益是非線性的。在ADS設計仿真中,為了更加接近真實電路,VCO的增益KVCO可以不設置為常數,而是根據輸出頻率不同,使用函數pwl()來進行數值擬合。經仿真對比發現,當鎖相環鎖定時,KVCO的細微波動并不會給仿真結果帶來影響。為了便于通過觀察VCO控制電壓來考察輸出信號的線性度,以下的仿真中KVCO設為固定值200 MHz/V。

3 結果分析

根據上面分析,在ADS環境下建立如圖4所示的系統電路模型,該電路可以輸出中心頻率為7 GHz,帶寬500 MHz的chirp-UWB信號。

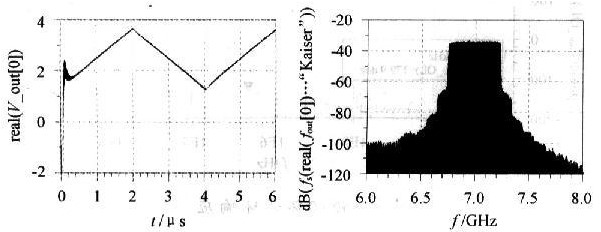

3.1 ADS仿真結果

對于Chirp-UWB信號性能分析,關鍵是考察信號的穩定性和線性度。在本系統中,信號由VCO產生,所以通過觀察VCO控制電壓波形和VCO輸出頻譜即可,圖5為仿真結果。從圖中可以看出,其VCO能夠跟蹤參考信號頻率的變化,產生所需帶寬的Chirp-UWB信號,且其旁瓣較低,完全能滿足系統設計的要求。

3.2 利用Matlab讀取ADS數據進行分析

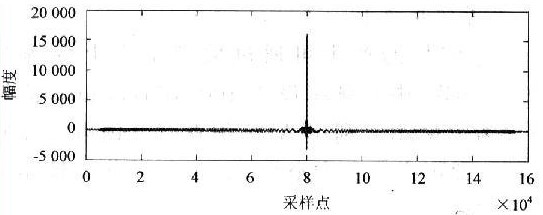

對于Chirp-UWB信號的性能分析還有個重要的指標就是其自相關特性,然而在ADS環境下很難實現這樣的分析。為此,本文利用Matlab讀取ADS仿真數據來實現對信號自相關特性的分析。

ADS仿真輸出數據可以存為一個ASCII格式的記事本文件。文件中每個數據均采用科學記數。其中,奇數個數表示時間,偶數個數表示信號。這樣就可以用Matlab程序來讀取仿真數據,如圖6所示為信號自相關結果。從該圖可以看出,信號相關性能很好,由此證明這種基于鎖相環的Chirp-UWB產生的電路性能較好。

4 結 語

首先利用ADS,對Chirp信號的產生電路進行建模和仿真,然后利用Matlab讀取ADS仿真數據,對系統性能進行分析,由此證明本文提出的基于DDS+PLL的寬度Chrip-UWB信號產生方案,可以產生線性度高,自相關特性好的Chrip-UWB信號。該信號產生方案已經成功應用于某超寬帶通信系統中。

-

振蕩器

+關注

關注

28文章

3974瀏覽量

140565 -

DDS

+關注

關注

22文章

672瀏覽量

154172 -

模數轉換器

+關注

關注

26文章

3315瀏覽量

128074

發布評論請先 登錄

請問怎么用Verilog寫一個DDS產生Chirp線性調頻信號

DDS 架構的各要素

請問AD9854能產生的chirp信號的最短時寬是多少呢?

PLL相比于DDS所擁有的典型優勢分享

Chirp脈沖波形的性能參數對脈沖頻譜的影響介紹

基于DDS+PLL在電臺設計中的應用

基于DDS驅動PLL結構的寬帶頻率合成器的設計與實現

VHDL語言與DDS技術結合產生的的BPSK信號

將DDS于PLL相結合實現產生Chirp-UWB信號

將DDS于PLL相結合實現產生Chirp-UWB信號

評論