引言

現代系統設計許多都是由C/C++,Python等高級語言來完成,而且這些系統越來越復雜,涉及到的算法的運算量也越來越大,許多算法需要用硬件實現來滿足算法的實時性要求.FPGA是一種可編程的邏輯器件,它具有便于修改,調試,并能并行地完成大量的運算,從而提高算法的實時性,并且隨著硬件制造水平不斷地提高,FPGA的資源越來越大,工作頻率也越來越高,使得能在其上面完成的算法也越來越復雜.但是傳統的軟硬件分開設計的方法由于軟硬件設計者采用不同的設計語言,存在軟硬件設計者之間難以溝通導致設計周期長等問題,這種設計方法已不能滿足快速地增長的市場要求,如何將這些系統設計中的算法快速轉換為相應的硬件來實現,需要新的軟硬件協同設計方法.當前基于C/C++的軟硬件協同設計,有一個SystemC 標準化組織一直致力于這個工作,也有少量商業化工具例如Syn-opsys 公司Synphony C Compiler 和Calypto Design Sys-tems 公司的Catapult SL Synthesis 可以將C/C++算法轉換為相應的硬件.Python是一種簡單易學并且功能強大的編程語言,有許多算法是由Python來實現,而且這些算法很多是免費.開源的,和C/C++類似需要如何完成基于Python的軟硬件協同設計.

1 基于Python 的軟硬件協同設計發展

由于Python的強大的軟硬件描述能力,近年來許多研究者在Python的軟硬件協同設計方面進行了許多研究,其中Logaras E 提出了一種稱為SysPy(System Py-thon)可以使用Python 來描述硬件并將其自動轉換為VHDL,Zhang mi采用PDSDL(Dynamic System Descrip-tion Language)來進行系統建模和校驗并可將系統轉換為Verilog的硬件描述,特別是Decaluwe J提出一種稱為MyHDL 的Python 擴展包來進行軟硬件協同設計,Villar J I采用MyHDL 完成了一個接口設計實例.這些開發工具各自具有自己的一些特點,但是他們有一點是相同,就是采用Python來進行軟硬件協同設計.下面以MyHDL為例介紹基于Python的軟硬件協同設計.

2 基于Python 的MyHDL 包簡介

MyHDL采用Python擴展包的形式使其能支持硬件設計和仿真并在仿真結果符合要求后可將軟件算法自動轉換為相應的采用Verilog 或VHDL 硬件描述,由于MyHDL包是基于Python的硬件擴展,下面主要對MyH-DL硬件方面的一些主要特點做簡要介紹.

2.1 數據類型

標準Python的int類型已經具有許多硬件設計所需要特征,但是在硬件設計中由于包含許多位操作和處理,MyHDL設計了intbv類,提供索引和切片操作來支持位的操作和處理.

在MyHDL采用函數來對硬件的模塊進行建模,My-HDL也有信號對象,類似于VHDL語言的信號,采用信號作為函數的參數來定義模塊的端口.

2.3 發生器

發生器是MyHDL 的一個關鍵概念,用來建立并發性模型,對應于Verilog的always塊或者VHDL的進程.

2.4 自動轉換

在一定限制條件下,MyHDL使用toVerilog()或者toVHDL()函數將MyHDL設計自動轉換為相應的Veril-og或者VHDL代碼,如果符合MyHDL可綜合子集的要求,就可使用MyHDL完成可硬件綜和的代碼并在FPGA上實現.

2.5 仿真

MyHDL通過Cosimulation對象使其能支持仿真,對于自動轉換的Verilog 代碼或者VHDL 代碼,MyHDL 還可作為硬件校驗語言來對轉換后的Verilog或VHDL進行協同仿真和校驗.

3 采用MyHDL 的硬件設計優點

Verilog和VHDL是當前的主流硬件設計語言,但是使用基于Python的MyHDL作為硬件設計也具有許多優點使得其可以作為設計者特別是硬件設計的初學者另外一種較好的選擇.

3.1 MyHDL使用成本低

MyHDL是免費的并且開源,在使用MyHDL設計的工具鏈中同樣可以使用大量的免費工具比如ICArus,IVERILOG仿真工具,GTKWAVE查看仿真波形,從而可以減少設計成本.

3.2 在硬件設計中使用先進的軟件開發技術

由于Python本身是一種軟件開發語言,現代軟件開發的先進方法比如快速應用開發,測試驅動開發都在Python上得以體現,由于硬件描述語言的硬件設計和軟件開發具有一定的相似性,采用MyHDL可以使用最新的軟件開發技術.

3.3 軟硬件設計可以采用同樣的開發環境

Python是算法實現的一種理想的語言,很多算法都由Python實現,通常算法的軟硬件實現由不同工程師來實現,軟件工程師使用Python,硬件工程師使用通用的硬件描述語言,例如Verilog或VHDL,硬件工程師和軟件工程師之間存在一條鴻溝,而采用MyHDL,就可以在同一個Python環境實現算法設計,仿真和校驗.

3.4 其他優點

對于沒有一定硬件設計經驗的設計者,通常采用Verilog 設計會混淆阻塞和非阻塞賦值,不清楚Verilog的符號運算,采用VHDL進行設計又不理解VHDL的信號概念,會覺得VHDL的類型和位寬轉換很繁瑣,但是如果采用基于Python 的MyHDL 包作為設計語言,這些都將不成為問題.

4 基于Python 的軟硬件設計流程

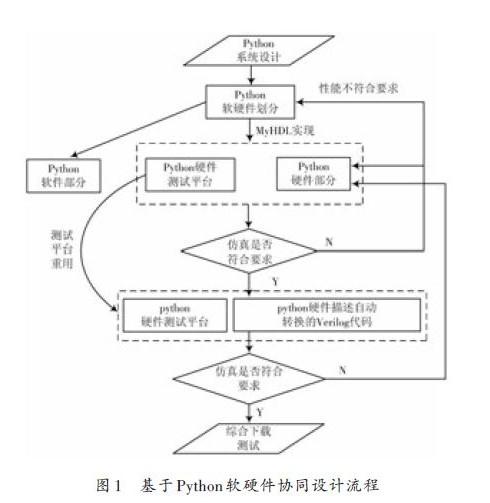

在現代系統設計中,軟件工程師采用Python等高級語言,而硬件系統設計多采用Verilog,VHDL硬件描述語言,在如何將Python描述的軟件映射為相應的硬件上,軟硬件開發者之間的交流存在一道天然的鴻溝,而采用Py-thon來進行軟硬件協同設計就可以解決這一個問題,基于Python的軟硬件協同設計的流程如圖1所示.

首先采用Python進行系統設計,然后根據系統性能要求進行軟硬件劃分,對于系統性能要求比較高的部分采用Python的MyHDL擴展包的形式來由硬件實現,同時采用Python來編寫硬件測試平臺.測試仿真如果不符合系統設計要求可以重新進行軟硬件劃分,如果測試仿真結果不正確,可重新修改.仿真通過后可以用MyHDL擴展包自動將Python轉換為Verilog代碼,這時的Python測試平臺無需修改還可以與轉換后的Verilog代碼一起進行混合仿真,如果仿真通過就可以進行硬件的綜合,下載,測試階段,這與傳統的硬件設計過程相同.

5 結語

從上面分析可以看出基于Python的MyHDL既是一種軟硬件協同設計方法,同時其也是Python的擴展包,使得整個開發過程僅使用一種Python語言,并可以很方便地將一個軟件算法快速地轉換為其相應的硬件實現,從而完成一個軟硬件系統設計.由于Python目前的可綜合子集的限制和其本身還處在發展階段,基于Python的軟硬件設計還主要用于系統的建模方面,將其用于芯片設計的應用還不是很多,有研究者比較過MyHDL與傳統硬件設計語言的實現,對于小規模的應用優勢不是很明顯.但是隨著現代系統的算法越來越復雜性,系統規模也不斷增大,相對于傳統的軟硬件設計方法采用Python來進行軟硬件協同設計的優勢就會體現出來,系統設計.仿真.校驗的速度會大大提高,采用Python進行系統設計的產品能更快地進入市場.隨著基于Python系統設計方法和工具的發展,基于Python的軟硬件協同設計方法將會有廣泛的應用前景.

-

編程語言

+關注

關注

10文章

1955瀏覽量

36235 -

C++

+關注

關注

22文章

2117瀏覽量

74840 -

python

+關注

關注

56文章

4825瀏覽量

86318

發布評論請先 登錄

基于FPGA的軟硬件協同仿真加速技術

基于EDA 的嵌入式系統軟硬件劃分方法

基于SOC的USB主設備的軟硬件協同驗證

基于軟硬件協同設計的低功耗生理信號處理ASIC設計

面向HDTV應用的音頻解碼軟硬件協同設計

可測性DSP軟硬件協同仿真驗證平臺設計

利用FPGA軟硬件協同系統驗證SoC系統的過程和方法

基于Python軟硬件協同設計方法,仿真和校驗的流程介紹

基于Python軟硬件協同設計方法,仿真和校驗的流程介紹

評論