隨著電子技術(shù)的迅速發(fā)展,高速信號(hào)觸發(fā)源已經(jīng)廣泛應(yīng)用于通訊、雷達(dá)等各種電子系統(tǒng)的測(cè)試和精確控制中。這就要求有一個(gè)穩(wěn)定性好、納秒上升沿、可控的脈沖發(fā)生器。但是,國內(nèi)至今還沒有合乎這些要求的商用脈沖發(fā)生器。即使在國際上普遍使用的加拿大生產(chǎn)的AVI-N型脈沖發(fā)生器也存在著幅度小、重復(fù)率低、易損壞等缺點(diǎn)。針對(duì)此現(xiàn)狀,設(shè)計(jì)一款高速脈沖信號(hào)發(fā)生器是非常有意義的。可編程邏輯器件(PLD)經(jīng)歷了PAL,GAL,CPLD和FPGA幾個(gè)發(fā)展階段,技術(shù)日趨成熟。采用VHDL語言對(duì)PLD進(jìn)行編程設(shè)計(jì)具有更改靈活、調(diào)試方便、操作性強(qiáng)、系統(tǒng)可靠性高等眾多優(yōu)點(diǎn),并有利于硬件設(shè)計(jì)的保護(hù),防止他人對(duì)電路的分析、仿照。因此,利用PLD器件為核心構(gòu)造高速脈沖信號(hào)發(fā)生器是一種有效的方法。

1 基本原理

設(shè)計(jì)采用的XILINX公司的復(fù)雜可編程邏輯器件(CPLD)幾乎可適用于所有的門陣列和各種規(guī)模的數(shù)字集成電路,他以其編程方便、集成度高、速度快、價(jià)格低等特點(diǎn)越來越受到設(shè)計(jì)者的歡迎。選用的CPLD為XILINX公司的XC9572XL,屬于XC9500系列,是目前業(yè)界速度較快的高集成度可編程邏輯器件。

CPLD開發(fā)軟件用ISE 6.0+ModelSim 5.7SE,該軟件是一個(gè)完全集成化、易學(xué)易用的可編程邏輯設(shè)計(jì)環(huán)境,并且廣泛支持各種硬件描述語言。他還具有與結(jié)構(gòu)無關(guān)性、多平臺(tái)運(yùn)行、豐富的設(shè)計(jì)庫和模塊化的工具等許多功能特點(diǎn)。

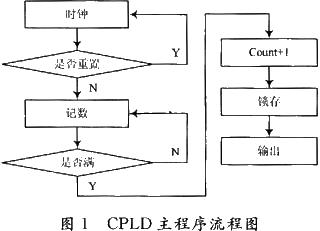

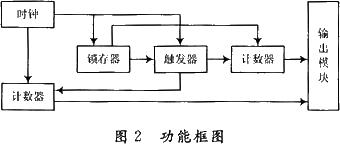

CPLD主程序流程圖如圖1所示,時(shí)針信號(hào)是整個(gè)程序的關(guān)鍵,通過時(shí)鐘對(duì)各個(gè)模塊進(jìn)行精確控制,實(shí)現(xiàn)基本功能。時(shí)鐘信號(hào)的精準(zhǔn)度決定了輸出脈沖信號(hào)的精準(zhǔn)度。時(shí)鐘源采用了4腳晶振,可以輸出一個(gè)穩(wěn)定的時(shí)鐘信號(hào)。CPLD內(nèi)部電路資源分配如圖2所示。

時(shí)鐘信號(hào)和復(fù)位信號(hào)作為輸入信號(hào),控制脈沖信號(hào)的輸出。系統(tǒng)分4個(gè)模塊,包括計(jì)數(shù)器、鎖存器、觸發(fā)器和數(shù)據(jù)輸出模塊。時(shí)鐘信號(hào)和復(fù)位信號(hào)分別加在計(jì)數(shù)器和觸發(fā)器上,計(jì)數(shù)器計(jì)數(shù)通過鎖存,在時(shí)鐘信號(hào)作用下同步觸發(fā)輸出信號(hào)。當(dāng)復(fù)位信號(hào)到來時(shí),計(jì)數(shù)器重新清零計(jì)數(shù)。

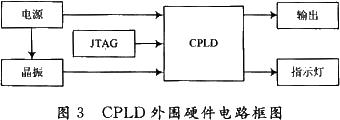

當(dāng)時(shí)鐘的上升沿到來時(shí)對(duì)高頻時(shí)鐘進(jìn)行計(jì)數(shù),CPLD內(nèi)部建立一個(gè)5位計(jì)數(shù)器,計(jì)數(shù)器滿后自動(dòng)重置為0,輸出端把計(jì)數(shù)器的各位進(jìn)行輸出,計(jì)數(shù)器滿后也輸出一個(gè)高電平。第一級(jí)輸出端一共有7個(gè),可以實(shí)現(xiàn)對(duì)時(shí)鐘的2,4,8,16,32,64分頻以及單脈沖輸出。在CPLD內(nèi)部再建立一個(gè)3位計(jì)數(shù)器,對(duì)前級(jí)4分頻信號(hào)再做計(jì)數(shù),調(diào)節(jié)占空比,控制脈沖輸出,同時(shí)對(duì)一級(jí)分頻信號(hào)進(jìn)行相與輸出。設(shè)置一個(gè)復(fù)位端,當(dāng)高電平時(shí)候,對(duì)電路進(jìn)行復(fù)位,計(jì)數(shù)器重新開始工作。通過復(fù)位端可以很好地控制脈沖輸出,并且輸出信號(hào)脈沖寬度在不同的分頻接口可以得到不同的脈沖寬度信號(hào),也可以通過修改程序?qū)崿F(xiàn)脈沖寬度的改變。CPLD外圍硬件電路包括了電源、晶振、輸出端口、指示燈,如圖3所示。

本設(shè)計(jì)選用的外部計(jì)數(shù)時(shí)鐘頻率為100 MHz,因此所產(chǎn)生脈沖的周期最小是10 ns,脈寬調(diào)節(jié)最小為5 ns,調(diào)節(jié)步長(zhǎng)為5 ns。該脈沖發(fā)生器可以實(shí)現(xiàn)多路輸出,脈沖輸出共有9路,其中1路可以實(shí)現(xiàn)單脈沖輸出,其余8路可以輸出不同脈寬的納秒級(jí)脈沖。若要提高脈沖發(fā)生器的精度,應(yīng)提高計(jì)數(shù)時(shí)鐘的頻率。同時(shí)選用速度等級(jí)更高的PLD。若要增加脈沖周期及脈寬的可調(diào)范圍,則應(yīng)選用容量更大的PLD。

2 仿真驗(yàn)證

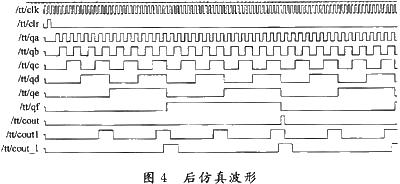

仿真是驗(yàn)證設(shè)計(jì)的一個(gè)重要環(huán)節(jié),如果仿真沒有通過,設(shè)計(jì)就必須重來,以便硬件調(diào)試的勝利通過。在ISE中,建立仿真文件并調(diào)用ModelSim 6.0對(duì)設(shè)計(jì)進(jìn)行行為仿真。在第2個(gè)脈沖到來時(shí)進(jìn)行計(jì)數(shù)器置零,開始計(jì)數(shù),對(duì)每個(gè)輸出端口的波形都進(jìn)行仿真測(cè)試。從仿真波形中可以預(yù)測(cè)出,可編程器件成功地對(duì)脈沖進(jìn)行控制,然后分頻輸出,達(dá)到預(yù)定的要求。

行為仿真只是對(duì)VHDL語言進(jìn)行邏輯綜合后仿真,布局布線后仿真則是在具體器件和硬件資源分配后,利用從布局布線中提取的一些信息,其中包括了目標(biāo)器件及互連線的時(shí)延、電阻、電容等信息,并考慮走線之間的相互影響后產(chǎn)生的仿真波形。圖4是布局布線后仿真圖,可以看到在CLR信號(hào)有效開始,輸出端經(jīng)過4個(gè)周期的延遲后才響應(yīng)到有效的復(fù)位信號(hào),這個(gè)說明器件延時(shí)加上互連線延時(shí)為4個(gè)周期,但是這并不影響設(shè)計(jì)輸出脈沖的質(zhì)量,在其他電子設(shè)計(jì)中卻要考慮到這個(gè)延遲。

3 試驗(yàn)結(jié)果

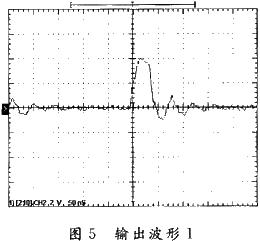

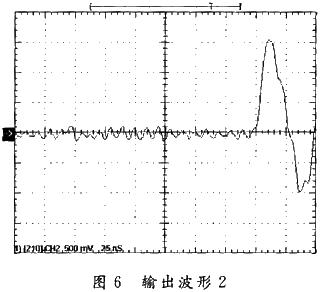

做好電路版,調(diào)試程序成功后,用型號(hào)為TektronixTDS210示波器測(cè)出兩個(gè)端口的輸出波形如圖5和圖6所示。圖5中波形幅度為3.98 V,峰峰值為4.98 V,脈沖寬度為37.8 ns,上升沿為16.7 ns;圖6波形幅度為1.53 V,峰峰值為2.51 V,脈沖寬度為19.8 ns,上升沿為9.7 ns。在示波器中顯示,得到納秒脈沖信號(hào)非常穩(wěn)定,可以作為一個(gè)穩(wěn)定的納秒信號(hào)源。每個(gè)脈沖過后都有一個(gè)小的負(fù)脈沖,并且上升沿和下降沿并沒有像仿真時(shí)短,主要原因是:一是仿真在一個(gè)相對(duì)理想的條件下進(jìn)行的,對(duì)器件資源在電路中的實(shí)際體積忽略;二是芯片的微加工制造工藝不精確,寄生電容電阻的大小沒有精確計(jì)算,可以在輸出端加電容接地減小過脈沖。

4 結(jié) 語

本文利用XILINX公司的復(fù)雜可編程邏輯器件,結(jié)合VHDL語言,提出了一種可控納秒級(jí)脈沖信號(hào)發(fā)生器的設(shè)計(jì)方法,并且通過仿真驗(yàn)證,得到脈沖寬度最小為19.8 ns,上升沿為9.7 ns的脈沖。在千伏高壓納秒脈沖發(fā)生系統(tǒng)中,采用MOS管、二極管、脈沖形成線等作為核心器件,該信號(hào)源必不可少的要一個(gè)觸發(fā)源。利用可控高速信號(hào)發(fā)生器作為觸發(fā)源,可以有效地實(shí)現(xiàn)對(duì)千伏高壓的精確控制。在高速數(shù)字系統(tǒng)中,數(shù)據(jù)在器件間的串行傳輸速率可以達(dá)到幾百M(fèi)b/s。此時(shí),由于時(shí)鐘周期非常小(通常只有幾納秒),為了保證高速數(shù)據(jù)的可靠接收,數(shù)據(jù)與時(shí)鐘的相對(duì)位置要求非常嚴(yán)格,以避免發(fā)生數(shù)據(jù)的錯(cuò)位或在數(shù)據(jù)變化邊沿對(duì)數(shù)據(jù)采樣,亦可采用該多路高速信號(hào)發(fā)生器。簡(jiǎn)便可靠的納秒信號(hào)發(fā)生器在電子系統(tǒng)設(shè)計(jì)中將越來越具有使用價(jià)值。

-

PLD

+關(guān)注

關(guān)注

6文章

230瀏覽量

59504 -

vhdl

+關(guān)注

關(guān)注

30文章

817瀏覽量

128346 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

517瀏覽量

44184

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

求一份利用PLD構(gòu)造高速脈沖信號(hào)發(fā)生器的方案

Rogowski線圈信號(hào)電阻對(duì)納秒級(jí)脈沖大電流的響應(yīng)

基于SoPC的脈沖發(fā)生器

延時(shí)可控高壓脈沖發(fā)生器的設(shè)計(jì)

基于ECL門電路的UWB信號(hào)發(fā)生器的設(shè)計(jì)

納秒級(jí)高壓頻率脈沖發(fā)生器的實(shí)現(xiàn)

采用VHDL語言和PLD的可控納秒級(jí)脈沖信號(hào)發(fā)生器的設(shè)計(jì)

采用VHDL語言和PLD的可控納秒級(jí)脈沖信號(hào)發(fā)生器的設(shè)計(jì)

評(píng)論