Petri網(wǎng)是離散事件系統(tǒng)建模的重要工具,本文使用硬件描述語(yǔ)言VHDL實(shí)現(xiàn)了基于Petri網(wǎng)的并行控制器。文中通過(guò)一個(gè)液位控制系統(tǒng)實(shí)例具體介紹了這一方法,并通過(guò)仿真波形證明了該方法的正確性。這對(duì)于離散事件系統(tǒng)并行控制器的設(shè)計(jì)具有十分重要的意義。

Petri網(wǎng)是異步并發(fā)系統(tǒng)建模與分析的一種重要工具,1962年由德國(guó)科學(xué)家C.A.Petri博士創(chuàng)立。40多年來(lái),Petri網(wǎng)理論得到了很大的豐富和發(fā)展,其應(yīng)用領(lǐng)域也在不斷擴(kuò)大,越來(lái)越受到國(guó)際同行的重視,已成為計(jì)算機(jī)、自動(dòng)化和通信領(lǐng)域的熱門(mén)研究課題。Petri網(wǎng)既有直觀的圖形表示,又有深厚的數(shù)學(xué)基礎(chǔ);既是層次化的結(jié)構(gòu)模型,又能反映系統(tǒng)的動(dòng)態(tài)性能。用硬件描述語(yǔ)言進(jìn)行電路和系統(tǒng)設(shè)計(jì)是當(dāng)前EDA技術(shù)的重要特征,它使得設(shè)計(jì)者能在較抽象的層次上進(jìn)行系統(tǒng)結(jié)構(gòu)和內(nèi)部特征的設(shè)計(jì)。VHDL作為一種高速的硬件描述語(yǔ)言適于描述設(shè)計(jì)異步并發(fā)的系統(tǒng),因而可與Petri網(wǎng)模型建立聯(lián)系。用VHDL對(duì)模型進(jìn)行程序設(shè)計(jì),為模型的硬件實(shí)現(xiàn)奠定了基礎(chǔ)。隨著大規(guī)模、高密度的可編程邏輯器件FPGA和CPLD的問(wèn)世與應(yīng)用方面的迅速推廣,并且有各種EDA軟件工具的支持,使得人們可以根據(jù)Petri網(wǎng)的拓?fù)浣Y(jié)構(gòu)用硬件加以實(shí)現(xiàn),以使Petri網(wǎng)的硬件實(shí)現(xiàn)成為可能。因此,基于Petri網(wǎng)的智能化的并行控制器的設(shè)計(jì)與硬件實(shí)現(xiàn)的課題引起了人們的強(qiáng)烈興趣。利用Petri網(wǎng)技術(shù),不僅可以用來(lái)進(jìn)行設(shè)計(jì)、分析和驗(yàn)證,還能夠進(jìn)行優(yōu)化控制。

微電子技術(shù)發(fā)展到今天,已提供了幾千至幾千萬(wàn)個(gè)標(biāo)準(zhǔn)門(mén)的芯片。特別是在系統(tǒng)可編程技術(shù),可有條件地在一個(gè)芯片上設(shè)計(jì)制作一個(gè)數(shù)字系統(tǒng),即系統(tǒng)芯片(System on Chip,SoC)。國(guó)內(nèi)市場(chǎng)上常見(jiàn)的Altera公司、Xilinx公司、Lattice公司的FPGA和CPLD芯片,一般都能滿(mǎn)足設(shè)計(jì)SoC的需要,并且都提供了EDA軟件開(kāi)發(fā)工具。而且在現(xiàn)有的軟件開(kāi)發(fā)工具中,有電路圖、狀態(tài)圖、真值表和硬件描述語(yǔ)言等輸入方式。但設(shè)計(jì)片上并行控制器,難以用電路圖或邏輯方程輸入方式實(shí)現(xiàn);如果用狀態(tài)圖或真值表輸入方式,隨著問(wèn)題復(fù)雜程度的增加,系統(tǒng)的狀態(tài)將發(fā)生組合爆炸,這是十分棘手的問(wèn)題。而且有限狀態(tài)機(jī)(FSM)雖已被廣泛運(yùn)用到數(shù)字邏輯控制系統(tǒng),也只是因?yàn)樗o出了系統(tǒng)化的硬件實(shí)現(xiàn)方法和具體的實(shí)現(xiàn)模型(如Moore自動(dòng)機(jī)和Mealy自動(dòng)機(jī)),用FSM實(shí)現(xiàn)并行控制器也十分困難。因?yàn)镕SM必須于設(shè)計(jì)前劃分控制器,所以常常會(huì)導(dǎo)致非最優(yōu)的門(mén)級(jí)實(shí)現(xiàn),且使設(shè)計(jì)中并發(fā)的數(shù)量受到使用FSM數(shù)量的限制,同時(shí)FSM間相互依賴(lài),使得設(shè)計(jì)難于驗(yàn)證且易產(chǎn)生并行同步錯(cuò)誤(如死鎖、丟失數(shù)據(jù)的完整性)。上述這些缺點(diǎn)只有設(shè)計(jì)遍歷整個(gè)狀態(tài)空間時(shí)才能驗(yàn)證,因而可能被漏檢。若用硬件描述語(yǔ)言輸入,遇到的困難是模型和驗(yàn)證。

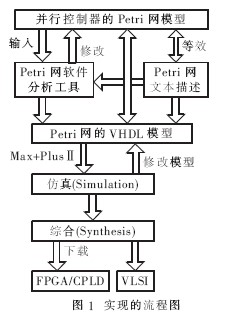

針對(duì)傳統(tǒng)的設(shè)計(jì)方法不太適合并行控制器設(shè)計(jì)的問(wèn)題,本文介紹一種使用硬件描述語(yǔ)言VHDL來(lái)實(shí)現(xiàn)基于Petri網(wǎng)的并行控制器的方法。首先使用Petri網(wǎng)對(duì)問(wèn)題進(jìn)行建模,并對(duì)模型進(jìn)行分析和控制,獲得控制器的Petri網(wǎng)模型;然后用VHDL對(duì)Petri網(wǎng)控制模型加以描述,得到源文件;最后通過(guò)EDA軟件開(kāi)發(fā)工具M(jìn)ax+PlusⅡ進(jìn)行編譯、模擬、適配,并下載到可編程邏輯器件中。

1 Petri網(wǎng)簡(jiǎn)介

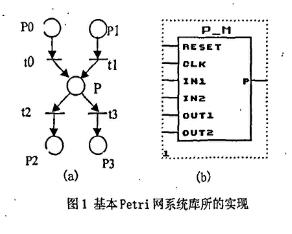

2 實(shí)現(xiàn)的基本方法

Petri網(wǎng)本身就是一種硬件描述語(yǔ)言,是一種高度抽象的、結(jié)構(gòu)化的并發(fā)語(yǔ)言。Petri網(wǎng)非常適合于復(fù)雜離散系統(tǒng)的建模和形式化分析,而VHDL則是一種標(biāo)準(zhǔn)的硬件描述語(yǔ)言,可以解決數(shù)字系統(tǒng)描述中并發(fā)性問(wèn)題,允許其仿真和綜合。Petri網(wǎng)和VHDL可以相互補(bǔ)充,并且也可以提供一個(gè)驗(yàn)證子系統(tǒng)接收所有設(shè)計(jì)任務(wù)相同的用戶(hù)接口描述。并行控制器的VHDL文本Petri網(wǎng)描述在一個(gè)實(shí)際設(shè)計(jì)中可獲得50%的面積減少及40%的速度改善(相對(duì)于最好的FSM綜合)。

用大規(guī)模可編程邏輯器件來(lái)實(shí)現(xiàn)由Petri網(wǎng)描述的并行控制器,其實(shí)現(xiàn)的基本步驟如下:

(1)對(duì)實(shí)際系統(tǒng)建立Petri網(wǎng)系統(tǒng)模型。

(2)采用Petri網(wǎng)軟件工具對(duì)所建立的Petri網(wǎng)系統(tǒng)模型進(jìn)行分析并加以控制,建立監(jiān)控器的Petri網(wǎng)系統(tǒng)模型。

(3)確定輸入輸出變量并選擇相應(yīng)的FPGA或CPLD器件。

(4)根據(jù)網(wǎng)的拓?fù)浣Y(jié)構(gòu)確定條件與事件間的邏輯關(guān)系,用硬件描述語(yǔ)言如VHDL對(duì)Petri網(wǎng)模型進(jìn)行描述。

(5)以VHDL描述作為設(shè)計(jì)輸入,通過(guò)EDA軟件開(kāi)發(fā)工具,如ispDesign EXPERT或Max+PlusⅡ等,進(jìn)行編譯、模擬、適配,然后下載到器件中。

整個(gè)硬件實(shí)現(xiàn)的流程圖如圖1所示。

3 基于Petri網(wǎng)的并行控制器設(shè)計(jì)舉例

3.1 系統(tǒng)描述

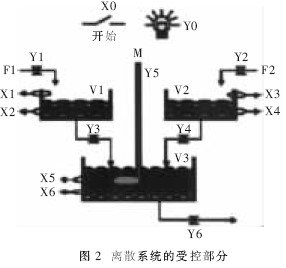

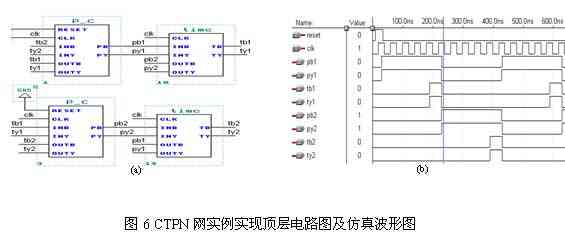

從文獻(xiàn)中選擇了一個(gè)如圖2所示的并行控制器設(shè)計(jì)例子,這是一個(gè)用于說(shuō)明離散事件系統(tǒng)控制器設(shè)計(jì)的典型示例。它有3個(gè)盛放液體的罐子:V1、V2、V3,其中V1、V2是用來(lái)盛放不同種液體F1、F2的,M是攪拌系統(tǒng)的驅(qū)動(dòng)電機(jī)。系統(tǒng)停止時(shí),指示燈Y0亮。當(dāng)起動(dòng)按鈕按下時(shí)(X0=1),閥Y1、Y2打開(kāi),2種不同的液體F1、F2分別注入V1、V2。當(dāng)V1中的液體到達(dá)X1位置時(shí),Y1關(guān)閉;當(dāng)V2中液體到達(dá)X3時(shí),閥Y2關(guān)閉。當(dāng)V1、V2中的液體分別都到達(dá)X1、X3時(shí),Y3、Y4同時(shí)打開(kāi);當(dāng)V1、V2中液體分別都低于X2、X4時(shí),Y3、Y4關(guān)閉,同時(shí)Y6打開(kāi)。當(dāng)V3中液體高于X5時(shí),Y5閉合,電動(dòng)機(jī)M開(kāi)始攪拌;當(dāng)V3中液體流出低于X6時(shí),Y6關(guān)閉,指示燈亮,重新回到原來(lái)狀態(tài)。

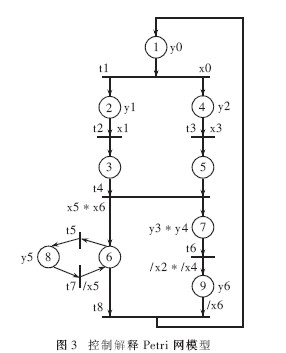

3.2 系統(tǒng)控制部分的控制解釋Petri網(wǎng)模型

用Petri網(wǎng)對(duì)系統(tǒng)控制部分進(jìn)行描述,得到的控制解釋Petri網(wǎng)模型如圖3所示。模型中輸入輸出信號(hào)的描述如表1所示,描述的局部狀態(tài)如表2所示。

3.3 模型的VHDL實(shí)現(xiàn)

用VHDL實(shí)現(xiàn)的部分源代碼如下:

t1<=not p2 and not p4 and x0 and p1;

t2<=not p3 and x1 and p2;

t3<=not p5 and x3 and p4;

t4<=not p6 and not p7 and p3 and p5;

t5<=not p8 and x5 and x6 and p6;

t6<=not p9 and not x2 and not x4 and p7;

t7<=not p6 and not x5 and p8;

t8<=not p1 and not x6 and p6 and p9;

np1<=t8 or (p1 and not t1);

np2<=t1 or (p2 and not t2);

np3<=t2 or (p3 and not t4);

np4<=t1 or (p4 and not t3);

np5<=t3 or (p5 and not t4);

np6<=t4 or t7 or(p6 and not t5 and not t8);

np7<=t4 or (p7 and not t6);

np8<=t5 or (p8 and not t7);

np9<=t6 or (p9 and not t8);

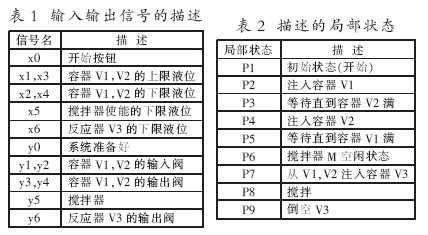

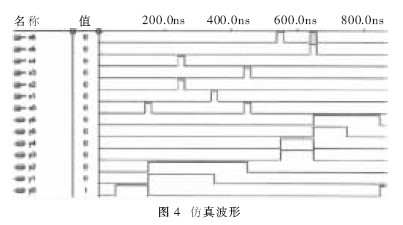

3.4 基于Max+PlusⅡ的并行控制器仿真

在MAX+PlusⅡ中經(jīng)編譯后進(jìn)行功能仿真,仿真波形如圖4所示。波形表明結(jié)果是正確的。

4 結(jié) 論

Petri網(wǎng)是并發(fā)系統(tǒng)強(qiáng)有力的建模工具,通過(guò)對(duì)Petri網(wǎng)模型的分析,可以獲得系統(tǒng)的許多結(jié)構(gòu)和動(dòng)態(tài)性能,根據(jù)控制策略,還可以建立系統(tǒng)的控制模型并獲得系統(tǒng)在控制作用下的性能。以上討論證明,基于Petri網(wǎng)的并行控制器可以用VHDL實(shí)現(xiàn),從而開(kāi)辟了并行控制器設(shè)計(jì)與實(shí)現(xiàn)的新途徑。

-

控制器

+關(guān)注

關(guān)注

114文章

16984瀏覽量

183021 -

soc

+關(guān)注

關(guān)注

38文章

4348瀏覽量

221769 -

vhdl

+關(guān)注

關(guān)注

30文章

819瀏覽量

129584

發(fā)布評(píng)論請(qǐng)先 登錄

怎么實(shí)現(xiàn)并行控制器?

幾種Petri網(wǎng)系統(tǒng)的硬件實(shí)現(xiàn)方案

怎么實(shí)現(xiàn)PID控制器的VHDL-AMS行為級(jí)建模

使用VHDL的Petri網(wǎng)系統(tǒng)的FPGA實(shí)現(xiàn) 同步Petri

VHDL語(yǔ)言實(shí)現(xiàn)DDR2 SDRAM控制

FM收音機(jī)的解碼及控制器VHDL語(yǔ)言實(shí)現(xiàn)

基于FPGA的PCIe總線接口的DMA控制器的實(shí)現(xiàn)并進(jìn)行仿真驗(yàn)證

VHDL-AMS的特性、仿真分析與在控制系統(tǒng)中的應(yīng)用

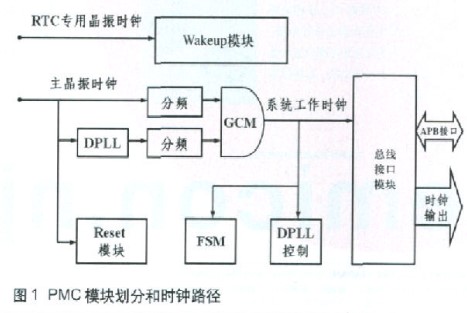

采用硬件描述語(yǔ)言實(shí)現(xiàn)PMC時(shí)鐘功耗管理控制器的設(shè)計(jì)

基于FPGA的Petri網(wǎng)的硬件實(shí)現(xiàn)

基于VHDL語(yǔ)言和可編程邏輯器件實(shí)現(xiàn)Petri網(wǎng)邏輯控制器的設(shè)計(jì)

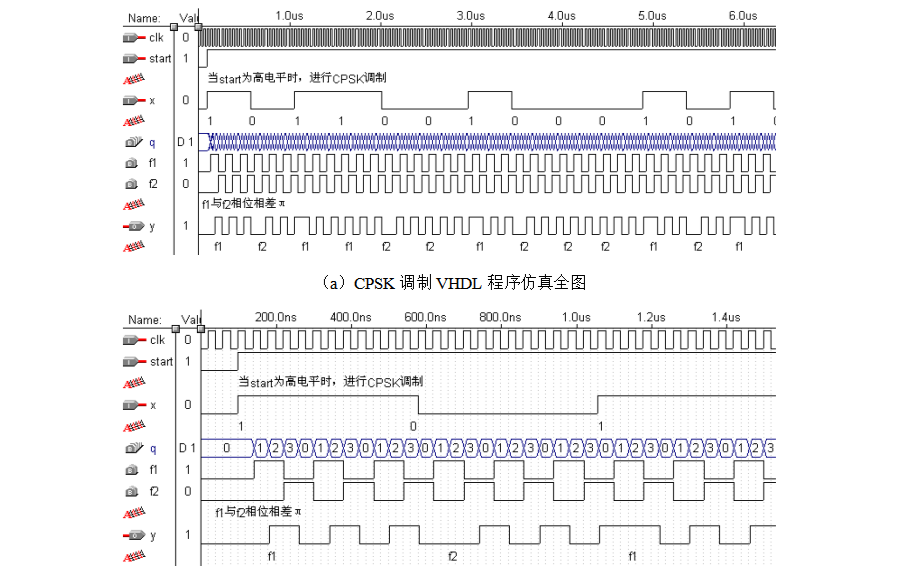

基于VHDL硬件描述語(yǔ)言實(shí)現(xiàn)CPSK調(diào)制的程序及仿真

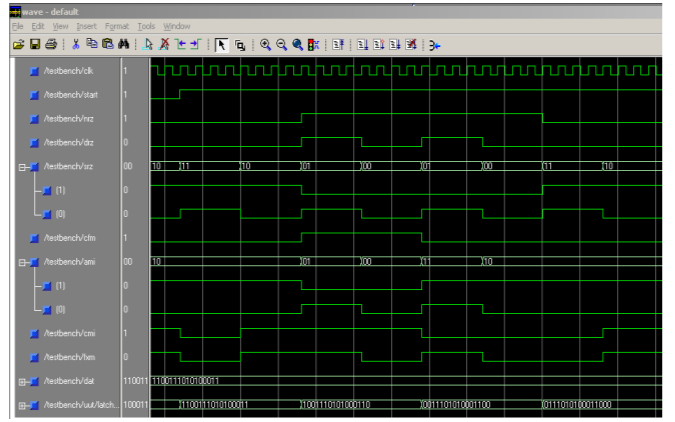

使用VHDL硬件描述語(yǔ)言實(shí)現(xiàn)基帶碼發(fā)生器的程序設(shè)計(jì)與仿真

一種基于Petri網(wǎng)的并行控制器的VHDL實(shí)現(xiàn)

采用VHDL預(yù)言實(shí)現(xiàn)基于Petri網(wǎng)的并行控制器設(shè)計(jì)并進(jìn)行仿真驗(yàn)證

采用VHDL預(yù)言實(shí)現(xiàn)基于Petri網(wǎng)的并行控制器設(shè)計(jì)并進(jìn)行仿真驗(yàn)證

評(píng)論