1 、引言

隨著微電子技術(shù)的迅速發(fā)展,人們對(duì)數(shù)字系統(tǒng)的需求也在提高。不僅要有完善的功能,而且對(duì)速度也提出了很高的要求。對(duì)于大部分?jǐn)?shù)字系統(tǒng),都可以劃分為控制單元和數(shù)據(jù)單元兩個(gè)組成部分。通常,控制單元的主體是一個(gè)有限狀態(tài)機(jī),它接收外部信號(hào)以及數(shù)據(jù)單元產(chǎn)生的狀態(tài)信息,產(chǎn)生控制信號(hào)序列。MOORE型有限狀態(tài)機(jī)的設(shè)計(jì)方法有多種,采用不同的設(shè)計(jì)方法,雖然可以得到相同功能的狀態(tài)機(jī),但它們的速度、時(shí)延特性、占用資源可能有較大的差異。在某些對(duì)速度要求很高的場(chǎng)合,如內(nèi)存控制器,則需要針對(duì)速度進(jìn)行優(yōu)化設(shè)計(jì)。

2 、MOORE型有限狀態(tài)機(jī)的幾種設(shè)計(jì)方法

2.1 輸出由狀態(tài)位經(jīng)組合譯碼得到

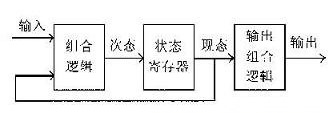

它的實(shí)現(xiàn)方案是:現(xiàn)態(tài)與輸入信號(hào)經(jīng)組合邏輯得到次態(tài),在時(shí)鐘的上升沿到來時(shí),狀態(tài)寄存器將次態(tài)鎖存得到現(xiàn)態(tài),現(xiàn)態(tài)經(jīng)過輸出組合邏輯譯碼得到輸出信號(hào)。如圖 1所示。由于輸出必須由現(xiàn)態(tài)的狀態(tài)位經(jīng)過譯碼得到,這就需要在現(xiàn)態(tài)與輸出之間增加一級(jí)組合譯碼邏輯,從而加大了從狀態(tài)位到器件輸出管腳的傳輸延遲,同樣也增加了時(shí)鐘-輸出時(shí)延TCO。

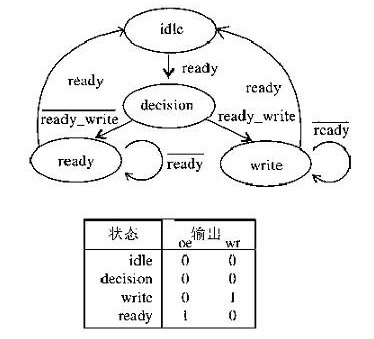

假設(shè)一個(gè)簡(jiǎn)單的內(nèi)存控制器的狀態(tài)轉(zhuǎn)換圖如圖2所示。一個(gè)完整的讀寫周期是從空閑狀態(tài)idle開始。在ready信號(hào)有效之后的下一個(gè)時(shí)鐘周期轉(zhuǎn)移到判斷狀態(tài)decision,然后根據(jù)read_write信號(hào)再轉(zhuǎn)移到read或write狀態(tài)。則采用這種設(shè)計(jì)方法的VHDL源程序如下:

signalpresent_state,next_state:std_logic_vector(1 downto 0);

process(clk,ready,read_write,present_state)

begin

if(clk‘eventandclk=’1‘)then

casepresent_stateis

when idle=>oe<=’0‘;wr<=’0‘;

if ready=’1‘ then

next_state<=decision;

else next_state<=idle;

endif;

when decision=>oe<=’0‘;wr<=’0‘;

if(read_write=’1‘)then

next_state<=read;

else next_state<=write;

endif;

when read=>oe<=’1‘;wr<=’0‘;

if(ready=’1‘)then

next_state<=idle;

else next_state<=read;

endif;

when others=>oe<=’0‘;wr<=’1‘;

if(ready=’1‘)then next_state<=idle;

else next_state<=write;

endif;

endcase;endif;

endprocess;

state_clock:process(clk)begin

if(clk’eventandclk=‘1’)then

present_state<=next_state;

endif;

endprocess;

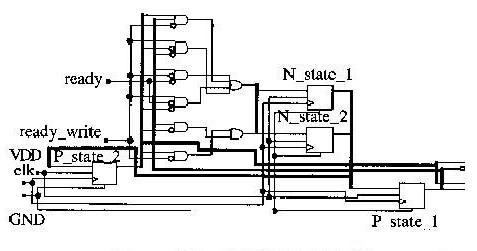

對(duì)此程序綜合出的電路如圖3所示。現(xiàn)態(tài)present_state與次態(tài)next_state均由兩個(gè)觸發(fā)器構(gòu)成,輸出wr和oe均由 present_state經(jīng)組合譯碼得到,因此從時(shí)鐘的上升沿到狀態(tài)機(jī)輸出的延遲為通過邏輯陣列的時(shí)鐘-輸出時(shí)延TCO2,而不是較短的時(shí)鐘-輸出時(shí)延 TCO,且輸出信號(hào)wr,oe直接來自組合邏輯電路,因而可能有毛刺發(fā)生。

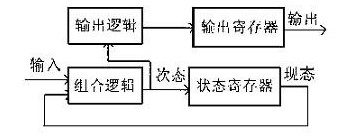

2.2 輸出由并行輸出寄存器譯碼得到

在第一種方法中,主要由于輸出組合邏輯引入了延時(shí),從而加大了時(shí)鐘-輸出時(shí)延。為了縮短狀態(tài)機(jī)輸出到達(dá)管腳的延時(shí),可以在鎖存狀態(tài)位之前,先進(jìn)行輸出的組合邏輯譯碼并將其鎖存到專用寄存器中,時(shí)鐘上升沿到來時(shí),專用寄存器中直接輸出wr和oe而沒有了組合邏輯引入的延時(shí),從而使?fàn)顟B(tài)機(jī)輸出的延遲為TCO。實(shí)現(xiàn)該方案的方框圖如圖4。采用這種設(shè)計(jì)方法的VHDL源程序如下:

signalpresent_state:std_logic_vector(1 downto 0);

signalnext_state:std_logic_vector(1 downto 0);

signalwr_d,oe_d:std_logic;

begin

process(clk,ready,read_write)

begin

if(clk‘event and clk=’1‘)then

case present_stateis

when idle=>

if ready=’1‘thennext_state<=decision;

else next_state<=idle;

endif ;

when decision=>

if(read_write=’1‘) then next_state<=read;

else next_state<=write;

endif;

when read=>

if(ready=’1‘)then

next_state<=idle;

else next_state<=read;

endif;

when others=>

if(ready=’1‘)then

next_state<=idle;

else next_state<=write;

endif;

endcase;

endif;

endprocess;

withnext_stateselect

oe_d<=’0‘ whenidle|decision|write,’1‘when others;

withnext_stateselect

wr_d<=’0‘whenidle|decision|read,’1‘when others;

state_clock:process(clk)

begin

if(clk’eventandclk=‘1’)then

present_state<=next_state;

oe<=oe_d;

wr<=wr_d;

endif;

endprocess;

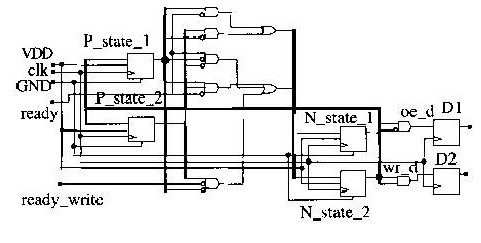

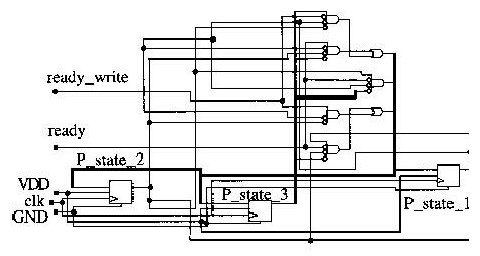

在此程序中,用到了兩個(gè)新的信號(hào)oe_d和wr_d,對(duì)次態(tài)next_state進(jìn)行鎖存,不象第一種方案中將現(xiàn)態(tài)present_state進(jìn)行譯碼從而得到在下一個(gè)時(shí)鐘周期oe和wr的取值。對(duì)此程序綜合出的電路如圖5所示。oe_d和wr_d作為鎖存器D1和D2的輸入。因此D1、D2的輸出為上一個(gè)次態(tài)(即現(xiàn)態(tài))的值。clk的上升沿到來時(shí),D1、D2即將oe_d和wr_d鎖存,從而得輸出oe和wr。因此從時(shí)鐘的上升沿到狀態(tài)機(jī)輸出的延遲為時(shí)鐘-輸出時(shí)延TCO而不是通過邏輯陣列的時(shí)鐘-輸出時(shí)延TCO2。又由于時(shí)鐘信號(hào)將輸出加載到附加的D觸發(fā)器中,因而消除了輸出信號(hào)的毛刺。然而,這種方法存在兩個(gè)缺點(diǎn):(1)由于用到了輸出寄存器,它比第一種設(shè)計(jì)需要多用兩個(gè)寄存器;(2)雖然它的時(shí)鐘-輸出時(shí)延從TCO2減小到TCO,但從狀態(tài)機(jī)的狀態(tài)位到達(dá)oe和wr需要經(jīng)過兩級(jí)組合邏輯,這就影響了系統(tǒng)時(shí)鐘的最高頻率。

2.3 輸出直接從狀態(tài)位得到

為了能夠把時(shí)鐘-輸出時(shí)延限制在TCO內(nèi),也可以將狀態(tài)位本身作為輸出信號(hào)。對(duì)于狀態(tài)位不是很多的狀態(tài)機(jī)而言,這種方法也許較前兩種更為優(yōu)越。某種情況下,可能會(huì)出現(xiàn)兩種不同狀態(tài)有相同的狀態(tài)位,此時(shí)只需增加一位狀態(tài)位加以區(qū)別即可。如此程序中,idle、decision、read、write四種狀態(tài)可分別編碼為000,001,100,010。采用這種方法所對(duì)應(yīng)的程序如下:

signalpresent_state:std_logic_vector(2downto0);

state:process(clk,ready,read_write);

begin

if(clk‘eventandclk=’1‘)then

case present_stateis

when “000”=>ifready=’1‘ then present_state<=“001”;

else present_state<=“000”;

endif;

when “001”=>if(read_write=’1‘) then

present_state<=“100”;

else present_state<=“001”;

endif;

when “100”=>if(ready=’1‘)then

present_state<=“000”;

elsepresent_state<=“100”;

endif;

when “010”=>if(ready=’1‘) then present_state<=“000”;

else present_state<=“010”;

endif;

when others=>present_state<=“---”;

endcase;

endif;

endprocess;

oe<=present_state(2);

wr<=present_state(1);

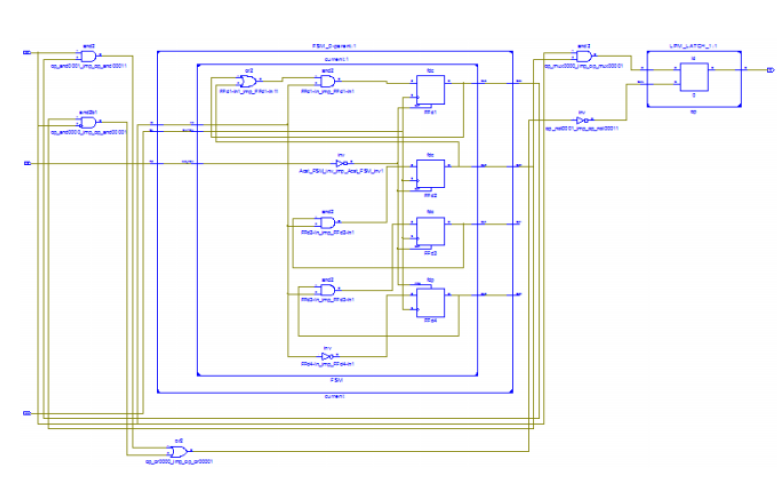

對(duì)此程序綜合出的電路如圖6所示。從圖中可知,輸出信號(hào)未通過額外的邏輯對(duì)現(xiàn)態(tài)進(jìn)行譯碼,而是直接來自狀態(tài)寄存器,因而輸出信號(hào)上沒有毛刺,并且它所用的宏單元少于通過并行輸出寄存器輸出的方式。

3 、結(jié)論

從以上分析可知,普通MOORE型狀態(tài)機(jī)時(shí)延最長,速度最慢,可應(yīng)用于對(duì)速度要求不高的場(chǎng)合。同時(shí),由于它的輸出信號(hào)中有毛刺,更加限制了它的應(yīng)用范圍。后兩種方案在相同的條件下,具有相同的時(shí)延,即速度是相同的,但第二 種方案所占用面積要比第三種大得多,且對(duì)時(shí)鐘頻率有一定限制。如果可能的話,選擇“輸出直接從狀態(tài)位得到”類型狀態(tài)機(jī)是一個(gè)理想的方案,因?yàn)槠渌俣茸羁欤娣e最小,設(shè)計(jì)這種狀態(tài)機(jī)時(shí),必須在VHDL源碼中對(duì)狀態(tài)的編碼加以明確的規(guī)定,使?fàn)顟B(tài)和輸出信號(hào)的取值一致。所以只有在狀態(tài)機(jī)的規(guī)模較小時(shí),才能很好地實(shí)現(xiàn)這種類型的設(shè)計(jì)。

-

控制器

+關(guān)注

關(guān)注

114文章

17059瀏覽量

183654 -

寄存器

+關(guān)注

關(guān)注

31文章

5432瀏覽量

124011 -

vhdl

+關(guān)注

關(guān)注

30文章

820瀏覽量

129775

發(fā)布評(píng)論請(qǐng)先 登錄

有限狀態(tài)機(jī)有什么類型?

MOORE型有限狀態(tài)機(jī)的幾種設(shè)計(jì)方法是什么

fsm有限狀態(tài)機(jī)pdf

有限狀態(tài)機(jī)的硬件描述語言設(shè)計(jì)方法

有限狀態(tài)機(jī)FSM在PLD中的實(shí)現(xiàn)分析

有限狀態(tài)機(jī)的建模與優(yōu)化設(shè)計(jì)

VHDL有限狀態(tài)機(jī)設(shè)計(jì)-ST

初學(xué)者對(duì)有限狀態(tài)機(jī)(FSM)的設(shè)計(jì)的認(rèn)識(shí)

狀態(tài)機(jī)和組合邏輯的冒險(xiǎn)競(jìng)爭(zhēng)淺析

如何使用FPGA實(shí)現(xiàn)序列檢測(cè)有限狀態(tài)機(jī)

基于事件驅(qū)動(dòng)的有限狀態(tài)機(jī)介紹

如何以面向?qū)ο蟮乃枷朐O(shè)計(jì)有限狀態(tài)機(jī)

基于事件驅(qū)動(dòng)的有限狀態(tài)機(jī)介紹

一個(gè)基于事件驅(qū)動(dòng)的有限狀態(tài)機(jī)

MOORE型有限狀態(tài)機(jī)的設(shè)計(jì)方案分析

MOORE型有限狀態(tài)機(jī)的設(shè)計(jì)方案分析

評(píng)論