DDS同 DSP(數(shù)字信號處理)一樣,是一項關(guān)鍵的數(shù)字化技術(shù)。DDS是直接數(shù)字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。與傳統(tǒng)的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉(zhuǎn)換時間等優(yōu)點,廣泛使用在電信與電子儀器領(lǐng)域,是實現(xiàn)設(shè)備全數(shù)字化的一個關(guān)鍵技術(shù)。DDS在結(jié)構(gòu)上由三部分構(gòu)成:⑴ 累加器;⑵ 角度幅度轉(zhuǎn)換器,它將數(shù)字相位值轉(zhuǎn)換為數(shù)字幅度值;⑶ 數(shù)模轉(zhuǎn)換器。ADI公司所有DDS的DAC都是電流輸出形式。DDS頻率規(guī)劃是指在應(yīng)用范圍內(nèi)提供最佳動態(tài)性能的一種嘗試,對于許多應(yīng)用來說,這就意味著在感興趣的帶寬內(nèi)提供最大的無雜散動態(tài)范圍,或者稱作SFDR.為了獲得最大的SFDR值,需要進行一些DDS頻率規(guī)劃。一個好的頻率規(guī)劃首先是要根據(jù)應(yīng)用所給定的性能標(biāo)準選擇合適的DDS器件,然后規(guī)劃并預(yù)算出DDS的主要雜散源

不同的應(yīng)用領(lǐng)域,對DDS的性能有不同的要求。當(dāng)把DDS用做雷達系統(tǒng)中的本振信號源時,對寄生信號抑制的要求可能比較高,如要求在60dB或70dB以上。當(dāng)把DDS用于雷達干擾系統(tǒng)時,除了對寄生信號抑制有一定的要求外,更重要的是其產(chǎn)生寬帶信號的能力。為了產(chǎn)生寬帶信號,要求DDS的系統(tǒng)時鐘頻率要高。盡管目前FPGA的速度和規(guī)模都已經(jīng)達到了相當(dāng)高的水平,但與電子干擾系統(tǒng)對它的要求相比仍有差距。按照目前FPGA的技術(shù)水平及使用經(jīng)驗,系統(tǒng)時鐘選擇200MHz是一個比較合理的選擇。因此,為了滿足電子干擾系統(tǒng)更高(如400MHz系統(tǒng)時鐘)的要求,應(yīng)該采用并行處理技術(shù)。

1 并行DDS電路工作原理

并行處理(Parallel Processing)是計算機系統(tǒng)中能同時執(zhí)行兩個或更多個處理機的一種計算方法。處理機可同時工作于同一程序的不同方面。并行處理的主要目的是節(jié)省大型和復(fù)雜問題的解決時間。為使用并行處理,首先需要對程序進行并行化處理,也就是說將工作各部分分配到不同處理機中。而主要問題是并行是一個相互依靠性問題,而不能自動實現(xiàn)。此外,并行也不能保證加速。但是一個在 n 個處理機上執(zhí)行的程序速度可能會是在單一處理機上執(zhí)行的速度的 n 倍。

圖1所示為并行DDS電路工作原理框圖,主要包括:相位累加器、兩路相位/幅度變換電路、二選一選擇器、鎖存器、SINC函數(shù)補償濾波器、D/A變換器和中頻濾波器。相位累加器通過對輸入頻率碼的累加,產(chǎn)生A、B兩路相位累加輸出,其中A路信號在前,B路信號在后(兩路信號合成一路信號后)。兩路相位/幅度變換電路分別對兩路相位累加器輸出的相位進行相位/幅度變換,獲得兩路幅度輸出。然后由二選一選擇器將兩路信號合并成一路信號(S=0時選A,S=1時選B)。相位累加器、相位/幅度變換電路的時鐘以及選擇器選擇端S的信號為fck1,它是由DDS電路系統(tǒng)時鐘fck分頻得到,即fck1=fck/2.而選擇器后面的鎖存器以及SINC函數(shù)補償濾波器、D/A變換器的時鐘為系統(tǒng)時鐘。為了簡化電路實現(xiàn),采用直接中頻方法取出D/A變換器的中頻信號輸出,同時,為了補償D/A變換輸出信號幅度隨頻率增加引起的衰減,圖1中增加了SINC函數(shù)補償濾波器。圖2給出了fck1、fck與數(shù)據(jù)之間時序關(guān)系的示意圖。

2 并行DDS電路實現(xiàn)

主要介紹相位累加器電路和相位/幅度變換器電路的實現(xiàn)。

2.1 相位累加器電路實現(xiàn)

實現(xiàn)并行相位累加器的直接方法是:由兩套結(jié)構(gòu)完全相同的相位累加器電路構(gòu)成,相位累加器的輸入(頻率碼)也相同,只是兩路輸出要有一個固定的初始相位偏差,其數(shù)值為相位累加器輸入(頻率碼)的1/2.

為了電路實現(xiàn)容易,需對上述方法進行簡化。這里提供一種較為簡單的方法,即利用一個相位累加器產(chǎn)生第一路(A路)相位累加器輸出,而另一路相位累加器輸出通過將第一路輸出的相位與相位累加器輸入(頻率碼)的1/2相加得到,如圖3所示。在圖3中,假定系統(tǒng)時鐘為400MHz,假定輸入的頻率碼為26位,范圍為F[25:0],其中位25代表200MHz,位24代表100MHz,…,位0為最低有效位,也就是DDS的分辨率fck/226=5.96Hz.

相位累加器電路中各器件的時鐘頻率為fck1=200MHz.相位累加器的輸入取26位頻率碼F[25:0]的低25位F[24:0],即得到A路相位累加器的輸出為A[24:0].F[25:0]的高25位F[25:1]經(jīng)右移一位(相當(dāng)于乘1/2)得到C[24:0]后與A路相位累加器的輸出A[24:0]相加得到B路相位累加器的輸出B[24:0].

最后,為了減小后面相位/幅度變換電路的硬件量,鎖存器只取出用于進行相位/幅度變換所需位數(shù)的相位(相位截斷),這里取相位截斷輸出為10位,A路為G[9:0],B路為H[9:0].

2.2 相位/幅度變換器電路實現(xiàn)

相位/幅度變換電路的功能是把由相位累加器輸出的相位信息轉(zhuǎn)換成幅度信息。相位/幅度變換電路通常采用ROM電路實現(xiàn),但也可采用數(shù)字邏輯電路實現(xiàn)。

并行相位/幅度變換器由兩套結(jié)構(gòu)完全相同的相位/幅度變換器構(gòu)成,因此,下面只介紹其中的一個。相位/幅度變換的原理可以很容易由ROM構(gòu)成的查找表(LUT)理解。相位/幅度變換的內(nèi)容存儲在ROM中,以相位值作為ROM的地址,ROM的輸出作為變換后的幅度。

與相位累加器不同,相位/幅度變換器的硬件量隨相位位數(shù)(ROM地址)的增加指數(shù)增加,而相位累加器硬件量隨累加器位數(shù)的增加線性增加。因此,當(dāng)相位位數(shù)(影響DDS的寄生信號性能)較大時,所需硬件量將急劇增加。盡管前面已經(jīng)對相位進行了截斷,但為了保證所需的寄生信號性能,剩下的用于進行相位/幅度變換的相位位數(shù)仍然較大,如果直接實現(xiàn)所需硬件量仍然較大。

下面兩種方法對減小硬件量比較有效。一是根據(jù)SIN函數(shù)的對稱性,只需要對一個象限進行相位/幅度變換,另外三個象限可以經(jīng)變換獲得,這樣可節(jié)省近3/4的硬件量[3];第二種是采用分段線性化的方法,也可有效降低ROM地址的位數(shù)[4].

以一個10位相位/8位幅度的相位/幅度變換電路為例,介紹相位/幅度變換電路的具體實現(xiàn)方法并分析硬件量節(jié)省的情況。圖4是分段線性化相位/幅度變換方法示意圖。曲線1是用于進行相位/幅度變換的原始正弦信號前1/4周期(第一象限)的曲線,將它分解成下面的3條曲線(曲線2、3、4)。曲線2是粗相位/幅度變換對應(yīng)的曲線。曲線3和4分別對應(yīng)的是線性變化部分(只有0、1、2三個值,即2位)和校正部分(只有0、1兩個值,即1位)。注意,為了清楚,曲線3和4的幅度都放大了5倍,并分別下移10和20.

根據(jù)圖4的方法,圖5給出了相位/幅度變換電路原理框圖。相位輸入10位,幅度輸出8位,分析中假定忽略掉兩組異或門和一個加法器所占用的硬件資源。在不采用任何措施以節(jié)省硬件資源的情況下,地址為10位,輸出幅度為7位(幅度的最高有效位不需要ROM資源),所需硬件量(ROM容量)為:210×7=7168.當(dāng)利用SIN函數(shù)的對稱性只對第1象限進行相位/幅度變換時,地址由10位變成了8位,所需硬件量變?yōu)椋?8×7=1792,減小了75%.在第1象限的相位/幅度變換中進一步采用分段線性化的方法,將一個較大的ROM(地址8位,字長7位)分解成三個較小的ROM:一個粗相位/幅度變換(地址6位,字長7位),一個分段線性變化部分(它只與最高兩位和最低兩位地址有關(guān),地址4位,字長2位),還有一個校正部分(地址8位,字長1位)。因此,所需硬件總?cè)萘孔優(yōu)椋?6×7+24×2+28×1=736,又減小了近59%.可見,綜合采用上述兩種方法,可以使相位/幅度變換所需的硬件量大幅度減小。

根據(jù)具體情況和具體要求的不同,分解方法并不局限于上面介紹的方法。以圖5為例,由于線性變化部分和校正部分都較小,因此也可以將二者合并成一個地址8位、字長2位的校正部分,這時,所需硬件總?cè)萘繛椋?6×7+28×2=960,減小的硬件量為46%。

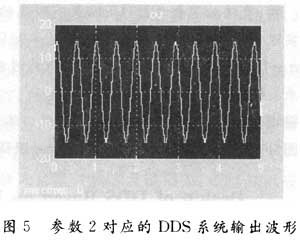

3 實驗測試結(jié)果

為了滿足電子干擾系統(tǒng)對寬帶信號產(chǎn)生的需要,按照上述方法設(shè)計并實現(xiàn)了一個基于FPGA的并行DDS樣機,系統(tǒng)時鐘400MHz(兩路200 MHz構(gòu)成),輸出頻率范圍250MHz~350MHz,頻率分辨率6Hz,相位截斷10位,D/A變換器幅度分辨率8位。

為了簡化外部電路,采用了直接中頻輸出的方法,即直接取出頻率范圍250MHz~350MHz的信號。由圖6可以看出,由于D/A變換器輸出信號幅度隨頻率按SINC函數(shù)衰減,在輸出信號250MHz~350MHz頻率范圍內(nèi),幅度變化范圍較大,約為(-6.5)~(-17.1)=10.6dB.因此,電路中還包含了SINC函數(shù)補償濾波器。

根據(jù)文獻[5],10位相位/8位幅度DDS的最高寄生信號抑制為-60.2dB.不過,這只是在特定條件下的理想結(jié)果,實際的DDS寄生信號性能還受到采樣信號頻譜折疊、D/A變換器采樣脈沖不理想(不是理想的沖擊脈沖)等因素的影響。特別是當(dāng)輸出信號頻率較高時,D/A變換器非線性的影響更不能忽視。因此,實際測量結(jié)果與理論分析會有所不同。圖7給出的是基于FPGA的并行DDS樣機的輸出信號頻譜分布測量結(jié)果,輸出信號約為300MHz,測量范圍是在信號附近(span=1MHz),此時的最大寄生信號抑制優(yōu)于50dB。

本文介紹了一種通過采用并行處理技術(shù)提高DDS系統(tǒng)時鐘的方法,給出了一個基于FPGA的400MHz系統(tǒng)時鐘DDS電路的實現(xiàn)方法和測試結(jié)果,輸出信號頻率范圍250MHz~350MHz,頻率分辨率6Hz,寄生信號抑制優(yōu)于50dB,為實現(xiàn)雷達和電子戰(zhàn)等領(lǐng)域中的寬帶信號產(chǎn)生提供了一種可供選擇的方案,具有實用性。

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

9027瀏覽量

151572 -

頻率合成器

+關(guān)注

關(guān)注

5文章

296瀏覽量

32809 -

雷達

+關(guān)注

關(guān)注

50文章

3114瀏覽量

119954 -

DDS

+關(guān)注

關(guān)注

22文章

672瀏覽量

154335

發(fā)布評論請先 登錄

FPGA實現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化...

FPGA實現(xiàn)高速FFT處理器的設(shè)計

基于FPGA控制的多DSP并行處理系統(tǒng)

基于DDS原理和FPGA技術(shù)的基本信號發(fā)生器設(shè)計

如何利用FPGA和DDS技術(shù)實現(xiàn)正弦信號發(fā)生器的設(shè)計

如何利用現(xiàn)場可編程邏輯門陣列FPGA實現(xiàn)實現(xiàn)DDS技術(shù)?

基于FPGA和高速DAC的DDS設(shè)計與頻率調(diào)制

基于FPGA的DDS調(diào)頻信號的研究與實現(xiàn)

基于FPGA的DDS信號源設(shè)計與實現(xiàn)

基于DSP Builder的DDS設(shè)計及其FPGA實現(xiàn)

低成本的采用FPGA實現(xiàn)SDH設(shè)備時鐘芯片技術(shù)

基于FPGA的振動信號采集處理系統(tǒng)設(shè)計并實際驗證

基于STM32+FPGA的DDS實現(xiàn)

通過FPGA與并行處理技術(shù)實現(xiàn)DDS系統(tǒng)時鐘電路

通過FPGA與并行處理技術(shù)實現(xiàn)DDS系統(tǒng)時鐘電路

評論