PCB設計軟件allegro藍牙音箱案例實操講解,以藍牙音箱為案例將PCB設計基礎知識融進實際案例中,通過操作過程講解PCB設計軟件功能及實用經驗技巧,本次課程將通過對高速信號布線相關知識的學習,完成PCB布線設計。

本期學習重點:

高速信號設計

高速信號處理

高速信號優化

本期學習難點:

高速信號布線

高速信號優化

一、高速信號布線

高速信號目前已經成為PCB設計的主流,以通信產品為代表的電子類產品呈現高速化、高密化的技術發展趨勢,給電路板設計師帶來新的技術挑戰。電路板設計師除了在實戰項目設計中逐步積累高速信號工程經驗外,也需要不斷刷新自身的知識結構、尤其需要補充在高速信號完整性方面的知識。

常見的高速信號以物理接口分類,包括:USB、RJ45、S-Video、VGA、DVI、HDMI、PCIExpress、PCI、SAS/SATA等等;按照邏輯電平分類,包括:LVDS、CML、PECL 等等。

二、高速信號設計

當前的電子產品設計,需要更加關注高速信號的設計與實現,PCB設計是高速信號最終得以保證信號質量并實現系統功能的關鍵設計環節。

傳統的電路板設計方式不關注PCB設計規則的前期仿真分析與制定,從原理圖到PCB的設計實現沒有高速信號規則約束,這樣的傳統設計方式在當前的高速信號產品研發體系中已經不可行,造成的后果一般是多次無效投板加工、不斷測試優化與返工設計,造成研發周期變長、研發成本居高不下。

高速信號電路板設計流程:

(1)高速信號前仿真分析

根據硬件電路模塊劃分與結構初步布局,仿真評估關鍵高速信號質量是否過關,如果不過關則需要修改硬件模塊架構甚至系統架構;仿真信號質量通過的情況下,給出電路板大體模塊布局方案及高速信號拓撲結構與設計規則。

(2)電路板布局及布線設計

根據電路板實際布線的情況,如果與前仿真制定的設計規則有出入,則需要再次仿真分析高速信號質量是否滿足要求,例如:電路板線路布線密度過高、實際設計的線寬比前仿真設計規則要小、可能造成高速信號線路損耗過大、接收端信號幅度不滿足芯片輸入要求而導致電路板功能無法實現。

三、電路板設計師需要掌握的高速信號知識

信號完整性基礎知識和電源完整性基礎知識可以查閱學習SI、PI理論書籍。PCB原材料料基礎知識需要在設計實踐中不斷的積累,下面中間介紹信號拓撲結構知識:

(1)常見信號拓撲結構

①點對點拓撲 point-to-point scheduling

該拓撲結構簡單,整個網絡的阻抗特性容易控制,時序關系也容易控制,常見于高速雙向傳輸信號線;常在源端加串行匹配電阻來防止源端的二次反射。

②菊花鏈結構 daisy-chain scheduling

如下圖所示,菊花鏈結構也比較簡單,阻抗也比較容易控制。菊花鏈的特征就是每個接收端最多只和2個另外的接收端/發送端項鏈,連接每個接收端的stub線需要較短。該結構的阻抗匹配常在終端做,用戴維南端接比較合適。

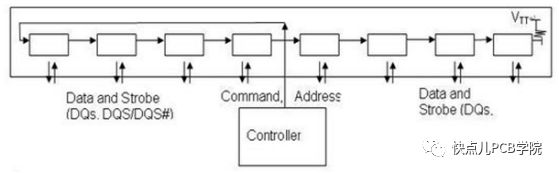

③fly-by scheduling

該結構是特殊的菊花鏈結構, stub線為0的菊花鏈。不同于DDR2的T型分 支拓撲結構,DDR3采用了fly-by拓撲結構,以更高的速度提供更好的信號完整性。

fly-by信號是命令、地址,控制和時鐘信號。如下圖所示,源于存儲器控制器的這些信號以串行的方式連接到每個DRAM器件。通過減少分支的數量和分支的長度改進了信號完整性。然而,這引起了另一個問題,因為每一個存儲器元件的延遲是不同的,取決于它處于時序的位置。通過按照DDR3規范的定義,采用讀調整和寫調整技術來補償這種延遲的差異。

fly-by拓撲結構在電源開啟時校正存儲器系統。這就要求在DDR3控制器中有額外的信息,允許校準工作在啟動時自動完成。

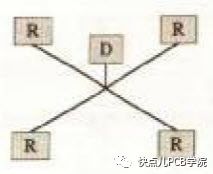

④星形結構 star scheduling

結構如下圖所示,該結構布線比較復雜,阻抗不容易控制,但是由于星形堆成,所以時序比較容易控制。星形結構需要特別注意D點到適合于單項數據傳輸,從D-R,而不適合于從R-D。匹配方式一般在R端做匹配,消除終端反射。

⑤遠端簇結構 far-end cluster scheduling

遠端簇結構可以算是星形結構的變種,要求是D到中心點的長度要遠遠長于各個R到中心連接點的長度。各個R到中心連接點的距離要盡量等長,匹配電阻放置在D附近,常用語DDR的地址、數據線的拓撲結構。

四、高速信號處理方法

通用的高速信號PCB設計處理原則有:

(1)層面的選擇:處理高速信號優先選擇兩邊是GND的層面處理

(2)處理時要優先考慮高速信號的總長

(3)高速信號Via數量的限制:高速信號允許換一次層,換層時加GND VIA如圖

(4)如果高速信號在連接器有一端信號沒有與GND 相鄰PIN時,設計時應加GND VIA 如下圖:

(5)高速信號在連接器內的走線要求:在連接器內走線要中心出線。

(6)高速信號應設置不耦合長度及本對信號的長度誤差,在做長度誤差時須考慮是否要加PIN DELAY

(7)高速信號處理時盡量收發走在不同層,如果空間有限,需收發同層時,應加大收發信號的距離

(8)高速信號離12V 要有180 MIL的間距要求,距離時鐘信號65mil間距

五、高速信號優化方法

以LVDS信號為例,說明高速信號的通常優化方法:

LVDS(Low Voltage Differential Signaling,低電壓差分信號)是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲和低功耗。

LVDS信號不僅是差分信號,而且是高速數字信號。因此,對用來傳輸LVDS的PCB線對必須采取措施,以防止信號在媒質終端發生反射,同時應減少電磁干擾以保證信號的完整性。在PCB布線時需要注意的一些問題如下:

以上便是PCB設計軟件allegro中的高速信號布線講解.

-

pcb

+關注

關注

4355文章

23436瀏覽量

407119 -

PCB設計

+關注

關注

396文章

4788瀏覽量

89384 -

allegro

+關注

關注

42文章

708瀏覽量

147047 -

藍牙音箱

+關注

關注

6文章

267瀏覽量

23224 -

可制造性設計

+關注

關注

10文章

2065瀏覽量

16001 -

華秋DFM

+關注

關注

20文章

3503瀏覽量

5284

原文標題:PCB設計軟件藍牙音箱實操│關鍵信號布線

文章出處:【微信號:eqpcb_cp,微信公眾號:快點兒PCB學院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB設計軟件allegro藍牙音箱案例實操講解

PCB設計軟件allegro藍牙音箱案例實操講解

評論