常見的模塊介紹:選擇器;譯碼器;解碼器;比較器。這里我們主要從常見的Verilog描述的層面去介紹,而不著重考慮電路。將會提到的Verilog語句有 條件選擇語句,case語句,if-else。

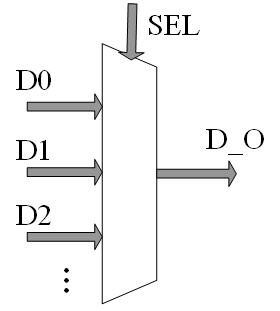

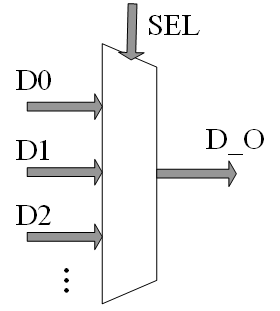

選擇器:電路示意圖如下。根據SEL信號,選擇將D0還是D1,或者D3傳遞給D_O。即根據SEL信號選擇,將某一個輸入信號傳遞給D_O。

對于只有兩個輸入信號的選擇器,我們可以用單層條件選擇語句描述。例如輸入只有D0,D1兩個。那么SEL只要為單bit即可實現選擇。SEL為0時,選擇將D0傳遞給D_O;SEL為1時,選擇將D1傳遞給D_O;

assign D_O = (SEL) ? D1:D0;

注意:條件選擇語句功能: 當 ( ) 里面的expression0的條件為真時,則選擇第一個表達式expression1里面的結果,否則選擇 :后面expression2的結果。結構如下:

assign out = (expression0) ? expression1 : expression2

有多個輸入信號時。例如:有3個輸入,D0,D1,D2; 因為2的2次方等于4,故SEL最小的位寬應該為2。若要實現如下選擇功能。

對應可以使用 case 語句描述:

reg[7:0] D_O;

always @(*) begin

case(SEL[1:0])

2b00: D_O = D0;

2b01: D_O = D1;

2b10: D_O = D2;

default: D_O = h0;

endcase

end

注意:case語句,如果SEL的所有組合沒有列全,最好在最后要加上 default: ... 項,使得信號完整。如此綜合出來的電路才不會出現鎖存器。

對應的可以用case語句去描述它的功能:

reg[7:0] D_O;

always @(*) begin

case(D_IN[2:0])

3b000: D_O = 8b1111_1110;

3b001: D_O = 8b1111_1101;

3b010: D_O = 8b1111_1011;

3b011: D_O = 8b1111_0111;

3b100: D_O = 8b1110_1111;

3b101: D_O = 8b1101_1111;

3b110: D_O = 8b1011_1111;

3b111: D_O = 8b0111_1111;

endcase

end

同樣對于8-3解碼器,大家可以自行去練手。

比較器,或者說判斷器。比如比較兩個數的大小,當a>b是,輸出信號en為高,否則為低。

if-else描述:

reg en;

always @( * )

if( a>b )

en = 1;

else

en = 0;

當然也可以用條件選擇語句:

wire en;

assign en = (a>b) ?1b1 : 1b0;

本文重在通過邏輯實例幫助大家理解常見的Verilog邏輯描述語言。大家在知道自己要實現的功能的情況下,去選擇合適的描述方式。

-

Verilog

+關注

關注

29文章

1366瀏覽量

111912 -

Case

+關注

關注

0文章

28瀏覽量

13561 -

IF

+關注

關注

1文章

64瀏覽量

27130

原文標題:常見的Verilog行為級描述語法

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

硬件描述語言(HDL)編碼技術:xilinx verilog語法技巧

Verilog硬件描述語言描述.

Verilog HDL硬件描述語言_行為建模

基于Verilog硬件描述語言的IEEE標準硬件描述語言資料合集免費下載

Verilog硬件描述語言參考手冊免費下載

常見的Verilog行為級描述語法

常見的Verilog行為級描述語法

評論