隨著集成電路設計的不斷發展,集成電路的規模越來越大,設計難度日趨復雜,傳統的設計方法已越不能適應集成電路設計發展的需要。基于IP復用的數字IC設計方法是有效提高IC設計產能的關鍵技術,有助于快速實現工藝先進、功能強大的產品。

微控制器MCU是嵌入式系統的核心,8位MCU IP核具有很高的通用性和靈活性,廣泛地應用于工業控制、機械設備、家用電器以及汽車電子等各個領域。本文介紹的是基于 RISC體系結構的8位高速MCUIP軟核的設計與實現,采用Verilog HDL自上而下地描述了MCUIP軟核的硬件結構,并驗證了設計的可行性和正確性。在實際硬件電路中,該IP核的運行頻率達到75MHz,可應用于高速控制領域。

系統結構設計

本設計的總線采用了哈佛結構,14位指令字長,8位數據字長,指令集與PIC16F676兼容。它具有35條指令,在連續工作的情況下,除了程序跳轉指令要用2個指令周期外,其它的所有指令都可以在1個指令周期內完成。由于哈佛結構總線具有獨立的指令總線和數據總線,可同時從程序存儲器和數據存儲器中分別讀取數據,大大提高了MCU內部執行的并行性,簡化了控制電路的設計。與更深級流水線相比,簡單的指令周期避免了深度流水線增加電路結構復雜性和芯片面積。

該微處理器在結構上可以劃分為四個子系統,分別為控制單元、數據通道、存儲單元、I/O單元。其中數據通道包含ALU和一個W工作寄存器。片內程序存儲器ROM的容量是8k×14位;數據存儲器由包括專用寄存器在內的256個可尋址的8位寄存器組成,通過數據總線與算術邏輯單元ALU相連,系統可以對數據存儲器用直接或間接尋址方式進行訪問。I/O單元提供了系統內部的數據總線與外界總線的連接接口,實現數據的輸入/輸出。控制單元則會根據指令產生相應的指示信號控制系統的協調運行。系統結構如圖1所示。

MCU IP核的時序設計

時鐘網絡的時序設計

本設計的時序設計部分采用內部包含4個節拍時鐘的結構,時鐘網絡模塊在復位結束后會利用兩級嵌套的D觸發器將外部時鐘(CLK)分頻產生4個非重疊正交的節拍時鐘信號q1、q2、q3、q4,一個指令周期分為4個狀態。節拍時鐘會與譯碼電路產生的控制信號配合,在不同時鐘節拍選通不同的電路操作,進而協調整個系統的運行。

二級流水線時序設計

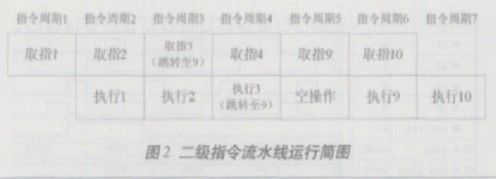

本設計所采用的二級流水線劃分為取指和執行兩級。系統運行時,會在前一指令周期的q4節拍從ROM中取出下一條待執行的指令并鎖存在指令寄存器中,在下一指令周期的q1節拍從指令寄存器中取出指令,同時程序計數器(PC)加1,q2到q4對所取指令進行譯碼和執行。因此,一條指令的完整執行過程大概分為取指令、指令鎖存、指令譯碼、取操作數、執行、回寫、PC+1等7個步驟。從時序上看,指令取指周期與執行周期是并行執行的,即在取指的同時,上一條指令正在進入執行周期。

程序跳轉指令與其它單周期指令一樣進入流水線,在執行程序跳轉指令時,屏蔽下一條指令進入指令譯碼單元,用空操作指令NOP代替。這樣,控制邏輯不需要做太大修改就能滿足流水線的執行。二級指令流水線操作過程如圖2所示。

MCU IP核的內部電路實現

指令寄存器

指令寄存器(IR)是為了實現兩級指令流水線而設計的。如果沒有指令寄存器,那么取指和執行就分別需要占用一個指令周期。但如果利用IR,在上條指令執行的同時把下一條指令從程序存儲器ROM中取出來寄存在IR中,這樣在每個指令周期內同時有指令的取出和執行,等效來看,一條指令只需要一個指令周期就可以執行完畢,從而提高了效率。

指令寄存器IR的另外一個功能是當執行分支指令的時候產生空操作,這是采用指令流水線結構所必需的。例如在執行程序跳轉指令GOTO的時候,由于GOTO指令會改變程序計數器PC的值,跳轉到另外的地址,那么在執行GOTO指令時取得的緊接GOTO的下一條指令就不是要執行的下一條指令,這個已經取得的指令就必須被屏蔽。具體的操作是在執行GOTO指令的時候,指令譯碼單元產生清零信號使得指令寄存器內部14位寄存單元被清零,那么下一指令周期的輸出就變為NOP指令。在執行該空操作的同時把GOTO指令跳轉后指向地址對應的指令取出來,在下個指令周期執行。

指令譯碼單元

指令譯碼單元在每個時鐘周期的q1節拍接收來自IR的14位執行指令,并對指令進行譯碼工作,給出其它各單元的操作控制信號,包括算術邏輯單元(ALU)的運算控制信號、RAM的讀寫控制、總線控制器的選擇信號、PC尋址等。

算術邏輯單元

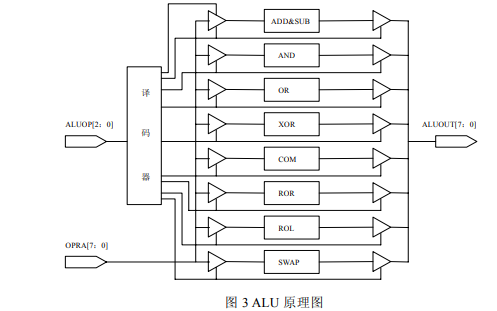

算術邏輯單元(ALU)是微控制器運算電路的核心部分,主要功能是按照指令譯碼器輸出的控制信號,實現算術運算、邏輯運算、循環移位等操作。ALU的字寬是8位,在ALU中做運算的2個操作數分別來自W寄存器和數據總線,最后運算的結果由指令譯碼后的控制信號決定是存放在W寄存器中,還是通用寄存器RAM中。本文通過將加、減操作復用到一個8位超前進位加法器,大大縮短了ALU算術運算的時間,進而提高了整個系統的運行速度。

程序計數器和堆棧

13位的PC對8k×14bit的ROM進行尋址,八級堆棧存儲的是ROM的地址,即在主程序中調用的子程序最多允許嵌套8次。當系統復位后PC從0000h地址開始執行,然后在每個指令周期q1節拍,PC自動加1。當執行GOTO指令時,就從指令中獲取地址來改變PC的值,然后PC再在此基礎上自動加1,順序執行指令。當執行調用子程序指令CALL指令時,把取指的地址送到堆棧保護起來,然后PC裝載子程序入口的地址,接著順序執行子程序指令直到子程序執行完,程序返回時把堆棧中的地址裝載到PC,PC繼續自動加1順序執行指令。

在每個時鐘周期,PC會檢測是否有來自中斷處理單元的中斷請求信號發生,一旦有中斷響應,PC就會進入中斷處理模式,把中斷現場的地址送入堆棧保護起來,并在下一指令周期PC指向中斷向量地址0004h,這是中斷服務程序的入口地址,系統執行中斷服務程序直到中斷返回,再把保護在堆棧的中斷現場地址加載到PC中,然后又順序執行指令。

定時器/計數器

TIMER0為8位可讀寫的定時器/計數器單元,其內部有一個分頻器,可以通過寄存器配置選擇定時或計數工作方式,以及分頻器的分頻比,分頻比最高可達l:128。當TIMER0從FFh到00h計數溢出時,將產生TIMER0中斷。

中斷處理單元

中斷處理單元會響應各個中斷源的中斷,并向系統的控制電路發出總中斷請求信號。該單元設置有8位中斷控制寄存器和外設中斷寄存器,使用標志位來記錄各種中斷請求。中斷控制寄存器還包括各中斷的使能控制位以及全局中斷使能位。全局中斷使能位將使能(置1時)所有未被屏蔽的中斷,或禁止(清零時)所有中斷。一旦進入中斷服務程序,可通過查詢中斷標志位確定中斷源。

雙向I/O

PORTA和PORTC為2個6位雙向I/O端口,每個端口有2個物理寄存器,分別是方向寄存器和數據寄存器。方向寄存器控制對應端口的輸入/輸出屬性,數據寄存器負責鎖存輸入/輸出數據。

MCU IP核的硬件仿真

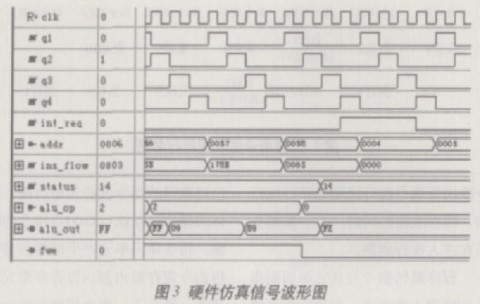

IP軟核的仿真測試是設計過程中非常重要的環節,通過自主建立的測試向量庫,編寫了覆蓋所有指令的測試文件,對軟核的多種指令、地址和數據組合進行了仿真測試,提高了軟核功能仿真的測試覆蓋率,保證了設計的正確性。由PORTA和PORTC的輸出來驗證設計正確性。部分信號波形如圖3所示,在正常情況下,地址是在每個指令周期進行加1取指的;當中斷信號int_req=1時,地址在下一指令周期跳到中斷向量地址0004h,同時屏蔽下一條指令進入指令譯碼單元,用NOP指令代替。

結語

本文介紹了一個8位RISC結構的高速微控制器IP軟核的設計,其指令集與PIC16F676兼容,采用模塊化結構,面向硬件映射,保證可綜合性。該核使用VerilogHDL為RTL級描述語言,通過了ActiveHDL仿真驗證后,用Quartus II 5.0進行綜合,并在Altera的EP1C12Q24C08器件上實現了布局布線。經測試,時鐘頻率達到了75MHz,驗證了設計的正確性,為今后的設計積累了大量有益的經驗。

-

mcu

+關注

關注

146文章

17869瀏覽量

361082 -

寄存器

+關注

關注

31文章

5424瀏覽量

123508 -

IP

+關注

關注

5文章

1789瀏覽量

151443

發布評論請先 登錄

【「RISC-V體系結構編程與實踐」閱讀體驗】-- 前言與開篇

【「RISC-V體系結構編程與實踐」閱讀體驗】-- SBI及NEMU環境

Microarchitecture指令集體系結構

已結束-【書籍評測活動NO.3】一本書帶你了解谷歌、蘋果等科技巨頭都看好的RISC-V體系結構

初探RISC-V—《RISC-V體系結構編程與實踐》

《RISC-V體系結構編程與實踐》試讀

《RISC-V體系結構編程與實踐》+試讀經驗

LTE體系結構

網絡體系結構,什么是網絡體系結構

PowerPC的發展與體系結構概述

基于RISC體系結構的8位高速MCU的IP軟核設計

基于RISC體系結構的8位高速MCU的IP軟核設計

評論