實現(xiàn)數據的高速大容量存儲是數據采集系統(tǒng)中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態(tài)機來描述對DDR SDRAM 的各種時序操作,設計了DDR SDRAM 的數據與命令接口。用控制核來簡化對DDR SDRAM 的操作,并采用自頂至下模塊化的設計方法,將控制核嵌入到整個數據采集系統(tǒng)的控制模塊中,完成了數據的高速采集、存儲及上傳。使用開發(fā)軟件Quartus II 中內嵌的邏輯分析儀SignalTap II 對控制器的工作流程進行了驗證和調試。最終采集到的數據波形表明,完成了對DDR SDRAM 的突發(fā)讀寫操作,達到了預期設計的目標。

DDR SDRAM 是Double Data Rate SDRAM 的縮寫,即雙倍速率同步動態(tài)隨機存儲器。

DDR 內存是在SDRAM 內存基礎上發(fā)展而來的,能夠在時鐘的上升沿和下降沿各傳輸一次數據,可以在與SDRAM 相同的總線時鐘頻率下達到更高的數據傳輸率。本設計中采用Altera 公司Cyclone 系列型號為EP1C6Q240C8 的FPGA 實現(xiàn)控制器,以Hynix 公司生產的型號為HY5DU121622B(L)TP 的DDR SDRAM 為存儲器,完成了對數據的高速大容量存儲。

1 DDR SDRAM 的控制原理及存儲功能的實現(xiàn)

DDR SDRAM 支持的常用命令有7 種:空操作(NOP)、激活操作(Active)、突發(fā)讀(BurstRead)、突發(fā)寫(Burst Write)、自動刷新(Autorefresh)、預充電(Precharge)、模式寄存器配置(Mode Register Set)。所有的操作命令都是通過信號線RAS_N、CAS_N、WE_N 共同控制來實現(xiàn)的。在對DDR SDRAM 進行存取數據操作之前,首先要對其初始化,即設置DDR SDRAM的普通模式寄存器和擴展模式寄存器,確定DDR SDRAM 的工作方式,這些設置包括突發(fā)長度、突發(fā)類型、CAS 潛伏期和工作模式以及擴展模式寄存器中的對DDR SDRAM 內部延遲鎖定回路(DLL)的使能與輸出驅動能力的設置。

初始化完成之后,DDR SDRAM 便進入正常的工作狀態(tài),此時便可對存儲器進行讀寫和刷新。DDR SDRAM 在一對差分時鐘的控制下工作。命令(地址和控制信號)在每個時鐘的上升沿被觸發(fā)。隨著數據DQ 一起傳送的還包括一個雙向的數據選通信號DQS,接收方通過該信號來接收數據。DQS 作為選通信號在讀周期中由DDR SDRAM 產生,在寫周期中由存儲器的控制器產生。該選通信號與數據相關,其作用類似于一個獨立的時鐘,并滿足相應的時序要求。由于DDR SDRAM 的數據接口在時鐘的兩個沿的觸發(fā)下工作,其數據寬度是存儲器數據寬度的一半。為實現(xiàn)數據的大容量存儲,設計時采用的是一個控制核同時對兩片DDR SDRAM 進行操作,外接數據線的寬度由單片DDR SDRAM 的16 位擴展到32位。

對DDR SDRAM 的讀和寫操作是基于突發(fā)的,即從一個選定的地址單元開始,連續(xù)存取已設置長度的地址單元,該長度就是所謂的突發(fā)長度。DDR SDRAM 提供的可編程的讀或寫的突發(fā)長度為2,4 或8。數據的存取以一個激活命令(Active)開始,接著便是讀(BurstRead)或寫(Burst Write)命令。與激活命令一起被觸發(fā)的地址位用來選擇將要存取的區(qū)和頁(或行),與讀或寫命令一起被觸發(fā)的地址位用來選擇突發(fā)存取的起始列單元。讀命令被觸發(fā)后,數據將在1.5~3 個時鐘周期之后出現(xiàn)在數據總線上。這個延遲就是所謂的CAS 潛伏期(CAS latency),即從DDR SDRAM 內核讀出數據到數據出現(xiàn)在數據總線上所需要的時間。CAS 潛伏期的大小與SDRAM 的速度和存儲器的時鐘頻率有關。當要存取一個不同行的地址單元時,需要通過一個預充電(Precharge)操作關閉當前行。

自動刷新(Autorefresh)命令用來周期性地刷新DDR SDRAM,以保持其內部的數據不丟失。2 DDR SDRAM 控制器的設計DDR SDRAM 控制器的功能包括:

(1)初始化DDR SDRAM;

(2)簡化DDR SDRAM的讀寫時序;

(3)將DDR SDRAM 接口的雙時鐘沿數據轉換為單時鐘沿數據,使得對DDR SDRAM 的操作類似于普通RAM;

(4)控制器還要產生周期性的刷新命令來維持DDR SDRAM 內的數據而不丟失。其控制轉換圖如圖1 所示。

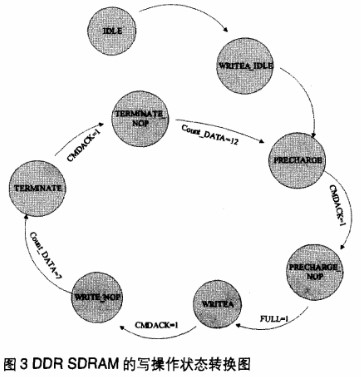

在對DDR SDRAM 初始化完成之后,就可進行讀、寫或其他操作。在執(zhí)行讀(寫)命令之前,先要激活將要讀(寫)的行,之后便可對該行進行突發(fā)讀(寫)。在控制器的設計中,所有的讀寫命令都是不帶預充電的,因此,某一行被激活之后將一直處于激活狀態(tài),直到用戶發(fā)送突發(fā)終止命令,此時控制器將自動產生一個預充電命令來關閉當前行。這樣,某一行被激活之后用戶便可進行連續(xù)的突發(fā)讀(寫)操作,從而節(jié)省了每次突發(fā)讀寫所需要的激活時間,提高了系統(tǒng)的數據吞吐率。

2.1 DDR SDRAM 的讀操作流程

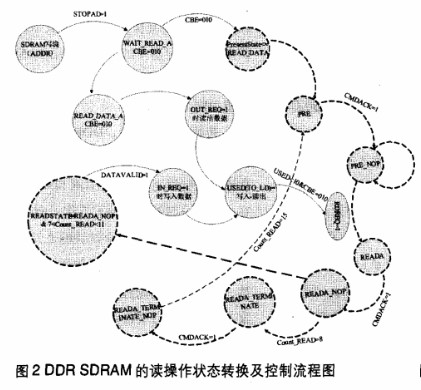

通過對DDR SDRAM 的讀時序的分析,將整個讀操作過程分解為7 個狀態(tài),每一個狀態(tài)都對應著不同的命令(CMD)值,DDR 控制核通過對CMD 的譯碼完成對DDR SDRAM的操作。從整體的控制過程來看,讀操作流程如圖2 所示。其中實線表示的是讀操作的控制流程,虛線表示的讀操作的狀態(tài)轉換流程。控制流程的實現(xiàn)依賴于控制器內部狀態(tài)轉換產生的控制信號。實現(xiàn)各狀態(tài)之間切換的控制信號主要有命令應答信號CMDACK,外部控制信號RDREQ 以及程序內部的計數器Count_READ。當系統(tǒng)的主狀態(tài)機進入到讀數據狀態(tài)時,控制信號CBE=“010”;控制器內部的狀態(tài)機進入到讀狀態(tài)。讀流程中另一個重要的信號為RDREQ,它是由控制器后端的緩存(FIFO)產生的,當緩存中數據容量低于設定值時,信號RDREQ 被置高,讀狀態(tài)由PRE_NOP 進入READA,發(fā)起一次讀操作,完成8 個數據的傳送。程序內部的計數器Count_READ 保證控制核在經過設定的CAS 潛伏期后從數據總線上讀取數據。

3 DDR SDRAM 控制器的FPGA實現(xiàn)

3.1 控制電路主狀態(tài)機設計

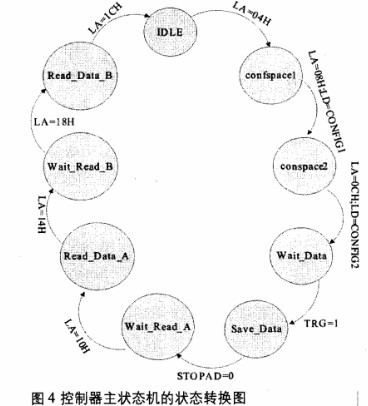

主狀態(tài)機用于控制整個數據采集系統(tǒng)的工作流程。各功能模塊的配合,命令的發(fā)送,數據的采集、存儲和傳輸都需要狀態(tài)機來協(xié)調并嚴格控制時序關系。其狀態(tài)轉換圖如圖4 所示。控制器上電或復位時進入IDLE 狀態(tài),其中LA 和LD 分別為PCI 局部總線的地址線和數據線,上位機的發(fā)送的命令通過PCI 總線及接口芯片傳送到PCI 局部總線,其中地址線的變化將引起狀態(tài)機內部的狀態(tài)轉換,狀態(tài)轉換的同時,相應的配置字將出現(xiàn)在數據線上。配置完參數之后,轉態(tài)機進入等待數據狀態(tài)(WAIT_DATA),當觸發(fā)信號滿足要求之后(TRG=‘1’),自動進入到保存數據狀態(tài)(SAVE_DATA),在此狀態(tài)下,控制程序開始進行數據采集。指定存儲深度的數據采集完成后,主狀態(tài)機自動進入等待讀數據狀態(tài),在接受到地址線上的狀態(tài)轉換命令后,分別進入讀取A 通道和B 通道數據的狀態(tài)。數據讀完之后,上位機發(fā)送命令使狀態(tài)返回到IDLE 狀態(tài)。

3.2 DDR SDRAM 控制器各模塊結構圖

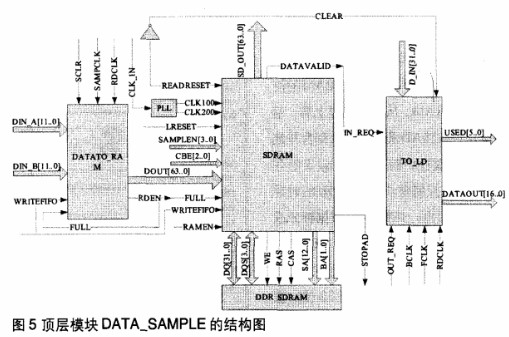

系統(tǒng)的頂層文件DATA_SAMPLE 的結構如圖5 所示,F(xiàn)PGA 內置的主要有前端緩存模塊DATATO_RAM、后端緩存模塊TO_LD 和DDR SDRAM 的控制模塊SDRAM。從數據流程上看,前端緩存將雙路AD 采集到的數據合并成64 位,當緩存中的數據達到設定的存儲深度時,控制模塊在100MHz 的時鐘下將數據讀出,并將64 位數據拆分成32 位分別存儲到兩片DDR SDRAM 中。進入到讀狀態(tài)時,控制模塊同時從兩片DDR SDRAM 中讀出32位的數據,根據用戶所選擇的數據通道,控制邏輯將相應的數據送入后端緩存中,后端緩存再將數據拆分成16 位,通過PCI 局部總線傳送到上位機中。從控制流程上看,DATATO_RAM和TO_LD 中都設置了數據計數器,當DATATO_RAM 中存儲的數據量超過設定值時,讀使能RDEN 有效,控制模塊從緩存中一次讀走4 個數據。后端緩存的控制方式與此類似。

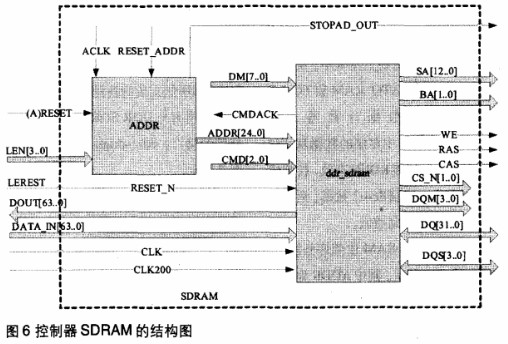

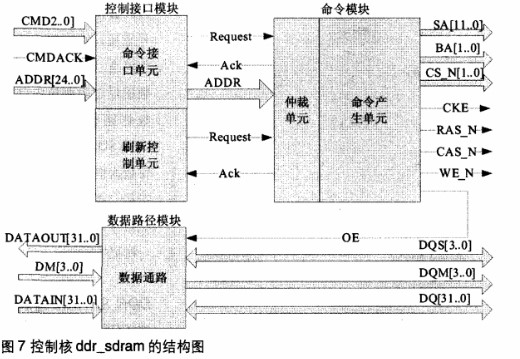

控制模塊SDRAM 由兩部分組成,其結構如圖6 所示。其中ADDR 為地址產生模塊,給控制核ddr_sdram 提供數據操作的行地址和列地址。控制核ddr_sdram 完成的功能包括將內部狀態(tài)轉換產生的CMD 控制命令譯碼成DDR SDRAM 所能實現(xiàn)的各種操作并實現(xiàn)以雙倍的速率與DDR SDRAM 進行數據交換的接口。ddr_sdram 的結構框圖如圖7 所示。

控制核ddr_sdram 采用自頂而下模塊化的設計方法,由4 個模塊構成:ddr_sdram 頂層模塊、控制接口模塊、命令模塊和數據路徑模塊。ddr_sdram 頂層模塊初始化并把其余三個模塊有機地結合起來;控制接口模塊接收CMD 命令和相關存儲器地址,對命令進行譯碼并將請求發(fā)送給命令模塊;命令模塊接收從控制接口模塊譯碼后的命令和地址,產生相應的命令給DDR SDRAM;數據路徑模塊在讀命令READA 和寫命令WRITEA 期間處理數據交換。控制接口模塊包含1 個命令譯碼器和1 個16 位的刷新減計數器及相應的控制電路。 命令譯碼器譯碼并將譯碼后的命令及相應的地址轉送給命令模塊。減計數器和相應的控制電路用來產生刷新命令給命令模塊。其值就是由LOAD_REG2 命令寫入到REG2 中的值。當計數器減到0 時,控制接口模塊就向命令模塊發(fā)Request 并一直保持到命令模塊發(fā)Ack 來響應該請求。一旦控制接口模塊接收到Ack,減計數器就會重新寫入REG2 中的值。命令模塊由1 個簡單的仲裁器、命令發(fā)生器及命令時序器組成。它接收從控制接口模塊來的譯碼后的命令,同時接收刷新控制邏輯發(fā)來的刷新請求命令并產生正確的命令給DDR SDRAM。仲裁器在控制接口發(fā)來的命令和刷新控制邏輯發(fā)來的刷新請求命令之間進行仲裁。刷新請求命令的優(yōu)先級高于控制接口來的命令。

在仲裁器收到命令譯碼器發(fā)來的命令后,該命令就傳送到命令發(fā)生器,命令時序器即用3 個移位寄存器產生正確的命令時序后發(fā)給DDR SDRAM。1 個移位寄存器用來控制激活命令時序,1 個用來控制READA 和WRITEA命令,1 個用來計時操作命令的持續(xù)時間,為仲裁器確定最后的請求操作是否完成。數據路徑模塊提供了DDR SDRAM 到FPGA 的數據通道。在和DDR SDRAM 接口的一方,數據路徑模塊將從DDR SDRAM 過來的數據總線寬度翻倍,并在200MHz 的時鐘頻率接收DDR SDRAM 在100MHz 時鐘的上下沿送出的數據。在和FPGA 接口的一方,數據路徑模塊將從FPGA 送來的數據寬度減半并以2 倍的速率送給DDR SDRAM。4 系統(tǒng)實現(xiàn)的功能及結果分析邏輯分析儀SignalTap II 是Quartus II 軟件中集成的一個內部邏輯分析軟件,使用它可以觀察本設計的內部信號波形。在系統(tǒng)的軟件設計和仿真完成之后,將編譯后的文件下載到系統(tǒng)的硬件中,對DDR SDRAM 控制器的狀態(tài)轉移和讀寫流程中各個信號進行了實時的采集與顯示。

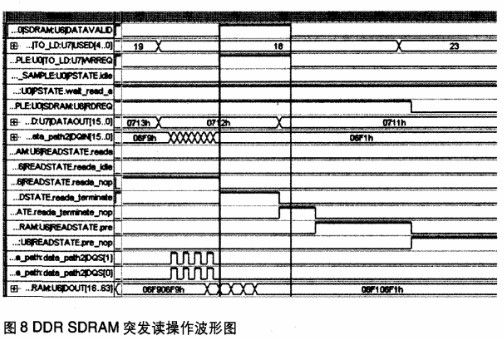

如圖8 所示,是控制器讀數據時嵌入式邏輯分析儀采集到的波形圖。第9 行到第15行的信號顯示的是讀流程中各狀態(tài)之間的切換過程。讀命令發(fā)出之后,經過CAS 潛伏期,DDR SDRAM 突發(fā)傳輸8 個數據,并產生選通信號DQS。控制器在讀到數據線DQ 上的數據后,將數據寬度加倍,傳送到后端緩存中。

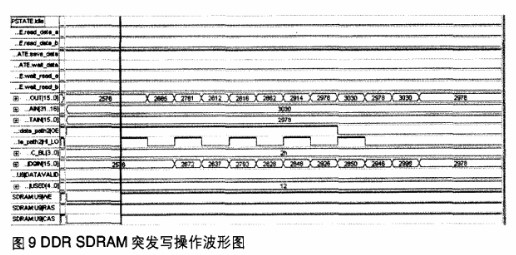

寫數據的波形圖如圖9 所示,當主狀態(tài)機在SAVE_DATA 狀態(tài)時,DDR SDRAM 從控制器的數據總線上一次存儲8 個數據。圖中的選通信號HI_LO 是由控制器產生的,在信號的上升沿和下降沿存儲器存儲數據總線上的數據,存滿8 個完成一次寫操作。直到前端緩存的讀使能信號有效時,控制器從前端緩存讀取數據,并發(fā)起下一次寫操作。

將所設計的控制器用于最高采樣速率為10MHz 的數據采集系統(tǒng)中,DDR SDRAM 工作的差分時鐘為100MHz,容量為32MByte,系統(tǒng)運行性能良好,能夠較好的完成DDR SDRAM與AD 轉換模塊,PCI 總線接口模塊之間的數據交換。圖10 為數據采集卡對10kHz 正弦信號采樣的波形。

5 特色描述

(1) 本設計在深入了解DDR SDRAM 工作原理的基礎上,確定了DDR SDRAM 控制器的總體方案和模塊化設計方法。

(2) 用FPGA實現(xiàn)的DDR SDRAM的控制器能在很高的速度下完成數據的讀寫和復雜的控制操作,工作可靠。

(3) 該控制器解決了DDR SDRAM 用于高速數據采集的關鍵技術問題,對增加數據采集系統(tǒng)的緩存容量具有重要意義。

-

FPGA

+關注

關注

1644文章

21998瀏覽量

615618 -

存儲器

+關注

關注

38文章

7641瀏覽量

166691 -

數據采集

+關注

關注

40文章

7041瀏覽量

115988

發(fā)布評論請先 登錄

FPGA和DDR3 SDRAM DIMM條的接口設計實現(xiàn)

如何用中檔FPGA實現(xiàn)高速DDR3存儲器控制器?

如何實現(xiàn)FPGA和DDR3 SDRAM DIMM條的接口設計?

使用Verilog實現(xiàn)基于FPGA的SDRAM控制器

基于FPGA的DDR2 SDRAM存儲器用戶接口設計

基于FPGA的DDR3 SDRAM控制器用戶接口設計

FPGA讀寫SDRAM的實例和SDRAM的相關文章及一些SDRAM控制器設計論文

使用Virtex-4 FPGA器件實現(xiàn)DDR SDRAM控制器

DDR SDRAM控制器的設計與實現(xiàn)

基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)簡介

基于FPGA的SDRAM控制器的設計與實現(xiàn)簡介

基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)

基于FPGA器件實現(xiàn)對DDR SDRAM的控制

基于FPGA器件實現(xiàn)對DDR SDRAM的控制

評論