設(shè)計(jì)背景:

頻率計(jì)又稱為頻率計(jì)數(shù)器,是一種專門對(duì)被測(cè)信號(hào)頻率進(jìn)行測(cè)量的電子測(cè)量?jī)x器。頻率計(jì)主要由四個(gè)部分構(gòu)成:時(shí)基(T)電路、輸入電路、計(jì)數(shù)顯示電路以及控制電路。

頻率,即使信號(hào)周期的倒數(shù),也就是說,信號(hào)每單位時(shí)間完成周期的個(gè)數(shù),一般去一秒為基本單位時(shí)間。

設(shè)計(jì)原理:

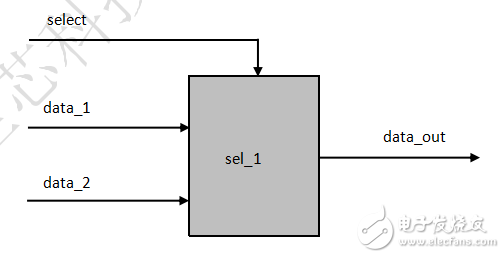

本次的設(shè)計(jì)主要是一個(gè)簡(jiǎn)單的二選一數(shù)據(jù)選擇器,我們的設(shè)計(jì)主頻率=1s/T,T=高電平的時(shí)間+低電平的時(shí)間。時(shí)間=周期數(shù)*周期。占空比=(高電平的時(shí)間/周期)100%。我們的時(shí)間單位都是以ns來計(jì)算的,所以要把1s換成1_000_000_000ns,驅(qū)動(dòng)時(shí)鐘是50MHz的,周期為20ns。計(jì)算占空比的時(shí)候,我們把周期20ns全部省略了。所以計(jì)算公式如下:

freq = 1_000_000_000/(low_time * 20 + high_time * 20);

duty_cycle = (high_time * 100)/(high_time + low_time);

設(shè)計(jì)架構(gòu)圖:

設(shè)計(jì)代碼:

設(shè)計(jì)模塊

0modulefreq_meter (clk,rst_n,wave,freq,duty_cycle);//端口列表

1

2 inputclk;//時(shí)鐘

3 inputrst_n;//復(fù)位

4 inputwave;//被測(cè)頻率

5 output[25:0]freq;//輸出頻率

6 output[6:0]duty_cycle; //輸出占空比

7

8 reg[25:0]low_cnt;

9 reg[25:0]high_cnt;

10 reg[25:0]low_time;

11 reg[25:0]high_time;

12 regstate;

13

14 localparamhigh_state =1'b0;

15 localparamlow_state =1'b1;

16

17 always@(posedgeclk ornegedgerst_n)

18 begin

19 if(!rst_n)

20 begin

21 low_cnt <=26'd0;

22 high_cnt <=26'd0;

23 low_time <=26'd0;

24 high_time <=26'd0;

25 state <=high_state;

26 end

27 else

28 begin

29 case(state)

30 high_state :begin

31 if(wave ==1'b1)//判斷輸入為高電平

32 begin

33 high_cnt <=high_cnt +1'b1;

34 state <=high_state;

35 end

36 else

37 begin

38 high_cnt <=26'd0;

39 high_time <=high_cnt;

40 state <=low_state;

41 end

42 end

43

44 low_state :begin

45 if(wave ==1'b0)//判斷輸入為低電平

46 begin

47 low_cnt <=low_cnt +1'b1;

48 state <=low_state;

49 end

50 else

51 begin

52 low_cnt <=26'd0;

53 low_time <=low_cnt;

54 state <=high_state;

55 end

56 end

57 default:state <=low_state;

58 endcase

59 end

60 end

61

62 assignfreq =1_000_000_000/(low_time *20+high_time *20);//求頻率

63 assignduty_cycle =(high_time *100)/(high_time +low_time);//求占空比

64

65endmodule

測(cè)試模塊

0`timescale1ns/1ps

1modulefreq_meter_tb;

2 regclk;

3 regrst_n;

4 regwave;

5 wire[25:0]freq;

6 wire[6:0]duty_cycle;

7

8 initialbegin

9 clk =1'b1;

10 rst_n =1'b0;

11

12 #200.1

13 rst_n =1'b1;

14 #1_000_000_0//仿真10ms

15 $stop;

16 end

17

18 always#10clk =~clk;

19

20 initialbegin

21 wave =1'b1;

22 foreverbegin//產(chǎn)生占空比為60%,頻率為1KHz的方波

23 #600_000

24 wave =1'b0;

25 #400_000

26 wave =1'b1;

27 end

28 end

29

30 freq_meter freq_meter_dut(

31 .clk(clk),

32 .rst_n(rst_n),

33 .wave(wave),

34 .freq(freq),

35 .duty_cycle(duty_cycle)

36 );

37

38endmodule

仿真圖:

由于在前面沒有測(cè)完一個(gè)周期出現(xiàn)了不穩(wěn)定的因素,就出現(xiàn)了不準(zhǔn)確的數(shù)值,當(dāng)測(cè)試完一個(gè)周期以后,測(cè)到的數(shù)值就比較的準(zhǔn)確,基本的沒有什么誤差。

相對(duì)的,如果測(cè)試的頻率越大,測(cè)到的數(shù)值就越準(zhǔn)確。

-

頻率計(jì)數(shù)器

+關(guān)注

關(guān)注

2文章

73瀏覽量

8977 -

低電平

+關(guān)注

關(guān)注

1文章

153瀏覽量

13522 -

高電平

+關(guān)注

關(guān)注

6文章

171瀏覽量

21773

原文標(biāo)題:FPGA學(xué)習(xí)系列:33. 頻率計(jì)的設(shè)計(jì)

文章出處:【微信號(hào):FPGAer_Club,微信公眾號(hào):FPGAer俱樂部】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何設(shè)計(jì)一個(gè)參數(shù)化的數(shù)據(jù)選擇器

至芯科技之a(chǎn)ltera 系列FPGA教程 第九篇 二選一多路選擇器的設(shè)計(jì)

至芯科技之a(chǎn)ltera 系列FPGA教程 第十篇 二選一多路選擇器激勵(lì)的設(shè)計(jì)

找一種八選一數(shù)據(jù)選擇器貼片式芯片

請(qǐng)問有單個(gè)二選一數(shù)據(jù)選擇器的芯片嗎?

【夢(mèng)翼師兄今日分享】 二選一數(shù)據(jù)選擇器的設(shè)計(jì)

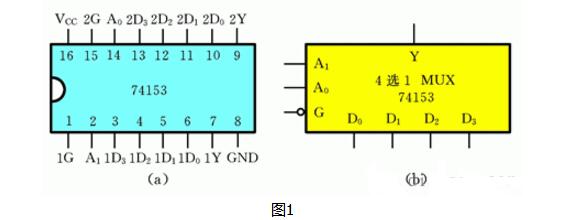

EDA四選一多路選擇器的設(shè)計(jì)

4選1多路選擇器是什么?

eda四選一多路選擇器的設(shè)計(jì)

FPGA學(xué)習(xí)系列:二選一數(shù)據(jù)選擇器的設(shè)計(jì)

74LS153利用雙四選一數(shù)據(jù)選擇器實(shí)現(xiàn)全加器的電路圖資料免費(fèi)下載

FPGA學(xué)習(xí)系列:33. 設(shè)計(jì)一個(gè)簡(jiǎn)單的二選一數(shù)據(jù)選擇器

FPGA學(xué)習(xí)系列:33. 設(shè)計(jì)一個(gè)簡(jiǎn)單的二選一數(shù)據(jù)選擇器

評(píng)論