在分析place_design生成的dcp時,就要開始關注保持時間違例,尤其是當WHS < -0.5ns時。這是因為過大的保持時間違例往往會導致布線時間增大,同時,在布線階段,工具未必能修復此類違例。

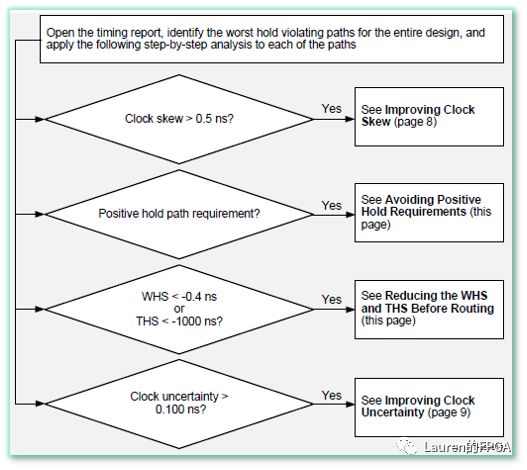

解決保持時間違例流程如下圖所示。按照此流程,要逐步關注以下幾個因素:

Clock Skew是否大于0.5ns

Hold Requirement是否為正(應該為0)

WHS是否小于-0.4ns或THS是否小于-1000ns

Clock Uncertainty是否大于0.1ns

圖片來源 page 4, ug1292

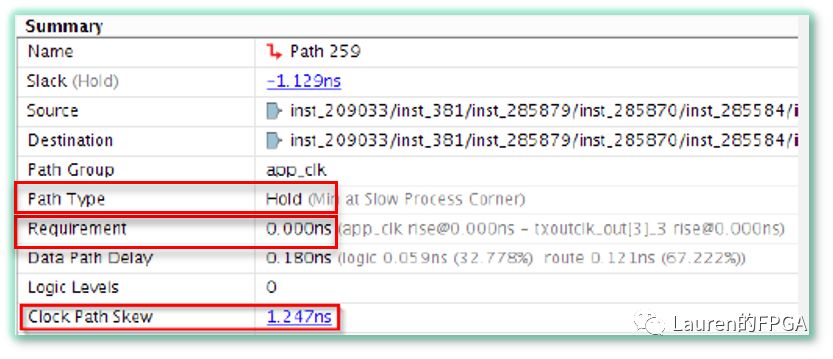

這幾個指標的具體數值可在時序報告中查到,如下圖所示。圖中,Path Type用于確定分析的是保持時間。

圖片來源 page 4, ug1292

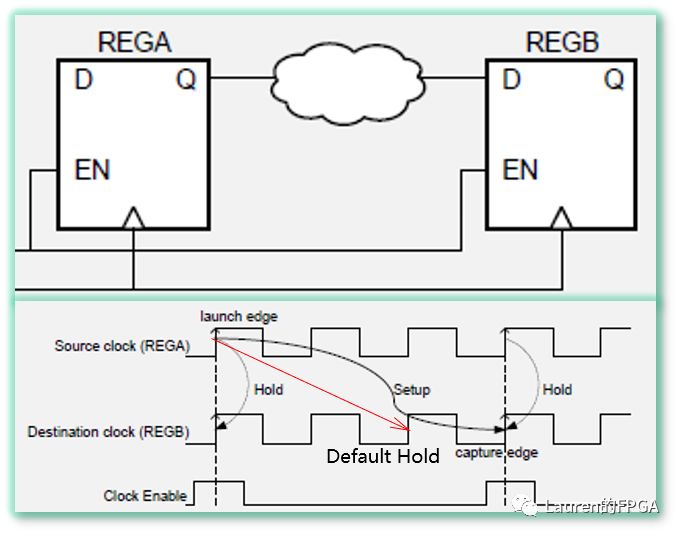

Hold Requirement為正的可能情形出現在使用多周期路徑約束的時序路徑中。如下圖所示,時鐘使能信號EN使得路徑的Setup Requirement為3個時鐘周期,但Hold Requirement仍應為0。

圖片來源 page 4, ug1292

在此情況下,應采用如下圖所示的多周期路徑約束。其中的第2條約束是對hold的調整,卻往往容易被遺漏。對于-hold,它表示相對于缺省捕獲沿(圖中的Default hold),實際捕獲沿應回調的時鐘周期個數。

對于過大的WHS或THS,應在布線之前做一些優化,盡可能地降低WHS和THS。為此,可在phys_opt_design階段采取如下圖所示的幾個措施。

其中方法(1)是在兩個同步時序元件之間插入與至相反的時鐘沿觸發的寄存器,將該路徑一分為二,該方法的前提是建立時間不會被惡化。方法(2)至方法(4)都是在路徑中插入LUT1。方法(2)只在WHS最大的路徑中插入LUT1;方法(3)則是在更多的路徑中插入LUT1;方法(4)則是在-directive為Explore的基礎上進一步修正保持時間違例,等效于-directive Explore +-aggressive_hold_fix。

-

寄存器

+關注

關注

31文章

5423瀏覽量

123418 -

信號

+關注

關注

11文章

2843瀏覽量

77928 -

時鐘

+關注

關注

11文章

1884瀏覽量

132855

原文標題:深度解析ug1292(4)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

S32K344 SPI數據引腳長時間保持高電壓后會出現數據錯誤怎么解決?

ADS1112的讀出的AD值就會保持不變,好長一段時間以后才會恢復,為什么?

ADC采樣保持過程的具體時間要如何確定?

使用瑞薩AnalogPAK SLG47001/03節省開發時間

軸承結構生產工藝流程柴油機軸承的結構與安裝

TPL5010死機時,DONE一直保持高電平,當超過看門狗的設定時間后,MCU會被PL5010復位嗎?

使用NTP,該如何同步時間?一文詳解!

OPA615峰值無法保持怎么解決?

OPA860做峰值保持電路,無法實現峰值保持的功能是為什么?

用混合信號示波器識別建立和保持時間違規

解決保持時間違例流程

解決保持時間違例流程

評論