今天陸妹給大家整理了一些FPG的知識點和FPGA的進階路線,小本本準備好,要開始劃重點嘍。

FPGA工作原理

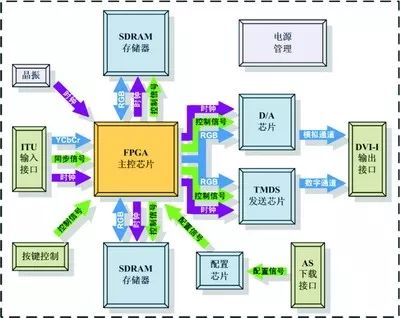

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個新概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。

FPGA的基本特點主要有:

1)采用FPGA設計ASIC電路,用戶不需要投片生產,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC電路的中試樣片。

3)FPGA內部有豐富的觸發器和I/O引腳。

4)FPGA是ASIC電路中設計周期最短、開發費用最低、風險最小的器件之一。

5) FPGA采用高速CHMOS工藝,功耗低,可以與CMOS、TTL電平兼容。

可以說,FPGA芯片是小批量系統提高系統集成度、可靠性的最佳選擇之一。

FPGA是由存放在片內RAM中的程序來設置其工作狀態的,因此,工作時需要對片內的RAM進行編程。用戶可以根據不同的配置模式,采用不同的編程方式。

加電時,FPGA芯片將EPROM中數據讀入片內編程RAM中,配置完成后,FPGA進入工作狀態。掉電后,FPGA恢復成白片,內部邏輯關系消失,因此,FPGA能夠反復使用。FPGA的編程無須專用的FPGA編程器,只須用通用的EPROM、PROM編程器即可。

當需要修改FPGA功能時,只需換一片EPROM即可。這樣,同一片FPGA,不同的編程數據,可以產生不同的電路功能。因此,FPGA的使用非常靈活。

FPGA常用術語

1:LCA(Logic Cell Array):邏輯單元陣列,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。

2: IOB(Input Output Block):可編程輸入輸出單元,為了便于管理和適應多種電器標準,FPGA的IOB被劃分為若干個組(bank),每個bank的接口標準由其接口電壓VCCO決定,一個bank只能有一種VCCO,但不同bank的VCCO可以不同。只有相同電氣標準的端口才能連接在一起,VCCO電壓相同是接口標準的基本條件。

3:CLB(Configurable Logic Block):可配置邏輯模塊,是FPGA內的基本邏輯單元,每個CLB都包含一個可配置開關矩陣,此矩陣由4或6個輸入、一些選型電路(多路復用器等)和觸發器組成。 在賽靈思公司公司的FPGA器件中,CLB由多個(一般為4個或2個)相同的Slice和附加邏輯構成。

4:Slice:是賽靈思公司公司定義的基本邏輯單位,一個Slice由兩個4輸入的函數、進位邏輯、算術邏輯、存儲邏輯和函數復用器組成。

5:LUT(Look-Up-Table):查找表。本質上就是一個RAM,目前FPGA中多使用4輸入的LUT,所以每一個LUT可以看成一個有4位地址線的 的RAM。

6:DCM(數字時鐘管理模塊):提供數字時鐘管理和相位環路鎖定。

7:BRAM(嵌入式塊RAM):塊RAM可被配置為單端口RAM、雙端口RAM、內容地址存儲器(CAM)以及FIFO等常用存儲結構。單片塊RAM的容量為18k比特,即位寬為18比特、深度為1024,可以根據需要改變其位寬和深度,但要滿足兩個原則:首先,修改后的容量(位寬 深度)不能大于18k比特;其次,位寬最大不能超過36比特。當然,可以將多片塊RAM級聯起來形成更大的RAM,此時只受限于芯片內塊RAM的數量,而不再受上面兩條原則約束。

必須精通的5項基本功

對于FPGA設計者來說,要練好5項基本功:仿真、綜合、時序分析、調試、驗證,

1.、仿真:Modelsim,QuartusII(Simulator Tool)

2.、綜合:Quartus II (Compiler Tool, RTL Viewer,Technology Map Viewer, Chip Planner)

3、 時序:Quartus II (TimeQuest Timing Analyzer, Technology Map Viewer, Chip Planner)

4、調試:Quartus II (SignalTap II Logic Analyzer, Virtual JTAG, Assignment Editor)

5、驗證:Modelsim, Quartus II(Test Bench Template Writer)

HDL語言與FPGA設計的5項基本功是相輔相成的。雖然它不是FPGA設計的全部,但是HDL語言在FPGA的整個設計流程中都是有體現的。

對于FPGA設計者來說,用好“HDL語言的可綜合子集”可完成FPGA設計中50%的工作——設計編碼。練好仿真、綜合、時序分析這3項基本功,對于學習“HDL語言的可綜合子集”有如下幫助:

1. 通過仿真,可以觀察HDL語言在FPGA中的邏輯行為。

2. 通過綜合,可以觀察HDL語言在FPGA中的物理實現形式。

3. 通過時序分析,可以分析HDL語言在FPGA中的物理實現特性。

同樣,用好“HDL語言的驗證子集”,可以完成FPGA設計另外50%的工作——調試驗證。

1. 搭建驗證環境,通過仿真的手段可以檢驗FPGA設計的正確性。

2. 全面的仿真驗證可以減少FPGA硬件調試的工作量。

3.把硬件調試與仿真驗證方法結合起來,用調試解決仿真未驗證的問題,用仿真保證已經解決的問題不在調試中再現,可以建立一個回歸驗證流程,有助于FPGA設計項目的維護。

FPGA設計者的這5項基本功不是孤立的,必須結合使用,才能完成一個完整的FPGA設計流程。反過來說,通過完成一個完整的設計流程,才能最有效地練習這5項基本功。對這5項基本功有了初步認識,就可以逐個深入學習一些,然后把學到的知識再次用于完整的設計流程。如此反復,就可以逐步提高設計水平。采用這樣的循序漸進、螺旋式上升的方法,只要通過培訓入了門,就可以自學自練,自我提高。

FPGA設計人員的進階路線

從技術層面來講,可編程邏輯范圍是目前和將來半導體行業最活潑的范圍之一,不再是繁多地用于IC設想的原型考證,更多地用于提供集成的零碎級處置計劃。古代的FPGA不再僅僅是可編程邏輯,而是介于ASIC和FPGA之間的混合芯片,包括微處置器、收發器以及很多其它單元。所以對FPGA設想職員的請求也越來越高,已超出繁多的邏輯設想范圍。因而,關于FPGA初學者來講,需求明白團體的進階道路,進而把握疾速開拓的辦法。下面給出作者團體的一些觀念。

1

熟習一門硬件設想言語(VHDL或Verilog HDL),由于不論在哪種運用范圍,HDL言語都是FPGA開拓的根底。目前國際運用Verilog HDL言語的開拓職員較多一些,因而引薦讀者進修Verilog HDL。正因如此,本書的實例都經過Verilog HDL完成,并在附錄中給出其扼要的語法闡明。

2

把握ISE Design Suit相關軟件的運用辦法。ISE軟件能夠完成設想輸出、分析、仿真、完成和下載,涵蓋了FPGA開拓的全進程,從中讀者能夠逼真領會到FPGA開拓全進程。關于嵌入式開拓職員,還需求把握EDK軟件操縱。當把握軟件的根本用法后,能夠深化了解各工具組件,如分析工具XST、布局布線工具PAR等的運轉機制,以便更好地在設想中應用其特性。

3

熟習XilinxFPGA芯片,包括不同類型資源的功能特性和運用辦法。此時,Xilinx所公布的文檔是首要參考材料。Xilinx針對每個系列的FPGA都提供了豐厚而片面的文檔,所以在開端任何一個系列的FPGA設想前,最好到Xilinx網站,將該系列FPGA的頁面上將一切的文檔都下載上去,然后有針對性的做參考。

4

參考xilinx推出的開拓板以及相應的參考設想,這是向初級進階最有價值的局部。Xilinx在網上針對每個系列的fpga都有文檔闡明,并都給出原理圖。其開拓板的文檔闡明十分具體具體,也很標準,有很大的參考價值。此外,在那些開拓板里也有眾多的核心接口電路,根本涵蓋了常用的運用場所。參考核心電路芯片的數據手冊,細心領會設想的細節和運用辦法。作為硬件工程師,閱讀手冊是一項根本技藝。當然,在具有硬件平臺的根底上,參考Xilinx網上的開拓板是進階道路中捷徑的捷徑。

5

入手調通一塊板子。有PCB設想才干的讀者,可自行設想;否則可購置相應的開拓板,將下面一切的硬件外設調通,并參照相似的開拓板,獨立完成Xilinx官方的參考設想。完成這一步,就步入初級設想的大門了。

6

由于FPGA芯片以及開拓技術開展很快,因而不只要在任務中累積經歷,還該當關心該行業的新技術和新意向,只要這樣才干一直站在高處。

全體看來,FPGA開拓入門復雜,進階階段不只難度較大、所需學問面廣,還是一個煩瑣的任務。同時假如想從底層更深化的了解硬件設想,還需需求深沉的實際支撐。因而FPGA開拓是一條平整但十分峻峭的路。

-

FPGA

+關注

關注

1643文章

21966瀏覽量

614144 -

FPG

+關注

關注

1文章

54瀏覽量

80232 -

觸發器

+關注

關注

14文章

2032瀏覽量

61880

原文標題:待查收:一些FPG的知識點 & FPGA的進階路線

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

整理了有關pcb設計的一些技巧分享給大家

記錄一些飛控開發過程的知識點

單片機的通信數據傳輸一些知識點資料說明

整理了一些FPG的知識點和FPGA的進階路線

整理了一些FPG的知識點和FPGA的進階路線

評論