Vivado? Design Suite 提供兩種方法可加速產(chǎn)品上市進(jìn)程,提高工作效率。可構(gòu)建 Vivado 布局布線。在任何設(shè)計(jì)階段處理任何類型的 ECO 問題,并可加快運(yùn)行時(shí)間,確保時(shí)序收斂進(jìn)程。

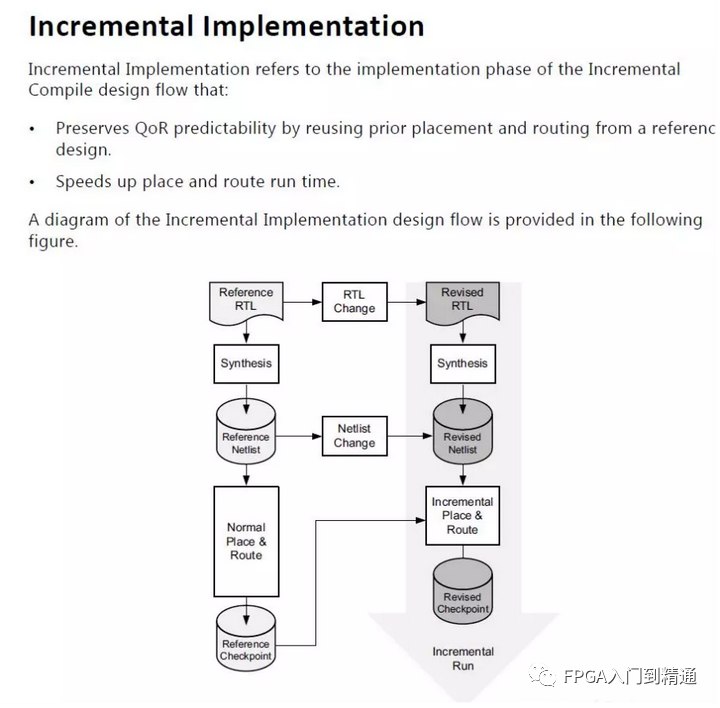

增量編譯:使用增量編譯滿足最后時(shí)刻 HDL 變動(dòng)需求,僅針對(duì)已變動(dòng)邏輯進(jìn)行布局布線,從而可節(jié)省時(shí)間。

P&R 數(shù)據(jù)重復(fù)使用為時(shí)序驅(qū)動(dòng),可在不影響性能的情況下,加速運(yùn)行時(shí)間。

平均速度比標(biāo)準(zhǔn)布局布線快 1 倍。

設(shè)計(jì)收斂保存可減少并加速迭代。

器件編輯器:使用器件編輯器通過強(qiáng)大的圖形界面,以外科手術(shù)般的高精度編輯布局布線設(shè)計(jì)。

手工輔助布線可提供各種建議布線,在避免猜測(cè)與犯錯(cuò)的情況下,加速達(dá)到目標(biāo)的進(jìn)程。

廣泛的交叉探測(cè)可幫助用戶便捷管理邏輯至物理的分配。

設(shè)計(jì)變動(dòng)記錄為 Tcl 命令,有利于回放與腳本處理。

增量編譯相對(duì)于器件編輯還是容易一些。本文主要講述增量編譯方法。

當(dāng)RTL代碼修改較少時(shí),使用增量編譯功能可以提高工程的編譯速度,Incremental Compile增量編譯是Vivado提供的一項(xiàng)高階功能。目的旨在當(dāng)設(shè)計(jì)微小的改變時(shí),重用綜合和布局布線的結(jié)果,縮短編譯時(shí)間。

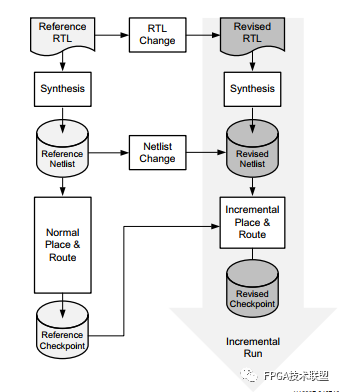

增量編譯的流程如下:

增量編譯是以已經(jīng)編譯和布局布線后的DCP文件為基礎(chǔ),當(dāng)我們需要做微小的改動(dòng)是,便可以使用增量編譯來實(shí)現(xiàn)。這里微小改動(dòng)主要包括有:

RTL代碼的微小修改

網(wǎng)表的微小修改,比如增加或者改變ILA

需要注意的是:這里微小的改懂是指與當(dāng)前設(shè)計(jì)相比變化非常小,其相似度大于95%時(shí),增量編譯的效果最好。而相似度小于75時(shí),工具的增量編譯就失效了。有時(shí)候一些全局變量修改,網(wǎng)表的改動(dòng)是非常大的,總線位寬的變化,網(wǎng)表的改動(dòng)也非常大。

增量編譯設(shè)置:

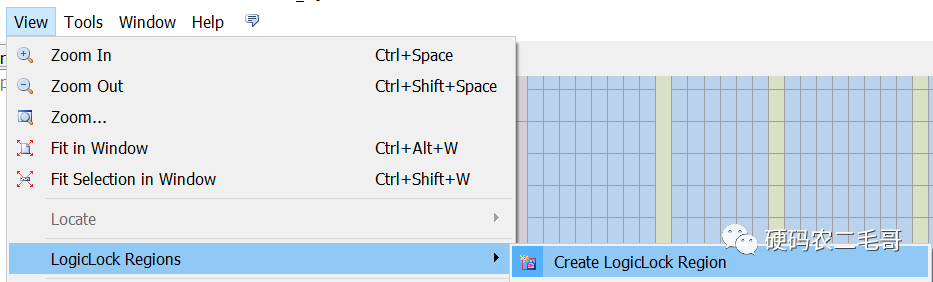

在項(xiàng)目模式下:在Vivado里面,使能IncrementalCompile的方式非常簡(jiǎn)單,在Impl run上右鍵選擇“Set Incremental Compile…”,然后設(shè)置相應(yīng)的參考dcp文件即可。

在非項(xiàng)目模式下:

在 opt_design 后運(yùn)行以下命令:

%read_checkpoint -incremental reference_routed.dcp

-

RTL

+關(guān)注

關(guān)注

1文章

389瀏覽量

61090 -

編輯器

+關(guān)注

關(guān)注

1文章

822瀏覽量

32023

原文標(biāo)題:增量編譯(Incremental Compile)提高Vivado編譯效率

文章出處:【微信號(hào):gh_873435264fd4,微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

淺析可提升Vivado編譯效率的增量編譯方法

誰(shuí)能縮短大容量FPGA的編譯時(shí)間?增量式編譯QIC!

Vivado中的Incremental Compile增量編譯技術(shù)詳解

Vivado Design Suite 2015.3新增量編譯功能介紹

引入增量編譯流程進(jìn)行調(diào)試的好處與步驟

Vivado 2015.3中的新增量編譯功能介紹

Vivado 2015.3的新增量編譯功能

如何在Vivado中實(shí)現(xiàn)邏輯鎖定和增量編譯工程實(shí)例說明

Vivadoz中增量編譯與設(shè)計(jì)鎖定

Vivado里如何手動(dòng)調(diào)整編譯順序

Quartus中的邏輯鎖定與增量編譯

Vivado增量編譯的基本概念、優(yōu)點(diǎn)、使用方法以及注意事項(xiàng)

淺談Vivado編譯時(shí)間

每次Vivado編譯的結(jié)果都一樣嗎

講述增量編譯方法,提高Vivado編譯效率

講述增量編譯方法,提高Vivado編譯效率

評(píng)論