可編程邏輯器件基礎(chǔ)

1、數(shù)字邏輯設(shè)計歷史-------了解歷史進展

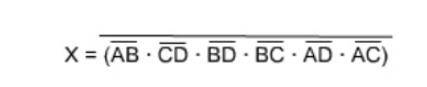

開始時:有復雜的邏輯關(guān)系,是我們初學者剛剛接觸的數(shù)電方面的基礎(chǔ)應用,設(shè)計一個基礎(chǔ)的TTL邏輯,根據(jù)真值表-----卡諾圖-----簡歷函數(shù)式邏輯表達式,舉個例子:X=AB+CD+BD+BC+AD+AC,需要很多的基礎(chǔ)邏輯單元,但是如果利用異或關(guān)系,可轉(zhuǎn)換成:

利用這樣的組合邏輯,這樣可以將數(shù)量眾多的基本邏輯單元簡化,硬件相對變簡單了。

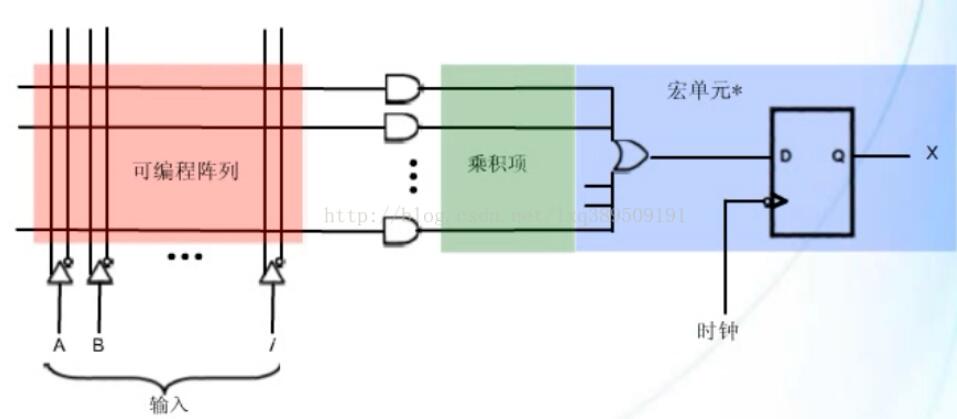

如果邏輯功能和寄存器組合到一個部件,通過布線(布線相當于一種控制)就可以得到一個簡單的PAL---可編程陣列邏輯,一種簡單的可編程控制單元,器件中的數(shù)量變少,占用更少的電路板,設(shè)計靈活,可防止逆向剖析,容易更新設(shè)計。

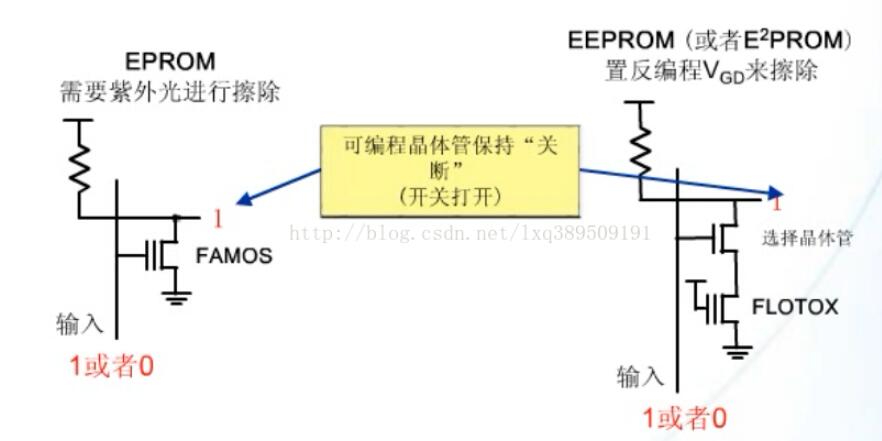

針對PAL的編程技術(shù)實質(zhì)(當前閃存技術(shù)的關(guān)鍵):陣列交叉(跨線)上的浮柵型晶體管(含有第二個柵極,浮動柵極)在加上編程電壓后,不會導通。以下兩種晶體管不做任何設(shè)置,都可用作N型晶體管,柵極接地時,源級和漏極導通。當柵極設(shè)置電壓后,電子被限制在浮動柵極,縱使浮動柵極設(shè)置電壓值,晶體管依舊不導通,這樣總是關(guān)斷,相當于一個開關(guān)。

2、可編程邏輯基本技術(shù)

了解器件本身:

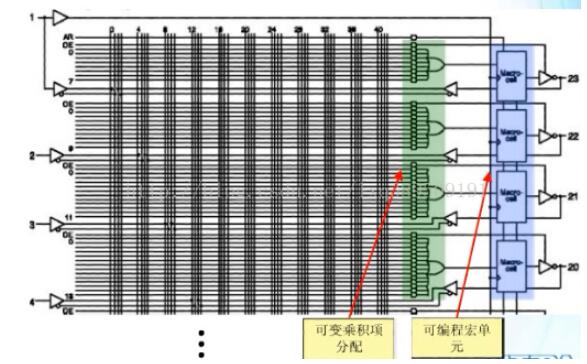

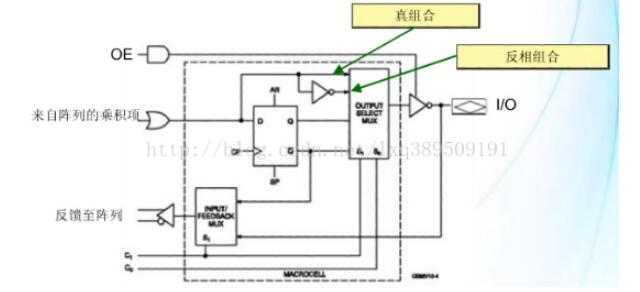

從PAL到可編程邏輯器件PLD,在單個器件中排列多個PAL陣列,存在可變的可乘積項分配和全面可編程宏單元。

可變的可乘積項分配:簡單的想法,改變或門、與門的數(shù)量,不會浪費邏輯門,不需要復雜的延時網(wǎng)絡(luò)。

靈活的可編程宏單元(主要進步):提供多種可編程選擇,實現(xiàn)乘積和輸出。

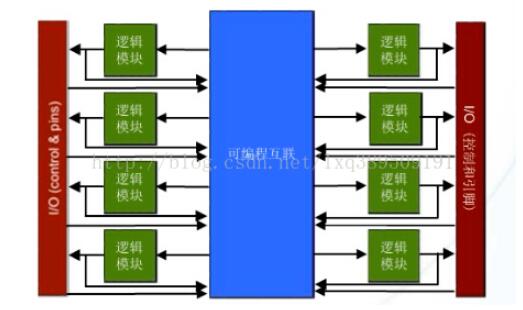

PLD進一步發(fā)展形成復雜的PLD(CPLD)-----在一個器件中,采用可編程互聯(lián)和I/O,連接多個PLD:

CPLD的特性:

CPLD邏輯模塊通常被稱為邏輯陣列模塊(LAB),每個LAB相當于一個PLD,含有4-20個宏單元,該宏單元還存在擴展項,提供可操控的乘積項分配和擴展,代價是額外的延時。即,建立一次乘積項就可以使用,大大減少了邏輯浪費。

LAB之間的互聯(lián)稱為可編程互聯(lián)陣列(PI或PIA),和PAL可編程陣列相同的編程技術(shù)(兩種晶體管,EPROM、EEPROM或者閃存技術(shù)編程),配置更高級,實現(xiàn)靈活的可編程關(guān)鍵,全局布線連接器件中的任何信號和任何目的位置。

單獨的I/O控制模塊,由PI將I/O引腳與LAB分開,I/O都有專用邏輯提供控制以及更多的功能,三態(tài)緩沖控制實現(xiàn)任意引腳的輸入、輸出和雙向功能。

采用JTAG進行在系統(tǒng)編程(ISP)

由于可編程邏輯越來越大、越來越復雜,必須放在特定的條件下編譯,器件放在特殊的單元,或者器件上加一些特殊裝置,不能在線編譯,故設(shè)計了一種和I/O分開的編程接口,幾乎所有的FPGA都使用JTAG接口,簡單的4、5線串行接口,構(gòu)成單個器件長1位寄存器或者多個器件的JTAG鏈,可用于器件自檢測或者系統(tǒng)編程(ISP),當PLD硬件生成EPROM編程電壓,由JTAG接口進行控制,簡化了實驗室自編程。

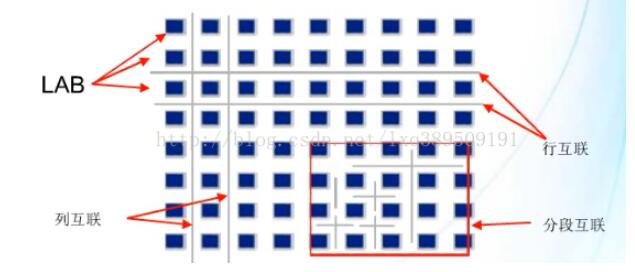

從CPLD到FPGA:理論上我們可以一直增加LAB,但是這樣大大增加了額外的全局布線,但是如果LAB本身重新排列一個陣列中呢?這就是FPGA的由來。

現(xiàn)場可編程門陣列(FPGA):LAB排列在大型陣列中,器件可以現(xiàn)場編程或重新編程,行列可編程互聯(lián),通過這中互聯(lián)方式(在行列之間設(shè)置互聯(lián)布線)可以跨越所有或者部分的陣列。

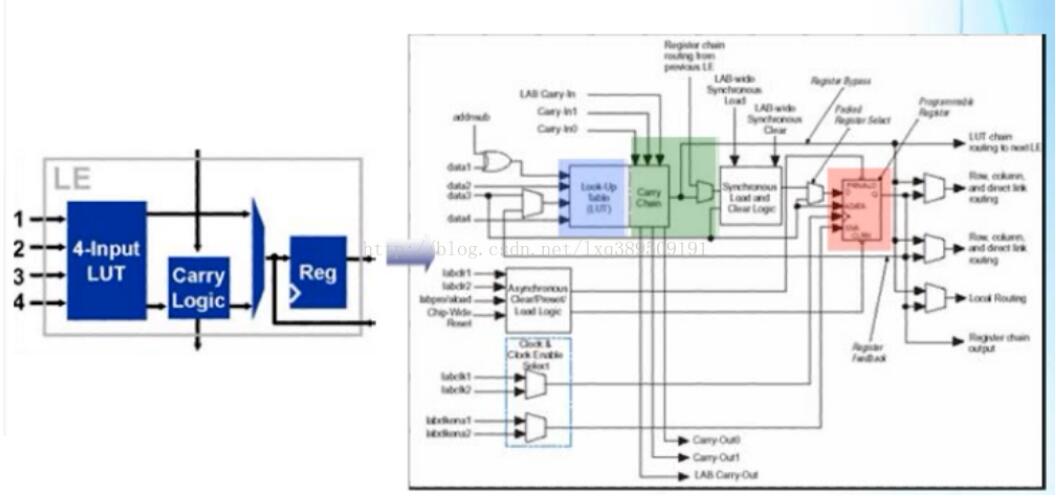

FPGA的LAB設(shè)計和CPLD不同,沒有乘積項和宏單元,F(xiàn)PGA-LAB由邏輯單元(LE)構(gòu)成,LE級聯(lián)更容易建立復雜的功能,LE實質(zhì)是一個4位查找表(LUT)、進位邏輯、輸出寄存器邏輯構(gòu)成。

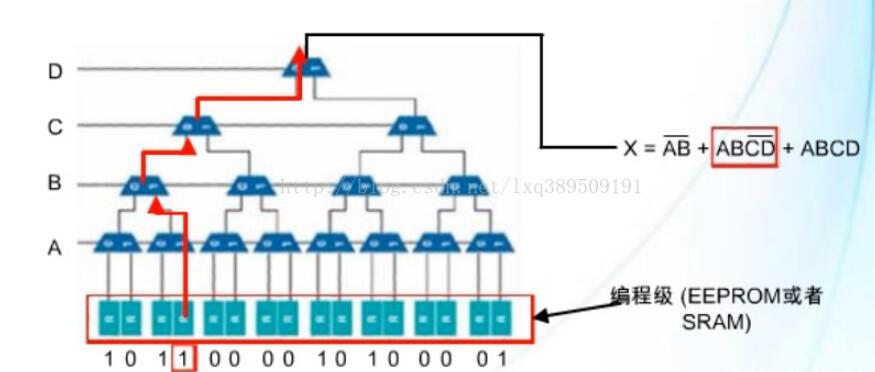

4位查找表 LUT替代了CPLD中的乘積項陣列,LUT是由一系列級聯(lián)復用的器件構(gòu)成,LUT輸入作為選擇線,復用輸入作為高或者低邏輯電平,之所以邏輯被稱作查找表,通過差找正確的編程級,來選擇輸出,根據(jù)輸入的值通過復用輸入,將輸出送到正確的位置,編程級的選擇基于函數(shù)真值表,故可以靈活的建立一個組合函數(shù)(級聯(lián)復用器),減少邏輯資源浪費。

LE同步部分來自可編程寄存器,該寄存器和CPLD宏單元相似,但配置靈活,配置為D\T\JK或者SR觸發(fā)器工作,一般由全局的時鐘來驅(qū)動時鐘,任何時鐘可驅(qū)動任何LE,可通過其他邏輯或者IO進行寄存器的異步控制,器件還可以反饋回LUT,產(chǎn)生嚴格的組合邏輯功能,這種寄存器只使用存貯、同步功能,這種靈活的LE輸出級適合所有類型的邏輯操作。

LE和宏單元不同之處在于進位邏輯和LAB寄存器鏈邏輯,LE之間存在進位bit鏈,這種進位可以輸出到別的LE,也可以輸出到互聯(lián)中,寄存器輸出可以鏈接至LAB中的其他LE寄存器,形成和LUT無關(guān)的移位寄存器(適合DSP峰作),增強資源管理。

更高級的FPGA使用自適應邏輯模塊(ALM)代替LE,提高性能和資源利用率,使用自適應的LUT(ALUT)可以任意劃分,智能資源管理。

FPGA布線

所有器件資源都可以和器件中的任何布線連接,分為本地互聯(lián)(LE之間互聯(lián)、相鄰LAB直接連接)、行列互聯(lián)(固定長度布線、跨過多個LAB)。

FPGA IO單元

高級可編程模塊可直接連接至行或者列互聯(lián),具有多種優(yōu)良特性,同時存在特殊的邏輯。

其他典型FPGA特性

采用專用功能硬件模塊代替某些LAB,存儲器模塊、嵌入式乘法器、高速收發(fā)器。(多查一下手冊,看是否滿足要求)

FPGA編程

大部分FPGA使用SRAM單元技術(shù)(基本是個鎖存器)對互聯(lián)和LUT功能進行編程,必須在上電時進行編程,數(shù)據(jù)易丟失。FPGA編程信息必須存儲在某一位置,以便在上電時對器件進行編程。主動編程方式:上電時FPGA自動控制編程順序;被動編程:智能主機(CPU)控制編程;JTAG編程:實驗室PC端編程。

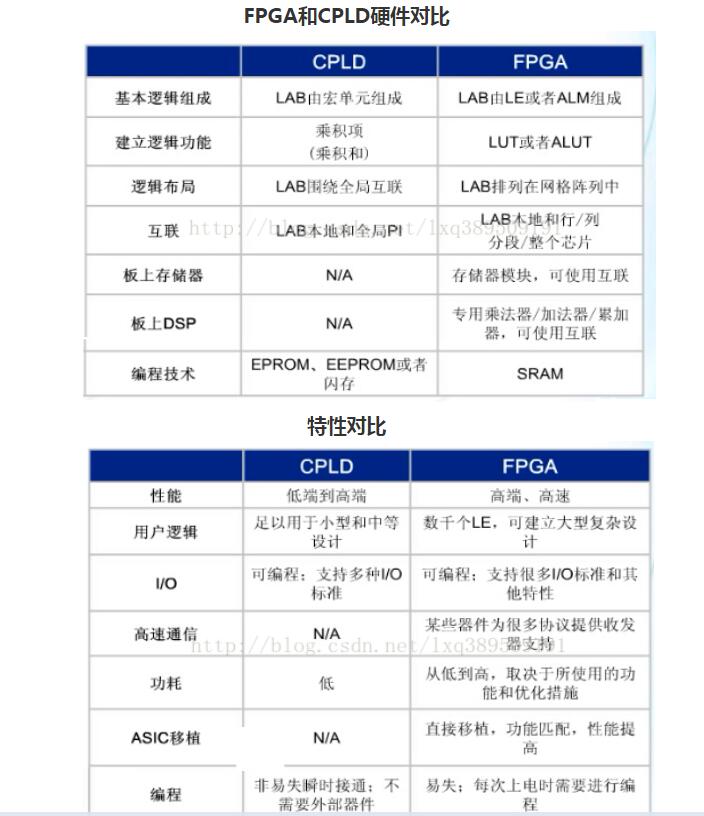

3、對比CPLD和FPGA

-

可編程邏輯

+關(guān)注

關(guān)注

7文章

524瀏覽量

44637 -

可編程邏輯器件

+關(guān)注

關(guān)注

5文章

145瀏覽量

30586

發(fā)布評論請先 登錄

fpga和cpu的區(qū)別 芯片是gpu還是CPU

什么是PLD的定義和應用 PLD與FPGA的區(qū)別和聯(lián)系

CPLD 在汽車電子中的應用

CPLD 與 ASIC 的比較

如何優(yōu)化 CPLD 性能

CPLD 的功耗控制技巧

CPLD 優(yōu)勢與劣勢分析

CPLD 應用場景分析

CPLD 與 FPGA 的區(qū)別

PLD設(shè)計流程的詳細步驟

如何選擇合適的PLD型號

5CGTFD7D5F27C7N Intel/Altera可編程邏輯器件(CPLD/FPGA)

德州儀器可編程邏輯器件解決方案

德州儀器推出全新可編程邏輯產(chǎn)品系列

德州儀器 (TI) 全新可編程邏輯產(chǎn)品系列助力工程師在數(shù)分鐘內(nèi)完成從概念到原型設(shè)計的整個過程

可編程邏輯器件基礎(chǔ)

可編程邏輯器件基礎(chǔ)

評論