聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21982瀏覽量

614562 -

數據

+關注

關注

8文章

7246瀏覽量

91148 -

串口通信

+關注

關注

34文章

1636瀏覽量

56593

發布評論請先 登錄

相關推薦

熱點推薦

【正點原子FPGA連載】第十二章 動態數碼管顯示實驗

`1)實驗平臺:正點原子開拓者FPGA開發板2)平臺購買地址:https://item.taobao.com/item.htm?id=579

發表于 06-15 22:54

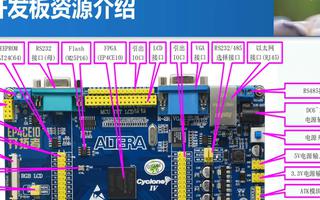

分享正點原子FPGA開發板全套資料

本帖最后由 100dongdong 于 2020-5-16 23:48 編輯

正點原子FPGA開拓者開發板,Intel(Altera) FPG

發表于 05-16 23:35

正點開拓者FPGA開發板使用問題

求問各位大佬,剛剛入門正點開拓者FPGA開發板,用板載pcf8591采集信號發生器單一頻率正弦波,再用ip核做fft,結果和matlab上fft不一樣,請問是怎么回事呢?

發表于 01-04 09:34

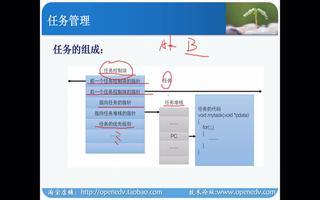

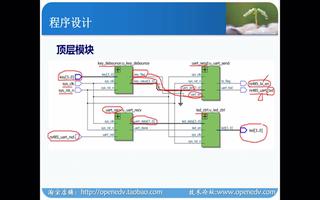

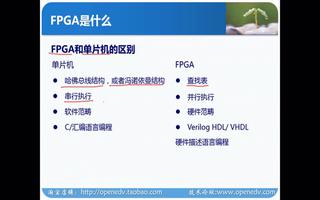

正點原子開拓者FPGA Qsys視頻:uCOS II任務管理與時間管理(2)

該課程是正點原子團隊編寫,詳細講解了quartus中的qsys。也可以從我頭像點進去看FPGA verilog相關的視頻。

正點原子開拓者FPGA:RS485串口通信實驗

RS485是一個定義平衡數字多點系統中的驅動器和接收器的電氣特性的標準,該標準由電信行業協會和電子工業聯盟定義。使用該標準的數字通信網絡能在遠距離條件下以及電子噪聲大的環境下有效傳輸信號。RS-485使得廉價本地網絡以及多支路通信鏈路的配置成為可能。

正點原子開拓者FPGA:串口通信實驗

正點原子開拓者FPGA:串口通信實驗

評論