UltraRAM 是 UltraScale + 系列中最新的存儲器模塊,能實現(xiàn)高達 500Mb 的總片上存儲容量,相當于賽靈思 28nm FPGA 片上存儲器容量的 6 倍。

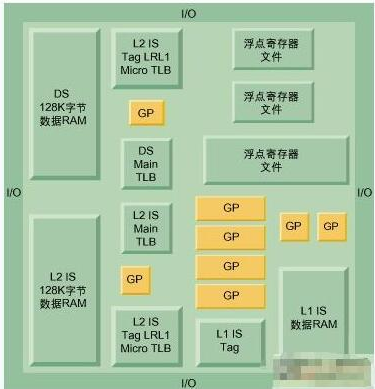

傳統(tǒng)的 FPGA 和 SoC 包含的片上存儲器以 block RAM 和分布式 RAM 的形式存在。由于器件能以更高數(shù)據(jù)速率處理更多數(shù)據(jù),因此越發(fā)需要將數(shù)據(jù)緩沖或存儲在靠近處理器的位置。

UltraScale+ 系列中的新產(chǎn)品是一款容量更大的稱為 UltraRAM 的靈活存儲器模塊。UltraRAM 模塊可級聯(lián)在一起構(gòu)成更大的片上存儲器。

在設(shè)計中使用 UltraRAM 很簡單,因為賽靈思提供了所有必要工具,利用這些工具可以在設(shè)計中集成功能強大的最新模塊。

緩沖與存儲的需求增加

UltraScale+ FPGA 和 MPSoC 能夠傳輸和處理的數(shù)據(jù)比前一代器件多得多。靈活的級聯(lián)功能使得 UltraRAM 模塊能夠采用多種配置——既可單獨使用,也可在器件中將所有模塊連 接在一起使用。這使得用戶能夠構(gòu)建大小適合應(yīng)用需求的存儲器陣列,并省去一些 PCB 上的外部存儲器 組件,例如 QDR SRAM。

UltraRAM 細節(jié)與特性

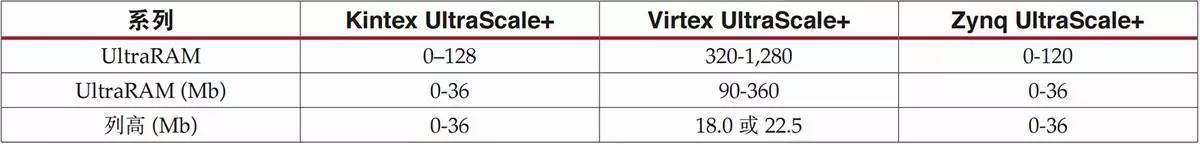

大多數(shù) Kintex UltraScale+ 和 Zynq UltraScale+ 器件都包含一列 UltraRAM ;高端 Virtex UltraScale+ FPGA 則包含多達 5 列 UltraRAM。在 Kintex UltraScale+ 和 Zynq UltraScale+ 器件中,級聯(lián)得到的 RAM 陣列可高達 36Mb,在 Virtex UltraScale+ 器件中可達到 22.5Mb。Virtex UltraScale+ 系列中,所有 UltraRAM 列都 可通過光纖路由連接在一起,在最大器件中可構(gòu)成容量達 360Mb 的存儲器陣列。

功耗降低

UltraRAM 提供各種內(nèi)置功能以最大化功率效率,通常無需用戶干預(yù)。這些功能包括 :

將設(shè)計中不用的 UltraRAM 斷電

自動對不使用的流水線寄存器進行時鐘門控

當 UltraRAM 長時間不使用時,使其進入休眠模式

在設(shè)計中使用 UltraRAM

UltraScale+ 產(chǎn)品組合使用賽靈思的 Vivado Design Suite。設(shè)計工具提供一系列代碼模板,可幫助用戶 成功鎖定器件內(nèi)的可用資源。有三種方法可以在 RTL 設(shè)計中使用 UltraRAM :

編寫代碼以調(diào)用存儲器 ;

實例化器件原語 ;

使用最近添加的賽靈思參數(shù)化宏 (XPM)。

創(chuàng)建存儲器陣列

UltraRAM 架構(gòu)擴展性非常強,允許很多個 UltraRAM 模塊高效地連接在一起,以構(gòu)成深邏輯存儲器, 僅使用很少甚至無需架構(gòu)資源,而且訪問時延相對較短。

寄存器和流水線化

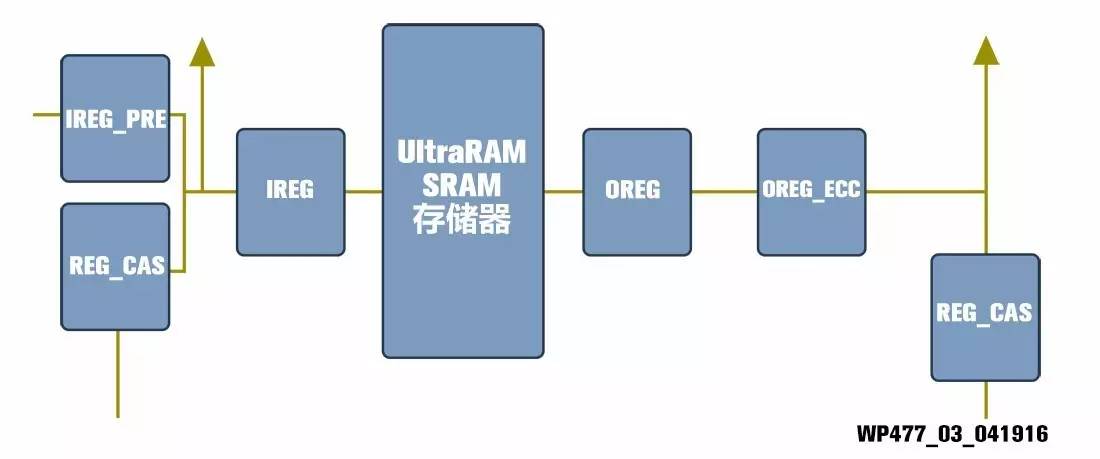

每個 UltraRAM 包含多個輸入和輸出寄存器,如圖 3 所示,其中有一些是可選的,取決于配置情況和所 需的功能。

圖3:UltraRAM 寄存器

遷移到 UltraRAM

在做這個步驟之前,用戶一定要知道所選目標器件中不同存儲器資源的數(shù)量。表 1 給出了不同 UltraScale+ 系列中 UltraRAM 的數(shù)量。在 Virtex UltraScale+ 器件中,可將所有 UltraRAM 連在一起,以構(gòu)成容量高達 360Mb 的多列陣列 ;不過,也可實現(xiàn)更為常用的 10Mb-144Mb 范 圍的多實例使用模型。

表1:UltraScale+ 產(chǎn)品組合中的 UltraRAM 資源

替代外部存儲器組件

高達 360Mb 的 UltraRAM 幾乎可配置成無數(shù)種方式,因此會有很多種使用模式。常見的 UltraRAM 使用模式是如果不實現(xiàn)在外部存儲器中,則可以將存儲器整合在 FPGA 或 MPSoC 中。

輸入多播

每個 UltraRAM 端口都可確定級聯(lián)模式中的事務(wù)處理是否屬于局部存儲器陣列。該功能可用來實現(xiàn)動態(tài) 的事務(wù)處理級寫單播、多播和廣播存儲器結(jié)構(gòu)。這種結(jié)構(gòu)可以構(gòu)成高效輸出緩沖存儲器開關(guān)的基礎(chǔ)。

結(jié)論

每個設(shè)計都需要和使用這樣或那樣的存儲器。將大容量、靈活的 UltraRAM 模塊添加到 UltraScale+ 產(chǎn)品 系列后,為用戶提供的片上存儲器容量比以往任何器件或競爭器件都要大。由于模塊可連接在一起構(gòu)成 不同大小的存儲器陣列,這樣用戶就能在設(shè)計中在需要的位置構(gòu)建理想的存儲器解決方案,消除了使用 外部 SRAM 組件所帶來的功耗和電路板復雜性。

-

賽靈思

+關(guān)注

關(guān)注

33文章

1797瀏覽量

132263 -

嵌入式存儲器

+關(guān)注

關(guān)注

0文章

24瀏覽量

12532

發(fā)布評論請先 登錄

如何實現(xiàn)嵌入式ASIC和SoC的存儲器設(shè)計?

嵌入式存儲器的設(shè)計方法是什么?

嵌入式系統(tǒng)使用的存儲器是如何進行劃分的

FPGA中嵌入式存儲器模塊的設(shè)計

嵌入式存儲器發(fā)展現(xiàn)狀

嵌入式存儲器內(nèi)建自修復技術(shù)

嵌入式芯片的存儲器映射

平板電腦如何選用嵌入式存儲器

嵌入式存儲器設(shè)計方案匯總

MRAM如何在嵌入式存儲器建立橋頭堡?

嵌入式硬件系統(tǒng)教程之嵌入式存儲技術(shù)的詳細資料說明

嵌入式存儲器如何來設(shè)計

FPGA中嵌入式塊存儲器的設(shè)計

嵌入式存儲器的巨大優(yōu)勢

嵌入式存儲器的巨大優(yōu)勢

評論