Vivado Design Suite 2016.1 現(xiàn)提供 SmartConnect 技術(shù)支持,能解決高性能數(shù)百萬(wàn)系統(tǒng)邏輯單元設(shè)計(jì)中的系統(tǒng)互聯(lián)瓶頸問題。

All Programmable技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布推出 Vivado Design Suite2016.1 的 HLx 版本。該全新套件新增了SmartConnect技術(shù)支持,能為 UltraScale 和 UltraScale+ 產(chǎn)品組合帶來前所未有的高性能。Vivado Design Suite2016.1 版本包含 SmartConnect 技術(shù)擴(kuò)展,可解決高性能數(shù)百萬(wàn)系統(tǒng)邏輯單元設(shè)計(jì)中的系統(tǒng)互聯(lián)瓶頸,從而讓 UltraScale 和 UltraScale+ 器件組合在實(shí)現(xiàn)高利用率的同時(shí),還能將性能進(jìn)一步提升20%-30%。

賽靈思 UltraScale+ 產(chǎn)品組合是業(yè)界唯一的一款基于 FinFET 的可編程技術(shù)。其包括 Zynq、Kintex和 VirtexUltraScale+ 器件,相對(duì)于 28nm 產(chǎn)品而言,性能功耗比提升 2-5 倍,能支持 5G 無線、軟件定義網(wǎng)絡(luò)和下一代高級(jí)駕駛員輔助系統(tǒng)等市場(chǎng)領(lǐng)先應(yīng)用。

賽靈思 SmartConnect 技術(shù)包括系統(tǒng)互聯(lián) IP 以及 UltraScale+ 芯片技術(shù)創(chuàng)新所帶來的最新優(yōu)化:

AXI SmartConnect IP:賽靈思的新型系統(tǒng)連接生成器將外設(shè)與用戶設(shè)計(jì)整合在一起。SmartConnect 創(chuàng)建的定制互聯(lián)功能能最好地滿足用戶的系統(tǒng)性能要求,從而能以更少的占用面積和功耗實(shí)現(xiàn)更高的系統(tǒng)吞吐量。現(xiàn)在,用戶可通過 Vivado Design Suite2016.1 版本中的 Vivado IP Integrator 搶先體驗(yàn)。

借用時(shí)間和有用的歪斜優(yōu)化:這些優(yōu)化技術(shù)得到新型 UltraScale+ 精細(xì)時(shí)鐘延遲插入功能的支持。這些全自動(dòng)化功能通過將時(shí)序裕量從設(shè)計(jì)的高速路徑轉(zhuǎn)移到關(guān)鍵路徑上,能夠緩解大的線路延遲,并讓設(shè)計(jì)運(yùn)行在更高時(shí)鐘頻率上。

流水線分析與重定時(shí):這些方法通過在設(shè)計(jì)中增加額外的流水線級(jí),并運(yùn)用自動(dòng)寄存器重定時(shí)優(yōu)化技術(shù),讓設(shè)計(jì)人員能夠進(jìn)一步提高性能。

供貨情況

Vivado Design Suite HLx 版本和嵌入式軟件開發(fā)工具 2016.1 版本現(xiàn)已開始供貨,歡迎下載。如需了解有關(guān)賽靈思軟件開發(fā)環(huán)境的更多信息,敬請(qǐng)?jiān)L問賽靈思軟件開發(fā)人員專區(qū)。

16nm UltraScale+ 系列FPGA、3D IC 和 MPSoC 憑借新型存儲(chǔ)器、3D-on-3D和多處理 SoC(MPSoC)技術(shù),繼續(xù)保持著“領(lǐng)先一代”的價(jià)值優(yōu)勢(shì)。為實(shí)現(xiàn)前所未有的高的性能和集成度,UltraScale+ 系列還采用了全新的 SmartConnect 互聯(lián)優(yōu)化技術(shù)。通過系統(tǒng)級(jí)的優(yōu)化,UltraScale+ 系列提供的價(jià)值遠(yuǎn)遠(yuǎn)超過了傳統(tǒng)工藝節(jié)點(diǎn)移植所帶來的價(jià)值,系統(tǒng)級(jí)性能功耗比相比 28nm 器件提升了 2-5倍,還實(shí)現(xiàn)了遙遙領(lǐng)先的系統(tǒng)集成度和智能化,以及最高級(jí)別的保密性與安全性。

-

賽靈思

+關(guān)注

關(guān)注

33文章

1797瀏覽量

132367 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

526瀏覽量

44771 -

16nm

+關(guān)注

關(guān)注

0文章

32瀏覽量

28185

發(fā)布評(píng)論請(qǐng)先 登錄

基于AMD Versal器件實(shí)現(xiàn)PCIe5 DMA功能

AMD Spartan UltraScale+ FPGA 開始量產(chǎn)出貨

賽思快訊 | 嘉興市委書記陳偉一行蒞臨賽思調(diào)研

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

易靈思邀您相約2025上海國(guó)際汽車工業(yè)展覽會(huì)

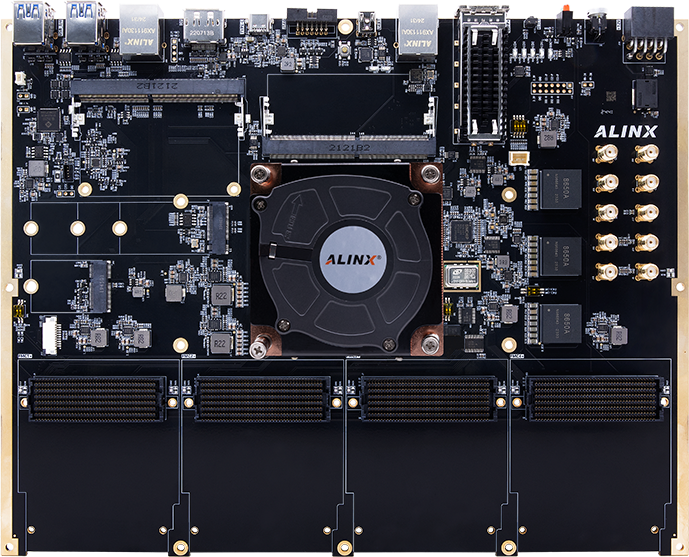

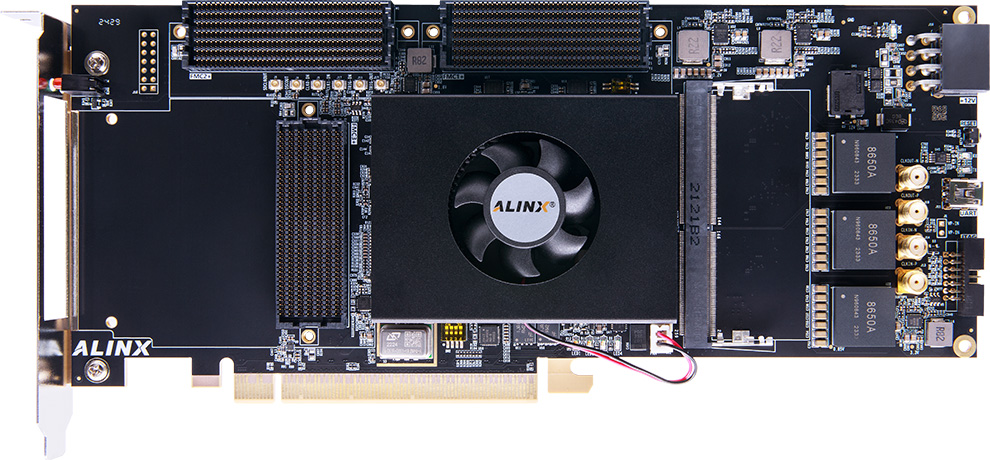

AI 應(yīng)用場(chǎng)景全覆蓋!解碼超高端 VU+ FPGA 開發(fā)平臺(tái) AXVU13F

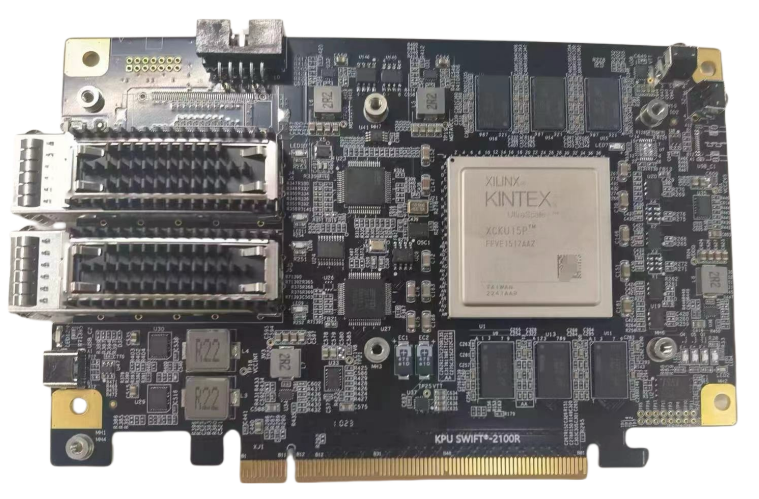

南京芯麒電子-基于KU15P的雙路100G光纖加速卡

今日看點(diǎn)丨美國(guó)擬管制16nm;Meta今年或開發(fā)出AI編程智能體

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

Zynq UltraScale+ MPSoC數(shù)據(jù)手冊(cè)

ALINX 發(fā)布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 綜合開發(fā)平臺(tái)

時(shí)序約束一主時(shí)鐘與生成時(shí)鐘

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評(píng)估套件

賽靈思擴(kuò)展SmartConnect技術(shù)為16nm UltraScale+器件實(shí)現(xiàn)性能突破

賽靈思擴(kuò)展SmartConnect技術(shù)為16nm UltraScale+器件實(shí)現(xiàn)性能突破

評(píng)論