中國北京-All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布首批Virtex UltraScale VU095 All Programmable FPGA已經(jīng)開始向客戶發(fā)貨,并將業(yè)界唯一20nm高端產(chǎn)品系列擴(kuò)展至單芯片400G和500G應(yīng)用。Virtex UltraScale VU095器件可為有線通信、測(cè)試測(cè)量、航空航天與軍用以及數(shù)據(jù)中心等多種不同應(yīng)用帶來前所未有的高性能、系統(tǒng)集成度和帶寬。此外,賽靈思還新增加了VirtexUltraScale系列另一款器件VU190 FPGA,該器件集成有近200萬個(gè)邏輯單元,超過130Mb的片上RAM容量,超過1000個(gè)并行I/O引腳數(shù),而且還擁有多達(dá)120個(gè)串行收發(fā)器。

VirtexUltraScale ASIC級(jí)系列產(chǎn)品利用FPGA和為客戶帶來領(lǐng)先一代產(chǎn)品價(jià)值的量產(chǎn)質(zhì)量級(jí)3D IC技術(shù),為業(yè)界提供了唯一可將系統(tǒng)級(jí)性能和集成度提升2倍以上,并將功耗降低多達(dá)50%的可編程方案。

VirtexUltraScale系列產(chǎn)品與Vivado設(shè)計(jì)套件和UltraFast設(shè)計(jì)方法進(jìn)行了協(xié)同優(yōu)化,可以在不降低性能的同時(shí),大幅提升生產(chǎn)力、可預(yù)測(cè)性,并實(shí)現(xiàn)出色的器件利用率。該系列內(nèi)含32.75 Gb/s芯片對(duì)芯片、芯片至光纖和28G背板收發(fā)器,并采用多個(gè)集成式ASIC級(jí)100G以太網(wǎng)和150GInterlaken內(nèi)核。賽靈思SmartCORE和LogiCORE解決方案提供了業(yè)經(jīng)驗(yàn)證的IP核,能滿足UltraScale設(shè)計(jì)豐富的功能構(gòu)建塊要求。UltraScale 20nm器件同時(shí)也可以無縫移植至未來的UltraScale 16nm FinFET器件。

賽靈思FPGA產(chǎn)品管理高級(jí)總監(jiān)Dave Myron指出:“隨著VU095器件的發(fā)貨,客戶可以立即著手實(shí)現(xiàn)要求最嚴(yán)苛的設(shè)計(jì)。而Virtex UltraScale VU190 FPGA更是創(chuàng)立了一個(gè)突破性的技術(shù)里程碑,它使得我們的客戶能夠推出高集成度、超高性能的系統(tǒng),可比市場(chǎng)上其它同類方案領(lǐng)先整整一代。”

供貨情況

首批Virtex UltraScale器件樣片現(xiàn)已開始發(fā)貨。支持UltraScale 器件的Vivado設(shè)計(jì)套件現(xiàn)在也已開始供貨。

關(guān)于20nm UltraScale系列

賽靈思UltraScale器件擁有業(yè)界唯一的ASIC級(jí)可編程架構(gòu)、Vivado ASIC增強(qiáng)型設(shè)計(jì)套件和UltraFast設(shè)計(jì)方法,可提供各種ASIC級(jí)的優(yōu)勢(shì)。UltraScale產(chǎn)品系列采用臺(tái)積公司(TSMC)的20SoC工藝技術(shù),所需功耗僅為目前市場(chǎng)上解決方案的一半,但卻將系統(tǒng)性能和集成度提升了2倍以上。這些器件同時(shí)還采用了下一代互聯(lián)技術(shù)、類ASIC時(shí)鐘、更強(qiáng)的的邏輯結(jié)構(gòu)、第二代量產(chǎn)質(zhì)量級(jí)的3D IC技術(shù)。不僅圖片了系統(tǒng)級(jí)的瓶頸問題,而且在不降低性能的同事讓器件保持了更高的利用率。

關(guān)于賽靈思

賽靈思是All Programmable器件、SoC和3D IC的全球領(lǐng)先供應(yīng)商。賽靈思公司行業(yè)領(lǐng)先的產(chǎn)品與新一代設(shè)計(jì)環(huán)境以及 IP 核完美地整合在一起,可滿足客戶對(duì)可編程邏輯乃至可編程系統(tǒng)集成的廣泛需求。

-

3D

+關(guān)注

關(guān)注

9文章

2952瀏覽量

109450 -

串行收發(fā)器

+關(guān)注

關(guān)注

0文章

14瀏覽量

9591 -

20nm

+關(guān)注

關(guān)注

0文章

73瀏覽量

87900

發(fā)布評(píng)論請(qǐng)先 登錄

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

易靈思2025 FPGA技術(shù)研討會(huì)北京站圓滿結(jié)束

NucleiStudio_IDE下調(diào)試一直報(bào)all ones錯(cuò)誤怎么解決?

國產(chǎn)EDA億靈思?接入DeepSeek

是否可以在不需要TSW3100的情況下單獨(dú)使用TSW3070軟件?

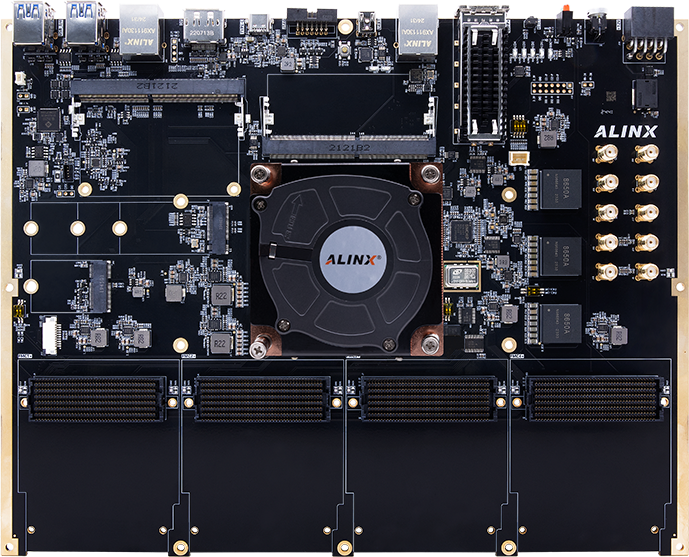

AI 應(yīng)用場(chǎng)景全覆蓋!解碼超高端 VU+ FPGA 開發(fā)平臺(tái) AXVU13F

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

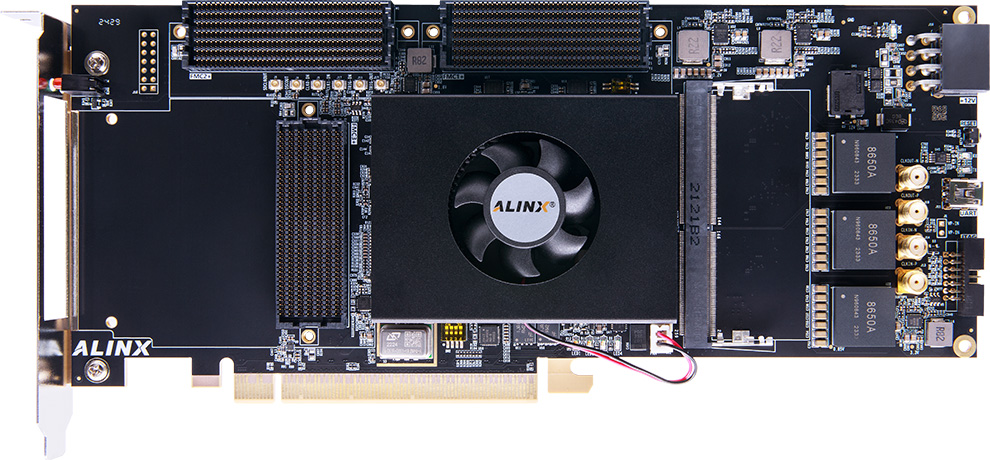

ALINX 發(fā)布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 綜合開發(fā)平臺(tái)

易靈思FPGA產(chǎn)品的主要特點(diǎn)

時(shí)序約束一主時(shí)鐘與生成時(shí)鐘

THS4503ID只要一上電就開始發(fā)燙,是正常的嗎?

賽思快訊 | 發(fā)展新質(zhì)生產(chǎn)力問道賽思?賽思如何下好“創(chuàng)新棋”?

賽靈思Virtex UltraScale VU095 All Programmable FPGA開始發(fā)貨

賽靈思Virtex UltraScale VU095 All Programmable FPGA開始發(fā)貨

評(píng)論