本篇討論的是有關(guān)CPU(在Zynq SoC中是指ARM處理器核)和FPGA的可編程邏輯架構(gòu)之間的機(jī)器視覺算法分割。

美國(guó)國(guó)家儀器公司(National Instruments)的Carlton Heard在新一期RTC雜志剛剛發(fā)表了一篇內(nèi)容翔實(shí)的標(biāo)題為《FPGA –將視覺技術(shù)提升至新高》的機(jī)器視覺處理方案文章,Heard寫道:

“視覺應(yīng)用程序必須依靠其他解決方案,而不是簡(jiǎn)單地依靠更快的處理器來提高速度。一種選擇是分割圖像處理算法,并行處理更多任務(wù),在視覺應(yīng)用程序當(dāng)中使用的算法非常適合于這樣處理。如SSE 、超線程和多核技術(shù)可以用于在不增加原始時(shí)鐘速率的情況下并行處理、執(zhí)行多個(gè)任務(wù)。不過,選擇這種方法也需要處理多個(gè)問題。除非所使用的軟件包將復(fù)雜性進(jìn)行抽象化,否則難以使用多線程編程軟件。必須在線程之間傳送數(shù)據(jù),這樣會(huì)出現(xiàn)存儲(chǔ)器拷貝和同步抖動(dòng)。此外,它通常是一個(gè)手動(dòng)過程,以利用現(xiàn)有的單線程圖像處理算法,并兼容多內(nèi)核。即使這樣,開銷問題往往禁止過多的并行處理,因?yàn)榇蠖鄶?shù)系統(tǒng)設(shè)計(jì)人員無法為所創(chuàng)建的測(cè)試單元購(gòu)買16內(nèi)核服務(wù)器級(jí)計(jì)算機(jī)。”

“使用FPGA的好處在于,它基本上是由軟件定義的硬件。因此,系統(tǒng)設(shè)計(jì)人員可以在軟件芯片中編程,并且當(dāng)該軟件下載到FPGA,代碼變成可根據(jù)需要重新編程的實(shí)際硬件。由于FPGA實(shí)際是并行設(shè)備,使用FPGA進(jìn)行圖像處理特別有利。可將算法分割運(yùn)行數(shù)千種不同的通路,并能保持完全獨(dú)立。雖然FPGA本身是非常適合許多視覺應(yīng)用程序的,但系統(tǒng)中還存在很多因素不適合在FPGA上運(yùn)行。評(píng)估是否要使用FPGA進(jìn)行圖像處理需要考慮多項(xiàng)因素。

“ FPGA處在處理圖像時(shí)具有令人難以置信的低延時(shí)(微秒數(shù)量級(jí))...當(dāng)使用具有高速相機(jī)總線的FPGA,如不緩沖的圖像數(shù)據(jù)的Camera Link,只要第一個(gè)像素自相機(jī)中發(fā)出,F(xiàn)PGA就可以處理圖像,而不要等到整個(gè)圖象讀出已經(jīng)完成后再處理。”

“ FPGA可以幫助避免抖動(dòng)。因?yàn)?FPGA不會(huì)因?yàn)槠渌€程、操作系統(tǒng)或中斷產(chǎn)生額外的開銷, FPGA具有很好的確定性。對(duì)于許多圖像處理算法來說,F(xiàn)PGA能夠?qū)⑺_定的執(zhí)行時(shí)間精確到納秒。”

Heard的文章延續(xù)了系統(tǒng)級(jí)功耗限制的討論,這樣的討論有利于FPGA在視覺系統(tǒng)中的應(yīng)用。

“一個(gè)FPGA可消耗1-10瓦的功率,而同樣性能的CPU會(huì)輕易消耗50-200瓦。功耗較大,就必須消散大量的熱量。在無風(fēng)扇嵌入式應(yīng)用程序中,這可能會(huì)造成更為復(fù)雜的大型機(jī)械設(shè)計(jì)。所以,在極端條件下如太空,空中和水下應(yīng)用中,低功耗FPGA特別有用。”

Heard的文章列出了機(jī)器視覺的四個(gè)主要應(yīng)用類別:

1、可視化

2、高速控制

3、圖像預(yù)處理

4、協(xié)處理

?“可視化”,從相機(jī)拍攝圖像并進(jìn)行調(diào)整,以增強(qiáng)圖像顯示效果以適應(yīng)人眼觀看。在這種情況下,F(xiàn)PGA從相機(jī)讀取圖像,執(zhí)行某些類型的并行處理,如突出顯示邊緣和關(guān)注功能或掩蔽功能。然后在FPGA直接輸出圖像至監(jiān)視器或?qū)⑵浒l(fā)送到主機(jī)CPU進(jìn)行顯示.....例如,使用醫(yī)療設(shè)備拍攝圖像,提取細(xì)胞圖像顯示在監(jiān)視器上供醫(yī)生檢查。FPGA可用于測(cè)量每個(gè)細(xì)胞的大小和顏色,并突出顯示醫(yī)生關(guān)注的特定細(xì)胞。

? 高速控制應(yīng)用程序,采用已處理圖像控制輸出,以執(zhí)行控制執(zhí)行器等任務(wù)。“在這些應(yīng)用中,捕獲圖像和執(zhí)行操作之間的時(shí)間必須連續(xù)而且短暫,因此應(yīng)優(yōu)先使用具有低延遲和低抖動(dòng)功能的FPGA。FPGA與視覺和I / O緊密集成可啟用高級(jí)應(yīng)用程序,如視覺伺服,視頻數(shù)據(jù)被用于定位直接反饋并控制伺服電機(jī)。”

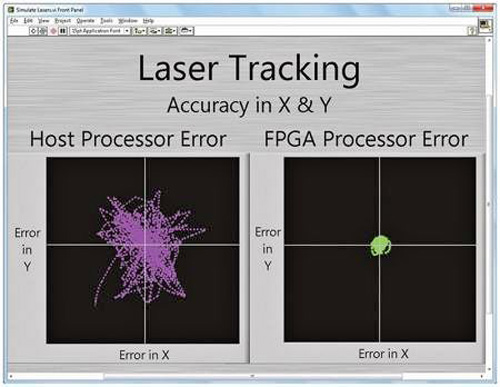

Heard的文章清楚地說明在激光跟蹤中通過使用具有確定性的,低抖動(dòng)的,基于FPGA視覺系統(tǒng)來顯著減少錯(cuò)誤(而不是使用基于CPU系統(tǒng)):

“FPGA非常適用于做空氣成分分選,比如需要執(zhí)行成像、檢驗(yàn)和對(duì)正在下降的空氣進(jìn)行分選等。這類應(yīng)用程序低抖動(dòng)至關(guān)重要,因?yàn)楸仨氁罌Q策和I / O的時(shí)間間隔。”

“圖像預(yù)處理、協(xié)同處理幾乎相同,區(qū)別在于設(shè)備初始捕獲圖像......預(yù)處理圖像時(shí),圖像數(shù)據(jù)遍歷FPGA ,被修改或增強(qiáng),然后FPGA將圖像發(fā)送到主機(jī)以進(jìn)行進(jìn)一步處理和分析。協(xié)處理指圖像數(shù)據(jù)自CPU還不是自相機(jī)發(fā)送到FPGA 。一旦捕獲數(shù)據(jù)需要處理大量圖像時(shí)這種情況是最常見的”

Heard的文章清楚地說明了美國(guó)國(guó)家儀器公司使用LabVIEW FPGA擴(kuò)展了LabVIEW 圖形開發(fā)平臺(tái),可加速?gòu)?fù)雜視覺處理系統(tǒng)開發(fā):

“通常情況下,使用FPGA會(huì)增加設(shè)計(jì)的復(fù)雜度。硬件編程與傳統(tǒng)軟件編程的顯著差異是一條復(fù)雜而不平凡的學(xué)習(xí)曲線。然而,高層次綜合工具如LabVIEW FPGA的可用于將這些復(fù)雜度抽象化,設(shè)計(jì)師能夠充分利用FPGA技術(shù),不需要對(duì)VHDL編程有深入的了解。”

如果設(shè)計(jì)團(tuán)隊(duì)更熟悉其他類型的開發(fā)工具也可以采取其他方法。例如,如果開發(fā)團(tuán)隊(duì)非常熟悉采用高級(jí)編程語(yǔ)言的C和C + +、Xilinx Vivado HLS (高層次綜合)編碼視覺系統(tǒng)可在 Xilinx 7 系列 All Programmable 器件 和 Zynq All Programmable SoC利用這些語(yǔ)言編譯將這些算法編寫成硬件描述。

許多視覺系統(tǒng)開發(fā)團(tuán)隊(duì)所熟悉的其他種類的視覺專用開發(fā)工具,如MVTec的綜合開發(fā)軟件HALCON 和Silicon Software Visual Applets圖形設(shè)計(jì)工具。這些工具也可以針對(duì)Xilinx All Programmable器件,使用低功耗可編程硬件提高視覺性能,而無需學(xué)習(xí)新的設(shè)計(jì)風(fēng)格。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21989瀏覽量

615222 -

cpu

+關(guān)注

關(guān)注

68文章

11053瀏覽量

216255 -

機(jī)器視覺

+關(guān)注

關(guān)注

163文章

4519瀏覽量

122452

發(fā)布評(píng)論請(qǐng)先 登錄

基于FPGA的機(jī)器視覺設(shè)計(jì)

機(jī)器視覺算法與應(yīng)用(雙語(yǔ)版)

機(jī)器人視覺系統(tǒng)組成及定位算法分析

照明對(duì)機(jī)器視覺應(yīng)用有什么影響?

機(jī)器視覺系統(tǒng)應(yīng)用于標(biāo)簽外觀視覺檢查!

深圳機(jī)器視覺led光源有什么優(yōu)勢(shì)

CPU和FPGA的機(jī)器視覺算法分割

基于交叉視覺皮質(zhì)模型的圖像快速分割新算法

基于改進(jìn)的SLIC像素分割算法

視覺顯著性目標(biāo)分割提取

機(jī)器視覺應(yīng)用,CPU還是FPGA?資料下載

什么叫機(jī)器視覺?機(jī)器視覺和嵌入式有什么關(guān)系?

CPU和FPGA的機(jī)器視覺算法分割

CPU和FPGA的機(jī)器視覺算法分割

評(píng)論