賽靈思All Programmable 器件低端產(chǎn)品組合中包括三大器件系列,因?yàn)榇罅?a target="_blank">DSP硬件處理模塊都集成進(jìn)了這三大系列的可編程邏輯架構(gòu)中,它們都給DSP設(shè)計(jì)師提供了有趣的選擇。這些DSP處理模塊---賽靈思官方稱謂是slices,都已經(jīng)集成進(jìn)乘法器和累加器中,并且已經(jīng)針對最常用(以及不常用)的DSP進(jìn)行了優(yōu)化。

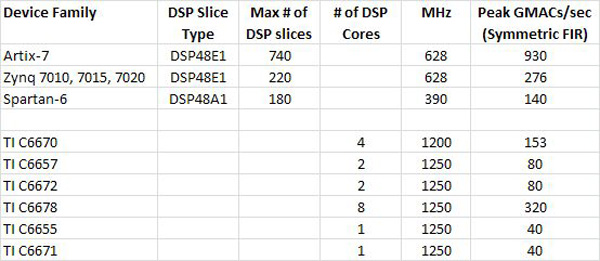

下表顯示了在每個(gè)賽靈思低端產(chǎn)品系列(Zynq、Artix-7和Spartan-6)中,可以使用的DSP Slices最大數(shù)量,以及你可以從這些器件獲得GMAC/s(每秒億次乘法累積操作)峰值。為便于比較,表中還顯示了你可以從TI的C66xx多核DSP系列得到的每秒GMAC峰值。

正如你所看到的,賽靈思低端All Programmable器件在較低時(shí)鐘頻率下比傳統(tǒng)DSP提供明顯更多GMAC/s性能,原因很簡單:并行性!在這些低端器件中有大量乘法器和累加器,DSP就是一種GMAC游戲。 (當(dāng)然,高端的Zynq SoC和賽靈思的Kintex-7、Virtex-7、Kintex UltraScale和Virtex UltraScale All Programmable系列器件則可以提供更高DSP性能。)

除了提供基礎(chǔ)的GMAC性能,把這些高性價(jià)比低端All Programmable器件用于DSP應(yīng)用的另外一個(gè)優(yōu)勢是實(shí)際的能效優(yōu)勢(性能/瓦)例如,TI的TMC320C6678多核DSP功耗大約是12.3W,并提供320 GMAC/s的性能,歸一化后就是26 GMAC/s/ W。

而Artix-7 All Programmable器件可以提供140 GMAC/s/W,這可是TI器件的五倍多!

現(xiàn)在,你可能在想,用類似這樣低端All Programmable器件的硬件芯片去實(shí)現(xiàn)DSP算法會不會太難了?基于硬件可編程器件的DSP設(shè)計(jì)會不會不適合你現(xiàn)有的設(shè)計(jì)流程?其實(shí)并不是那樣的,例如,如果您正在用MATLAB或Simulink開發(fā)基于模型的DSP算法,您就已經(jīng)涉及了賽靈思的System Generator和Mathworks的HDL編碼器。如果您目前在用C或C + +寫DSP算法,那用賽靈思的Vivado HLS工具也可以干這事。

-

dsp

+關(guān)注

關(guān)注

555文章

8121瀏覽量

354088 -

ti

+關(guān)注

關(guān)注

113文章

8014瀏覽量

214035 -

賽靈思

+關(guān)注

關(guān)注

33文章

1795瀏覽量

132010

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)之浮點(diǎn)DSP算法實(shí)現(xiàn)【賽靈思工程師作品】

選擇賽靈思(Xilinx)FPGA 7系列芯片的N個(gè)理由

賽靈思Zynq-7000可擴(kuò)展處理平臺讓編程流程更簡單

如何利用賽靈思28納米工藝加速平臺開發(fā)?

賽靈思28nm系列的里程碑–首批Artix-7 FPGA出貨

深入剖析賽靈思(Xilinx)All Programmable三大創(chuàng)新器件

賽靈思器件低端產(chǎn)品組合中三大器件系列給DSP設(shè)計(jì)師提供了選擇

賽靈思器件低端產(chǎn)品組合中三大器件系列給DSP設(shè)計(jì)師提供了選擇

評論