1。接線寬度和電流

一般寬度不應小于0.2mm(8mil)

高密度,高精度PCB,間距和線寬通常為0.3mm(12mil)。

當銅箔厚度約為50um時,線寬為1~1.5 mm(60mil)= 2A

公共場所一般為80mil,這對于使用微處理器的應用來說更為重要。

2。高速電路板有多高?

當信號的上升/下降沿時間是信號傳輸時間的<3~6倍時,它被認為是一種高速信號。

對于數字電路,關鍵是要觀察信號邊緣的陡度,即上升和下降時間信號。

根據一本非常經典的書“高速數字設計”的理論,信號從10%上升到90%不到6倍于線延遲,這是一個高速信號!------即使是8KHz的方波信號,只要邊緣足夠陡峭,就是高速信號,而傳輸線理論接線需要。

3。 PCB堆疊和分層

為了獲得更好的電磁兼容性設計,多層印刷電路板在正常運行期間可以滿足電磁兼容性和靈敏度標準。適當的堆疊有助于屏蔽和抑制EMI。在多層印刷電路板的分層和堆疊中通常遵循以下基本原則:

( 1 ) 電源層應盡可能靠近地平面,并應低于地平面。

( 2 ) 布線層應鄰近布置圖像平面層。

( 3 ) 功率和地層阻抗最低。

( 4 ) 在中間層形成一條帶狀線,并且在表面上形成微帶線。這兩者的特征是不同的。

( 5 ) 重要的信號線應該接近地面。

多重的一個非常重要的優勢普通雙層板和單層板上的層板是信號線和電源可以分布在不同的板層上,以提高信號隔離和抗干擾性能。然而,許多工程師仍然對PCB的分層和堆疊感到頭疼,以常用的4層板為例。

四層板具有以下堆疊順序。以下說明各種堆棧的優缺點:

注:S1信號布線層,S2信號布線層2; GND接地層POWER電源層

在第一種情況下,它應該是四層電路板的最佳情況。由于外層是接地層,它對EMI有屏蔽作用,電源層靠近接地層也很可靠,因此電源的內阻很小,可以得到最好的郊區水果。但是,當電路板的密度相對較大時,不能使用第一種情況。因此,不能保證第一層的完整性,并且第二層信號將變得更糟。此外,這種結構不能用于整板功耗相對較大的情況。

第二種情況是我們通常使用的最常見的方式。從電路板的結構來看,它不適合高速數字電路設計。因為在這種配置中,難以保持低電源阻抗。以2 mm的板為例:Z0 = 50歐姆是必需的。線寬為8密耳。銅箔的厚度為35μm。因此,地面和地面之間的信號層中間為0.14mm。形成和功率層為1.58mm。這極大地增加了電源的內阻。在這種結構中,由于輻射是空間的,因此需要增加屏蔽板以降低EMI。

在第三種情況下,S1層的信號線質量最佳。 S2排名第二。它對EMI有屏蔽作用。但是,電源阻抗很大。當整個電路板的功耗很大且電路板是干擾源或接近干擾源時,可以使用該電路板。

4。阻抗匹配

反射電壓信號的幅度由源反射系數ρs和負載反射系數ρL決定。

ρ L =(RL - Z0)/(RL + Z0)和ρS=(RS - Z0)/(RS + Z0)

在上面的公式中,如果RL = Z0,負載反射系數ρL= 0.如果RS = Z0源反射系數ρS= 0。

由于普通傳輸線阻抗Z0通常應滿足約50Ω的50Ω要求,因此負載阻抗通常在幾千歐姆到幾十千歐姆的范圍內。因此,難以在負載側實現阻抗匹配。但是,由于信號源(輸出)阻抗通常較小,因此大約為十幾歐姆。因此,在源處實現阻抗匹配要容易得多。如果電阻器與負載并聯連接,電阻器將吸收一些信號,這將不利于傳輸(我明白)。選擇TTL/CMOS標準24mA驅動電流時,輸出阻抗約為13Ω。如果傳輸線阻抗Z0 =50Ω,則應添加33Ω源端接電阻。 13Ω+33Ω=46Ω(約50Ω,弱欠阻尼有助于信號建立時間)

當選擇其他傳輸標準和驅動電流時,匹配阻抗會有所不同。在高速邏輯和電路設計中,對于某些關鍵信號,如時鐘,控制信號等,我們建議添加源側匹配電阻。

這樣,信號也從負載端反射回來。由于源阻抗匹配,反射信號不會被反射回來。

5 。電源線和接地線布局注意事項

電源線盡可能短,筆直,最好是樹形,不要走環

接地回路問題:對于數字電路,接地回路引起的接地回路為幾十毫伏,而TTL抗干擾門限為1.2V,CMOS電路可達到1/2電源電壓。也就是說,接地回路循環不會對電路的運行產生不利影響。相反,如果地線未閉合,則問題會更大,因為數字電路產生的脈沖電源電流將導致每個點的地電位不平衡。例如,當逆變器為1.2A時,我反向測量74LS161的接地電流。 2Gsps示波器測量的地電流脈沖寬度為7ns)。在大脈沖電流的影響下,如果使用分布式地線(線寬25密耳),地線之間每個點的電位差將達到100毫伏的水平。在使用接地回路之后,脈沖電流擴展到地線的各個點,這大大降低了干擾電路的可能性。對于閉合的地線,每個設備的地面的最大瞬時電位差被測量為未閉合地面的一半到五分之一。當然,具有不同密度和不同速度的電路板的測量數據是非常不同的。我上面說過,它指的是附著在protel 99SE上的Z80演示板的水平。對于低頻模擬電路,我認為接地線閉合后的電源頻率。從空間感測干擾,無論如何都不會模擬或計算干擾。如果地線未閉合,則不會發生接地渦流。 Beckhamtao說,“但地線是開路的,工頻感應電壓會更大。”理論基礎和兩個例子,我在7年前接管了其中一個。該項目的精密壓力表采用14位A/D轉換器,但實際測量只有11個有效精度。經過調查,地面有15mVp-p的工頻干擾。解決方案是模擬PCB的接地回路。刮擦,A/D地線的前端傳感器由飛線分布。后來,大規模生產的模型PCB根據飛行線重新生產,到目前為止沒有問題。第二個例子,朋友喜歡發燒,DIY一個功放,但輸出總是有嗡嗡聲,我建議它切斷地面循環,問題解決了。之后,這名男子回顧了數十個“Hi-Fi機器”PCB圖,確認沒有機器在模擬部件中使用接地回路。

6。印刷電路板設計原則和抗干擾措施

印刷電路板(PCB)是對電子產品中電路元件和器件的支持。它提供電路組件和設備之間的電氣連接。隨著電力技術的快速發展,PGB的密度越來越高。 PCB設計的質量對干擾能力有很大影響。因此,在PCB設計中,必須遵守PCB設計的一般原則,并且應滿足抗干擾設計的要求。

7 。接線

接線原理如下:

(1)使用的電線應盡可能避免輸入和輸出端子。最好在導線之間添加接地線以避免反饋。

(2)印刷光導線的最小寬度主要由通過導線和絕緣基板之間的粘合強度和流過它們的電流值。當銅箔的厚度為0.05mm,寬度為1~15mm時,通過2A的電流,電流不會超過3℃。因此,1.5mm的線寬可以滿足要求。對于集成電路,尤其是數字電路,通常選擇0.02至0.3mm的線寬。當然,只要允許,盡可能使用寬線,尤其是電源線和地線。導線的最小間距主要由最壞情況的線間絕緣電阻和擊穿電壓決定。對于集成電路,尤其是數字電路,只要工藝允許,間距可以小到5到8 mm。

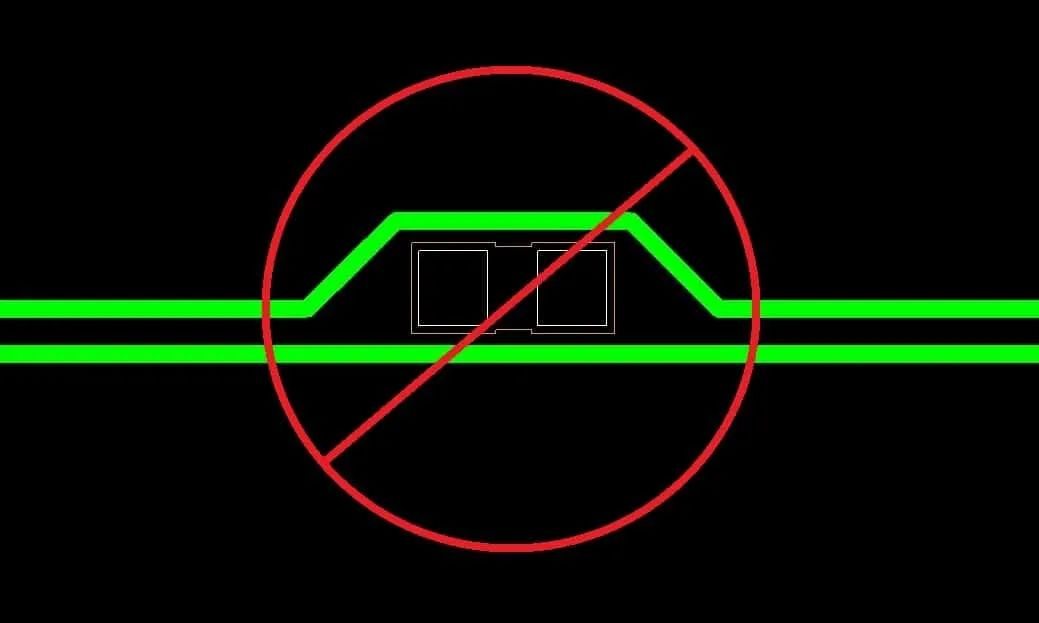

(3)印刷導體的彎曲角通常呈圓弧形,直角或角度影響高頻電路中的電性能。另外,盡量避免使用大面積的銅箔,否則很容易導致銅箔在長時間加熱時膨脹和脫落。當使用大面積的銅箔時,優選使用網格形狀。這有利于消除銅箔和基板之間粘合劑熱量產生的揮發性氣體。

8。焊盤

焊盤的中心孔略大于器件引線的直徑。焊盤太大而不能形成焊點。墊外徑D通常不小于(d + 1.2)mm,其中d是引導孔。對于高密度數字電路,最小焊盤直徑可以是(d + 1.0)mm。

PCB和電路抗干擾措施

印刷電路板的抗干擾設計與具體電路密切相關。這里僅解釋了PCB抗干擾設計的一些常用測量方法。

9。解除電容器配置

PCB設計的一個常見做法是在印刷電路板的各個關鍵點配置適當的去耦電容。

解捻電容器的一般配置原則是:

( 1)電源輸入端子連接到10~100 uf的電解電容器。如果可能的話,最好選擇100uF或更多。

(2)原則上,每個集成電路芯片應配備一個0.01pF的陶瓷電容器。如果印刷電路板上沒有足夠的空間,則每4~8個芯片可以安排1~10pF的電容。

(3)對于抗噪聲較弱的設備在關機期間能力和大電源變化,如RAM和ROM存儲設備,去耦電容應直接連接在電源線和芯片的地之間。

( 4)電容器引線不應太長,特別是高頻旁路電容器不得有引線。

此外,還應注意以下兩點:

(1)當印刷電路板上有觸點,繼電器,按鈕和其他元件時,操作時會發生大火花放電,并且RC電路如圖所示必須使用圖紙來吸收放電電流。一般情況下,R需要1~2K,C需要2.2~47UF。

(2)CMOS的輸入阻抗很高,易受感應。因此,在使用過程中必須將電源接地或連接到未使用的端子。

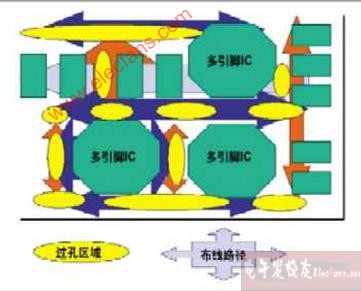

10。高效PCB自動布線的設計技巧和關鍵點

盡管當前的EDA工具非常強大,但隨著PCB尺寸要求變小和器件密度的增加越來越高,PCB設計并不困難。如何實現高PCB布局并縮短設計時間?本文介紹了PCB規劃,布局和布線的設計技巧和要點。如今PCB設計越來越短,越來越小的電路板空間,更高的器件密度,極其苛刻的布局規則和大尺寸元件使設計人員的工作更加困難。為了解決設計難題并加快市場推出,許多制造商現在更喜歡使用專用的EDA工具來實現PCB設計。

-

PCB布線

+關注

關注

21文章

469瀏覽量

42537 -

PCB打樣

+關注

關注

17文章

2974瀏覽量

22379 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28456 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43763

發布評論請先 登錄

[分享]實現PCB高效自動布線的設計技巧和要點

實現PCB高效自動布線的設計技巧和要點

實現PCB高效自動布線的設計技巧和要點

怎么實現PCB高效自動布線,這篇文章告訴你

如何實現PCB高效自動布線資料下載

高效PCB自動布線的設計技巧和關鍵點

高效PCB自動布線的設計技巧和關鍵點

評論