賽靈思與采埃孚展開合作,加速促成無人駕駛應(yīng)用落地

ZF ProAI 的獨特賣點是其模塊化的硬件概念和開放式的軟件架構(gòu)。我們的目標(biāo)是為無人駕駛領(lǐng)域提供最....

CES與賽靈思達(dá)成技術(shù)合作共同滿足自動駕駛技術(shù)需求

事實證明,MINIEYE在基于賽靈思技術(shù)為汽車制造提供高精度深度神經(jīng)網(wǎng)絡(luò)方面擁有出色的能力。通過與M....

戴姆勒透露合作開發(fā)使用賽靈思技術(shù)的車載系統(tǒng)

在交流期間,戴姆勒首次透露了與賽靈思技術(shù)合作的更多細(xì)節(jié),兩家公司正在合作開發(fā)使用賽靈思技術(shù)的車載系統(tǒng)....

賽靈思創(chuàng)新產(chǎn)品三大更新

最后,他們還簡要介紹了近期發(fā)布的 RF 數(shù)據(jù)轉(zhuǎn)換器評估工具。該工具與 ZCU111 評估套件共同運行....

回顧賽靈思五大產(chǎn)品新聞

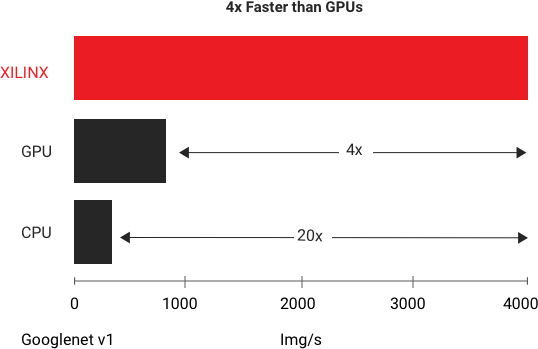

Alveo加速器卡使開發(fā)人員能夠調(diào)整和優(yōu)化他們的算法,以改變加速工作負(fù)載,所有這些都使用相同的硬件。....

賽靈思開發(fā)的FPGA開發(fā)平臺介紹

我們決定創(chuàng)建一個 Word Color Match (單詞顏色配對) 游戲。液晶顯示器有一個RGB可....

賽靈思大中華區(qū)銷售副總裁唐曉蕾在高峰論壇發(fā)表主題演講

通過部署在ZCU102 B4096DPU Dual-core同時實現(xiàn)4中不同的應(yīng)用場景。該方案主要....

賽靈思MPSoC開發(fā)教程詳解

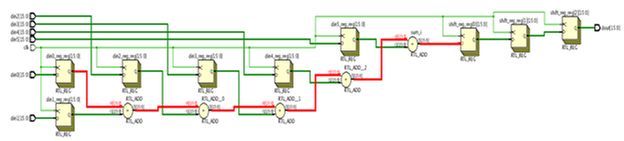

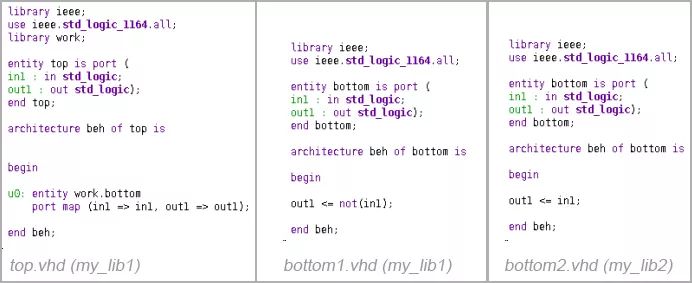

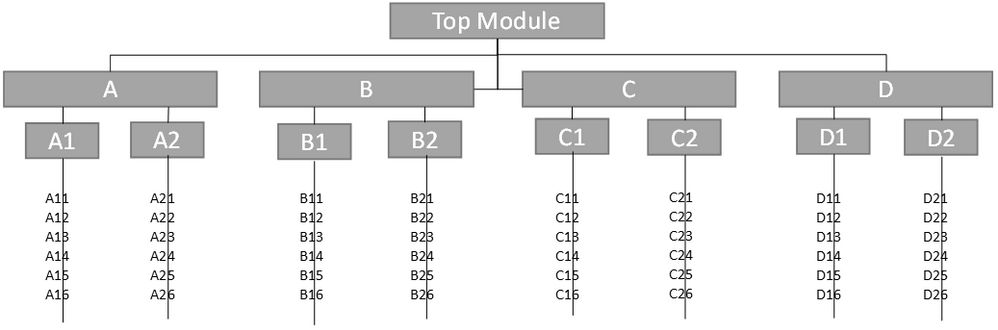

SoC系統(tǒng)將包括硬件設(shè)計和軟件設(shè)計兩個方面。硬件設(shè)計會映射到SoC設(shè)備上的FPGA邏輯資源,而軟件則....

賽靈思帶來了“FPGA — 人工智能計算的加速引擎”的主題演講

這些市場包括八大市場領(lǐng)域:汽車、無線基礎(chǔ)設(shè)施、有線通信、音頻、視頻與廣播、航空航天、工業(yè)、科學(xué)與醫(yī)療....

賽靈思布展第七屆中國國際技術(shù)進(jìn)出口交易會

賽靈思為 ADAS 及自動駕駛系統(tǒng)提供基于深度學(xué)習(xí)處理器的車載感知處理平臺DP-2400。該平臺以F....

第七屆中國電子信息博覽會賽靈思榮獲雙冠軍

相比市場其他的解決方案,擁有15年行業(yè)標(biāo)準(zhǔn)認(rèn)證,并基于賽靈思獨特靈活性和高度集成優(yōu)勢的賽靈思汽車電子....

賽靈思參加百度云智峰會,展示四大加速方案

Xilinx 機(jī)器學(xué)習(xí)(ML)套件運行于賽靈思 Alveo 數(shù)據(jù)中心加速卡上,為用戶提供了開發(fā)和部署....

GCC和CCIX 聯(lián)盟簽訂備忘錄,支持CCIX作為互聯(lián)技術(shù)工業(yè)標(biāo)準(zhǔn)

基于這份合作備忘錄,CCIX 和GCC 共同將CCIX 作為GCC 綠色計算標(biāo)準(zhǔn)體系的支柱技術(shù)之一,....

賽靈思助力華為在服務(wù)器領(lǐng)域?qū)崿F(xiàn)重大突破

華為認(rèn)為,以“信息技術(shù)”為特征的第四次工業(yè)革命,將世界帶入了數(shù)字化時代;以“智能技術(shù)”為特征的第四次....

浪潮與賽靈思合作將進(jìn)一步滿足全球AI用戶日益增長的計算力需求

FPGA 技術(shù)因可定制性、低延遲和高性能功耗比的特點受到越來越多 AI 用戶的青睞。Alveo U2....

賽靈思對于智能汽車的概念解析

隨著大數(shù)據(jù)以及人工智能的發(fā)展,以及車載4G通信系統(tǒng)的進(jìn)一步普及,可以預(yù)想今年發(fā)布的新車會越來越多的搭....

賽靈思助力現(xiàn)代化醫(yī)療方案加速工業(yè)4.0發(fā)展

在醫(yī)療領(lǐng)域,賽靈思產(chǎn)品因其靈活性與大數(shù)據(jù)處理的優(yōu)勢在諸如基因測序,以及圖形圖像處理方面得到了廣泛的應(yīng)....

賽靈思擔(dān)任計算技術(shù)人才培養(yǎng)工作委員會工委秘書長單位

在找到“新摩爾定律”之前,架構(gòu)的創(chuàng)新需要擔(dān)負(fù)起更為重要的角色。因此可定制計算走向了前臺。賽靈思公司靈....

賽靈思在技術(shù)日演示方案惠及從云到端的各類應(yīng)用

通過部署在ZCU102 B4096DPU Dual-core 同時實現(xiàn)4種不同的應(yīng)用場景。分別是:人....

世界通信大會賽靈思展出八大創(chuàng)新方案

對于 5G 而言,賽靈思的技術(shù)正在幫助解決容量、連接以及性能挑戰(zhàn)。并靈活支持多標(biāo)準(zhǔn)、多頻帶和多子網(wǎng)絡(luò)....

賽靈思十大智能之工業(yè)互聯(lián)智能運動控制器方案

支持速度前瞻、電子凸輪、電子齒輪、螺距補償、同步跟蹤、運動疊加、虛擬軸、脈沖閉環(huán)、硬件位置鎖存、位置....

賽靈思十大智能之智能駕駛方案

針對智能駕駛,安富利與合作伙伴一起展示了基于賽靈思平臺的高級駕駛輔助系統(tǒng),包括了ADAS融合、駕駛員....

數(shù)字峰會上賽靈思的十大智能演示

MYMINIEYE(深圳市我是你的眼科技有限公司)成立于2015年,其產(chǎn)品涵蓋:無人機(jī),無人船,航模....

賽靈思參加第二屆數(shù)字中國建設(shè)峰會,展現(xiàn)全面賦能數(shù)字創(chuàng)新事業(yè)

在數(shù)字世界的發(fā)展進(jìn)程中,以信息化、數(shù)字化為代表的新興科技發(fā)展已成為引領(lǐng)創(chuàng)新、驅(qū)動轉(zhuǎn)型、打造競爭優(yōu)勢的....

賽靈思發(fā)布智能解決方案,滿足醫(yī)療保健平臺的需求

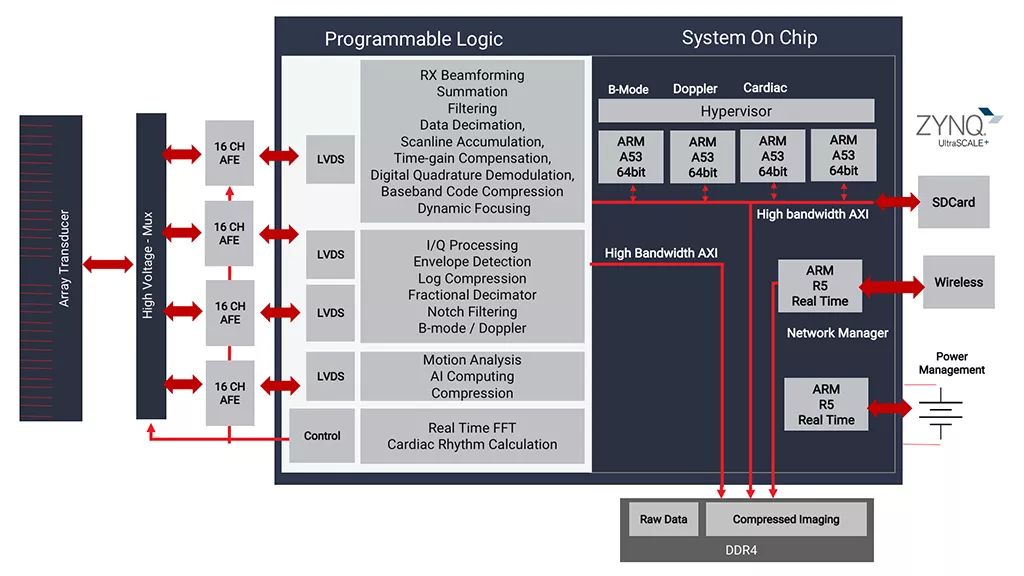

賽靈思 ZYNQ-Ultrascale+ 片上系統(tǒng) (SoC) 技術(shù)可為并行波束形成等復(fù)雜架構(gòu)實現(xiàn)超....

Vivado崩潰調(diào)試的方案和預(yù)防

在某些情況下會出現(xiàn)日志不足的狀況,并且需要與賽靈思共享 RTL 設(shè)計,才能對問題進(jìn)行進(jìn)一步調(diào)試。

云計算成為新興市場,為全球提供服務(wù)

許多這些業(yè)經(jīng)驗證的 IP 核都可進(jìn)行配置,因而可針對特定應(yīng)用性能需求進(jìn)行量身定制。賽靈思提供各種專業(yè)....