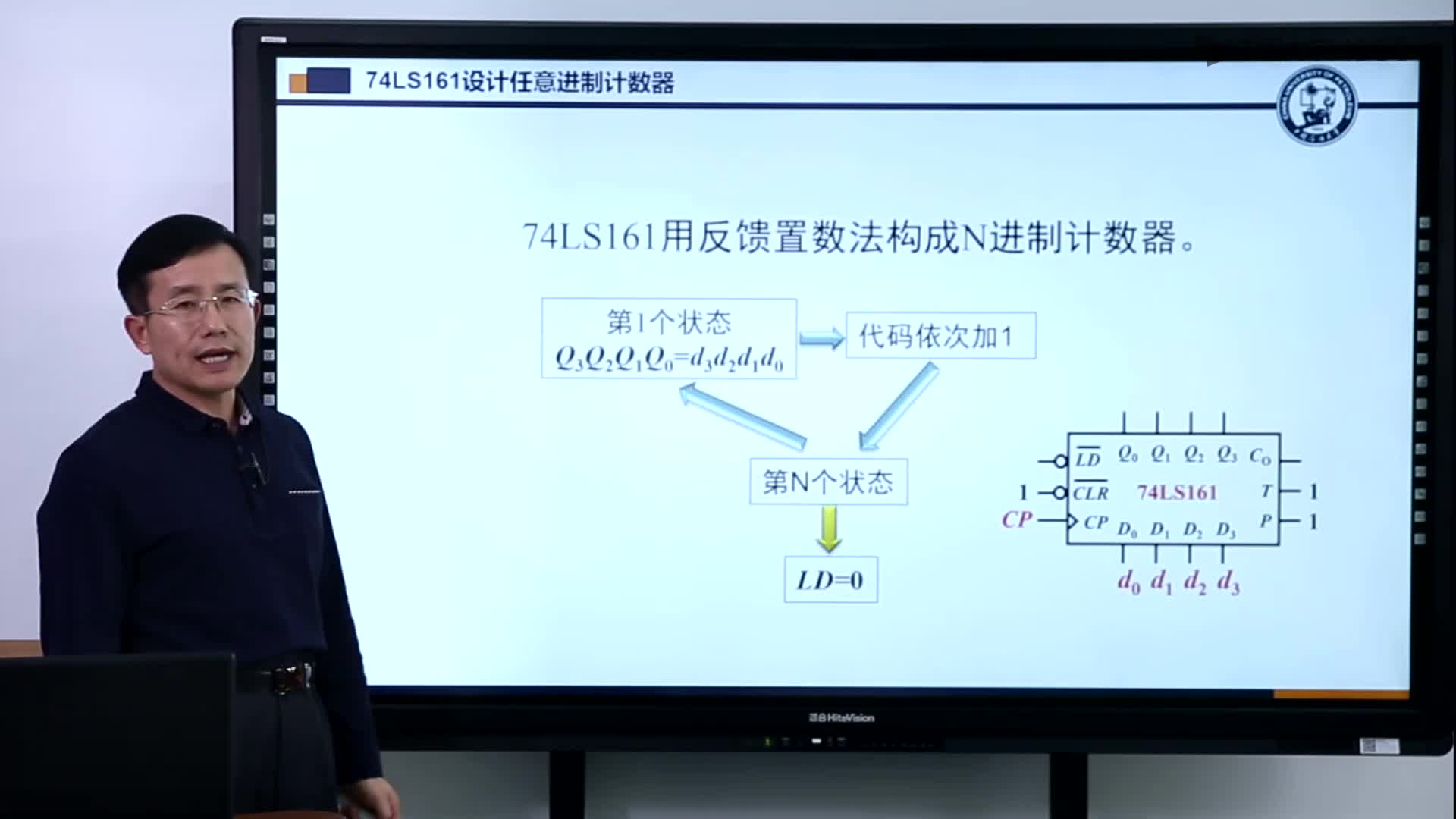

本文為大家介紹基于74LS192的任意進制計數器的設計。

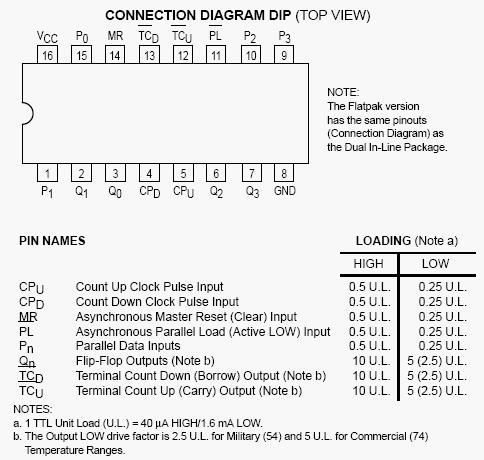

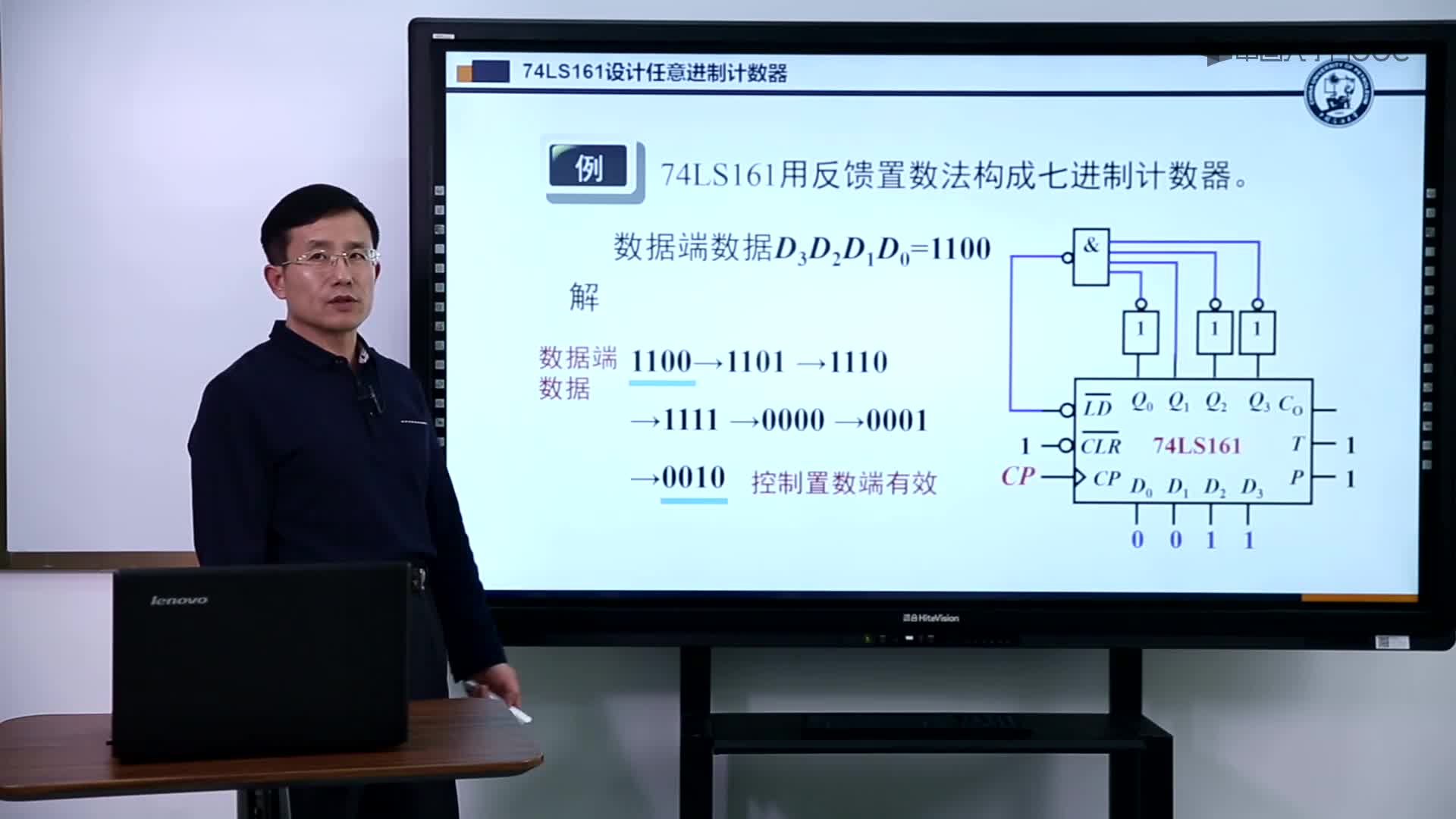

74LS192的管腳圖

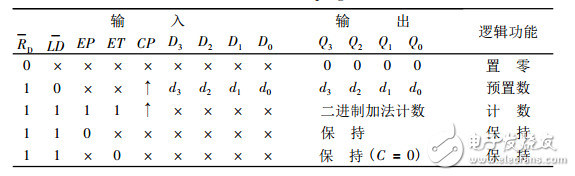

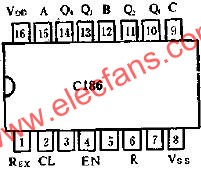

74LS192是同步十進制可逆計數器,它由四個主從 T觸發器和一些門電路組成。具有雙時鐘輸入、清零、保持、并行置數、加計數、減計數等功能。圖1為74LS192的管腳圖。

圖1 74LS192的管腳圖

圖1中:CLR是清零端,高電平有效;UP是遞加計數脈沖輸入端;DOWN是遞減計數脈沖輸入端;~LOAD是置數控制端,低電平有效;~CO是進位輸出端;~BO是借位輸出端。ABCD是置數端口。

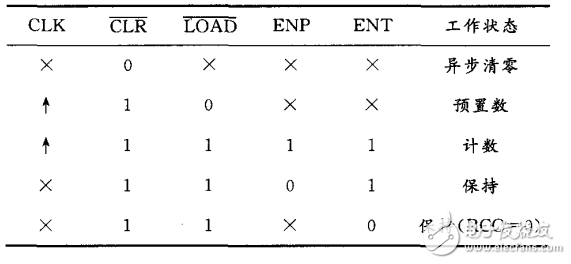

任意進制計數器M小于N的情況

假定已有的是N進制計數器,需要得到的是M進制計數器。這時就有M小于N和M大于N兩種情況。

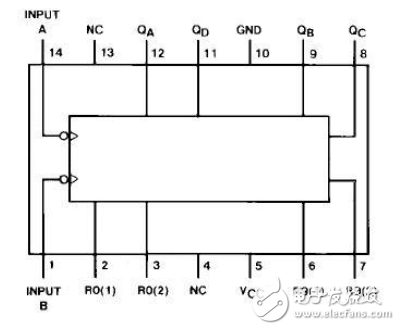

例題為用74LS192設計一個八進制計數器:

在N進制的計數器的計數順序中,使計數器的計數狀態跳過N-M的狀態,就可以得到M進制計數器,如例,74LS192是一個十進制計數器,如想得到八進制計數器,輸出狀態QAQBQCQD需要從0000―1110狀態,跳過0001及1001這兩個狀態。實現跳躍的方法有置零法和置數法這兩個方法。

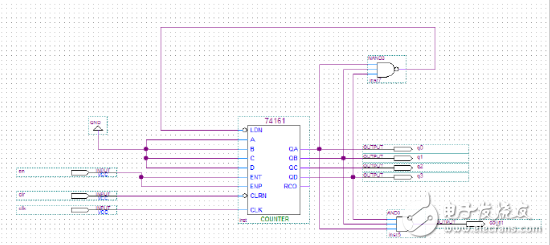

置零法的方式為在輸入第M個計數脈沖CP后,利用計數器當前的輸出狀態SM進行譯碼產生清零信號加到清零端上,使計數器清零,即實現了M進制計數器。在計數器的有效循環中不包括狀態SM,所以狀態SM只在極短的時間內出現稱為過渡狀態。對于本例題來說,在輸入第八個時鐘脈沖后,當前的輸出狀態QAQBQCQD為0001,通過計數器輸出端QD的高電平信號給CLR清零端,將計數器置零,回到0000狀態。根據以上原理設計出的邏輯圖如圖2所示。

圖2

置數法方式為通過給計數器置入某個數值的方法跳躍N-M的狀態,從而獲得M進制計數器,這種方法適用于有預置數功能的集成計數器。對于本例題來說,QAQBQCQD=0001狀態與非門譯碼產生~LOAD=0的低電平信號,下一個時鐘脈沖信號到來時將置數端ABCD=0000狀態置入,跳過0001及1001這兩個狀態因而就實現了八進制。設計出的邏輯圖如圖3所示。

圖3

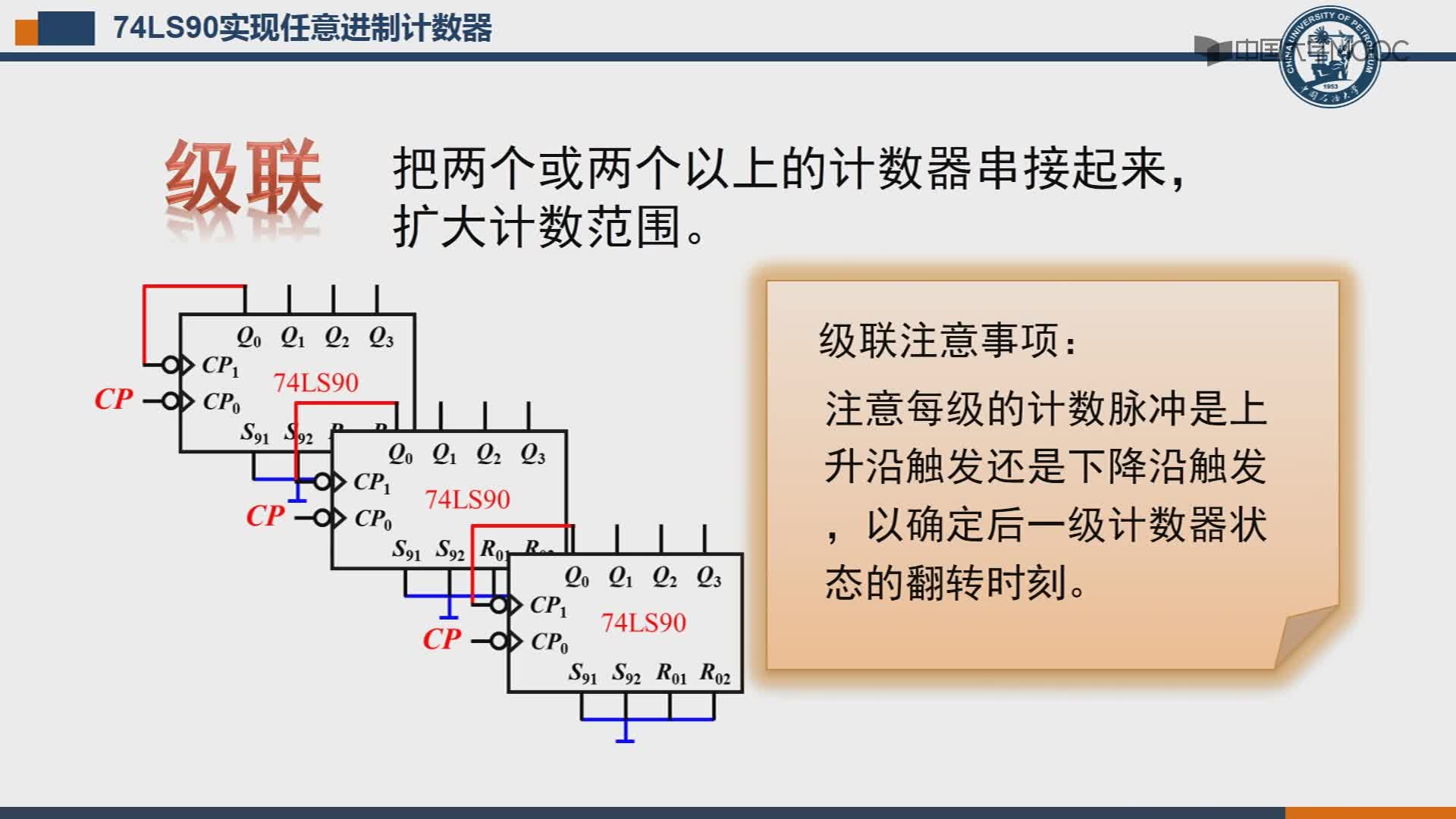

任意進制計數器M大于N的情況

例題為用74LS192設計一個24進制的計數器。

設計任意進制計數器M大于N的情況時必須要使用兩個以上的N進制集成電路進行組合來完成M進制計數器的設計,各個集成電路之間的連接方式可分為串行進位,并行進位,整體置零,整體置數等幾種方法。

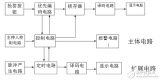

圖4

整體置零法就是將兩片N進制計數器級聯成大于M進制的計數器,然后在計數器輸出到達M狀態時,通過輸出狀態譯碼出清零信號同時送達兩個計數器的清零端,使兩個計數器同時清零,從而實現M進制,此方法類似于M小于N的置零法原理。對于74LS192來說,就是在兩片集成計數器輸出端QAQBQCQD到達0010(第一片低位)0100(第二片高位)狀態時,譯出清零信號同時送到兩個計數器的清零端。根據以上設計原理設計出下面的邏輯電路圖(圖4)。

整體置數法的工作原理等同于M小于N的置數法原理,首先就是將兩片N進制計數器聯成大于M進制的計數器,然后選定所設計的M進制狀態,譯碼出置數端的有效工作信號,使N進制計數器置入置數輸入端規定的信號,跳過剩余的不用的狀態,從而實現M進制。用整體置數法使兩片74LS192完成24進制的設計方法可以參考M小于N的置數法以及以上的設計例題。

電子發燒友App

電子發燒友App

評論