在國外網站看到一個主副電源自動切換的電路,設計非常巧妙。

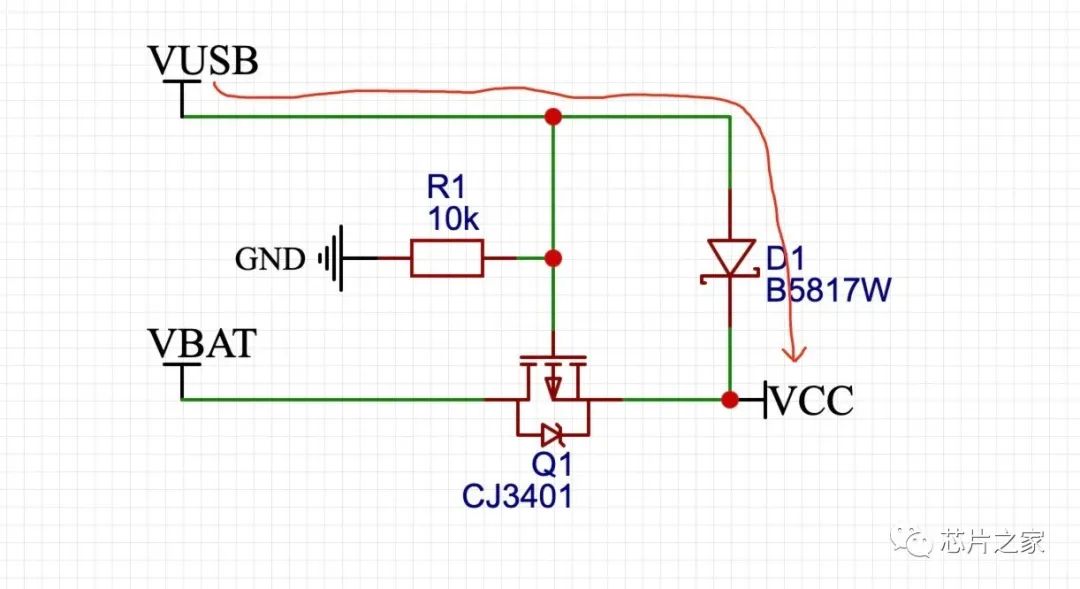

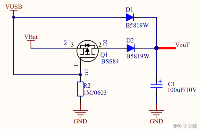

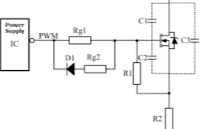

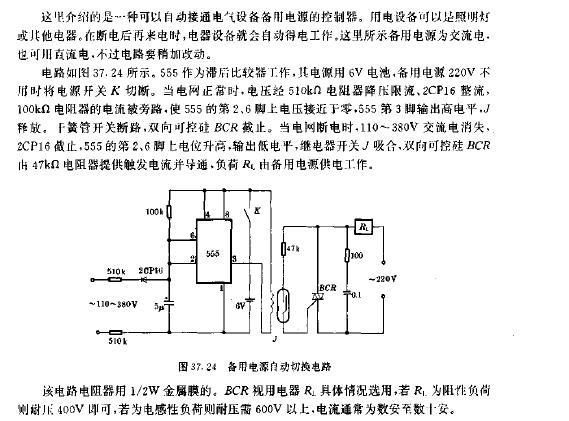

我之前應用的電路:

上面電路設計也挺不錯的,如果VCC端需要的電壓不一定要求等于VUSB,那么這個電路是可以的,那么問題來了,如果主副輸入電壓相等,同時要求輸出也是同樣的電壓,不能有太大的壓降,怎么設計?上面的電路肯定不能滿足了,因為D1的壓降最小也是0.3V。

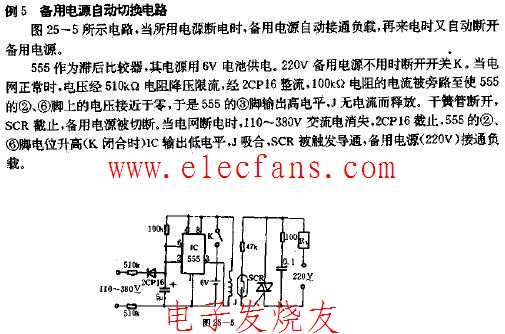

主副電源自動切換電路分析

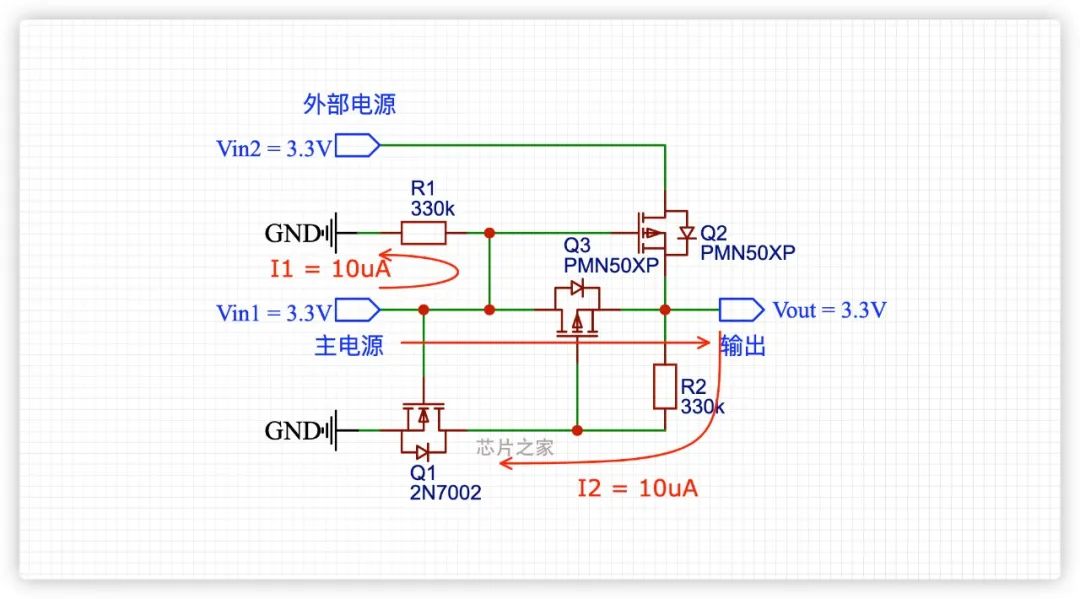

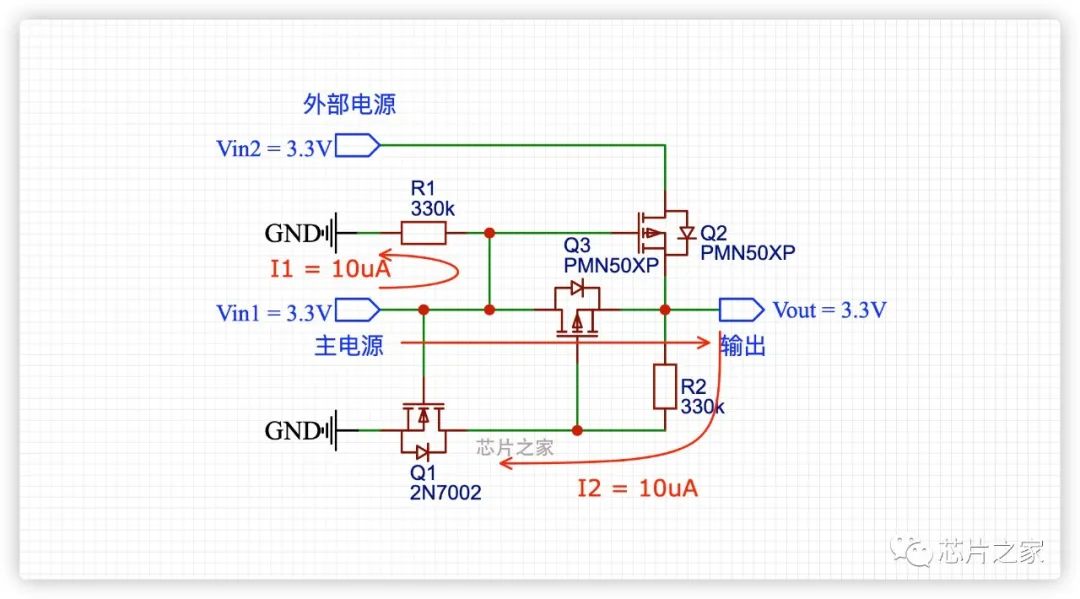

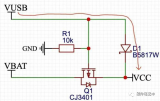

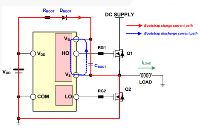

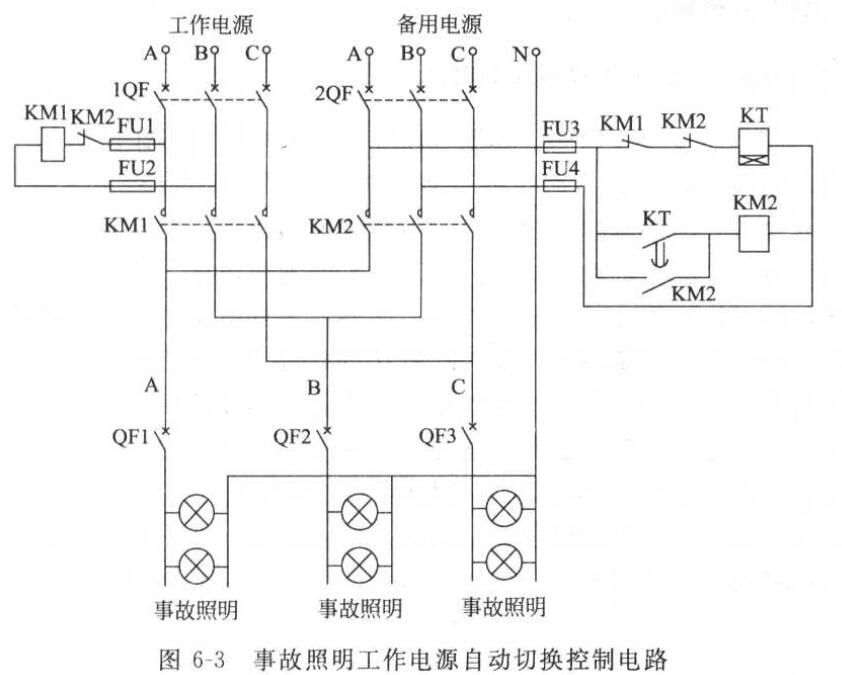

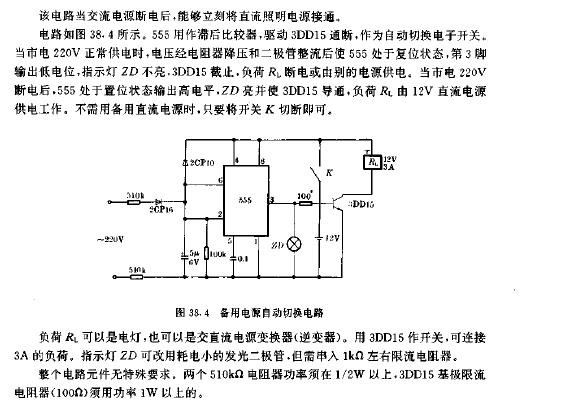

看下面的電路:

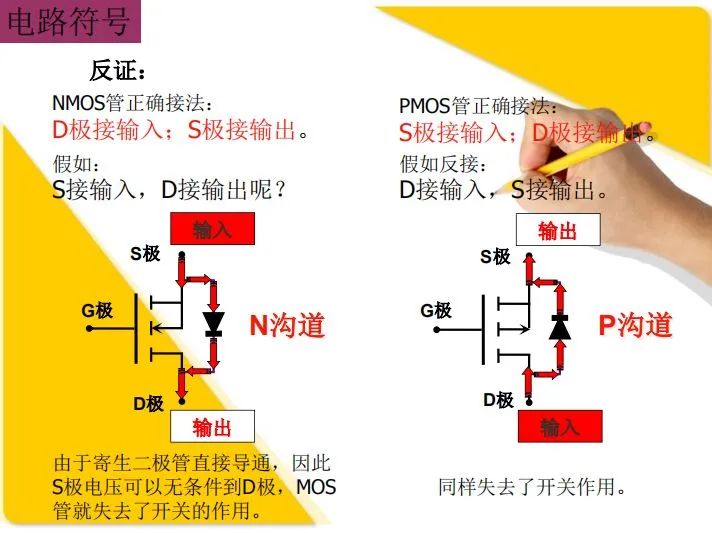

這個電路咋一看復雜很多,其實很簡單,巧妙的利用了MOS管導通的時候低Rds的特性,相比二極管的方式,在成本控制較低的情況下,極大的提高了效率。

本電路實現了:當Vin1=3.3V時,不管Vin2有沒有電壓,都由Vin1通過Q3輸出電壓;當Vin1斷開的時候,由Vin2通過Q2輸出電壓。因為選用MOS管的Rds非常小,產生的壓降差不多為數十mV,所以Vout基本等于Vin。

原理分析:

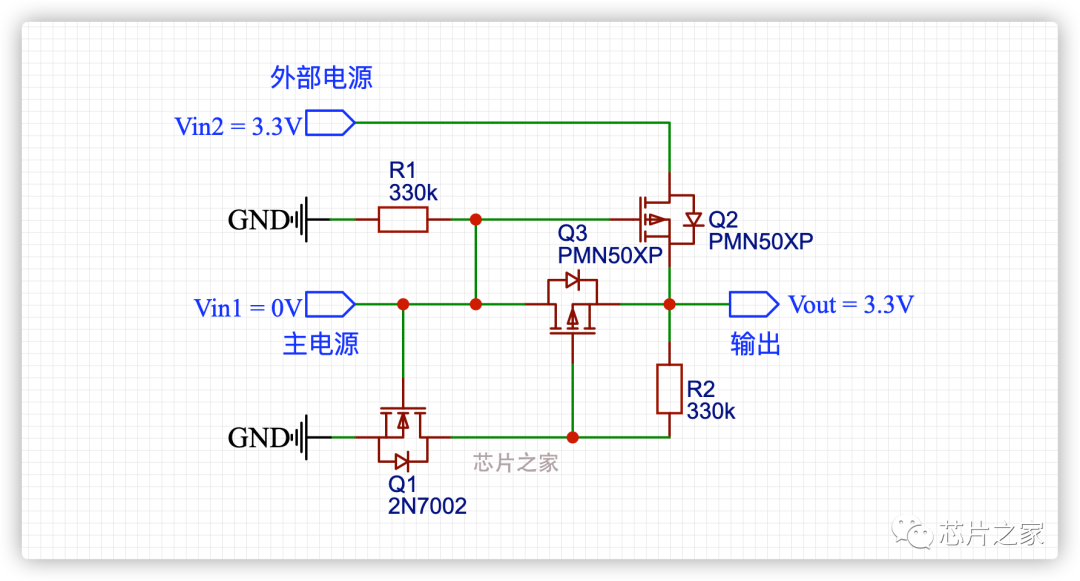

1、如果Vin1=3.3V,NMOS Q1導通,之后拉低了PMOS Q3的柵極,然后Q1也開始導通,此時,PMOS Q2的柵極跟源極之間的電壓為Q3的導通壓降,該電壓差不多為幾十mV,因此Q2關閉,外部電源Vin2斷開,Vout由Vin1供電,Vout=3.3V。此時整個電路的靜態功耗I1+I2=20uA。

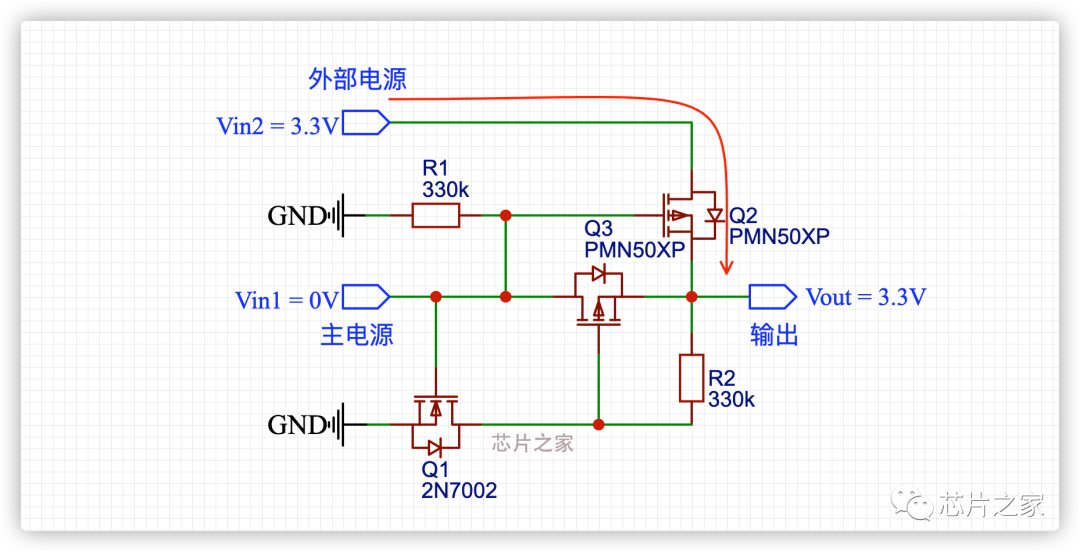

2、Vin1斷開了,Q1截止,Q2的柵極有R1的下拉,所以Q2導通,Q3的柵極通過R2上拉,所以Q3也截止,整個電路,Q1跟Q3截止,Vout由Vin2供電,Vout =3.3V。此時上面電路I1跟I2的靜態功耗不存在。

可見,當存在主電源時,電路的靜態功耗為20uA,否則,幾乎為零。所以電池適合在外部電源供電。

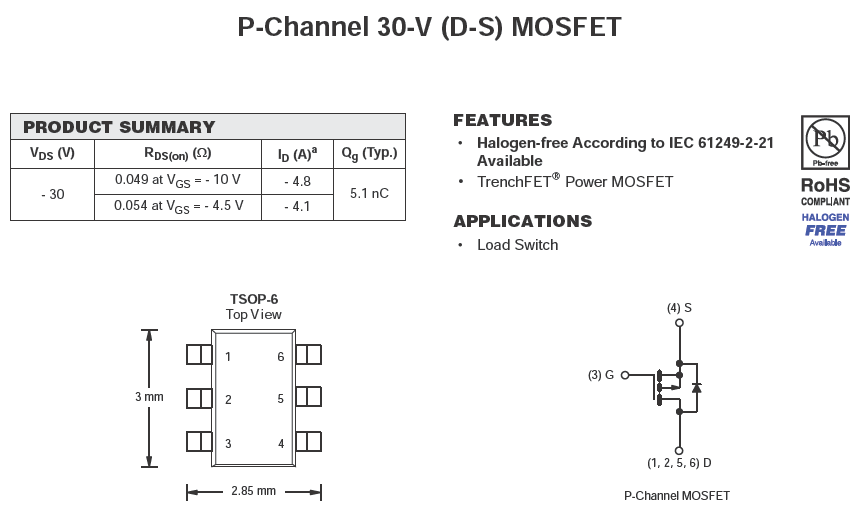

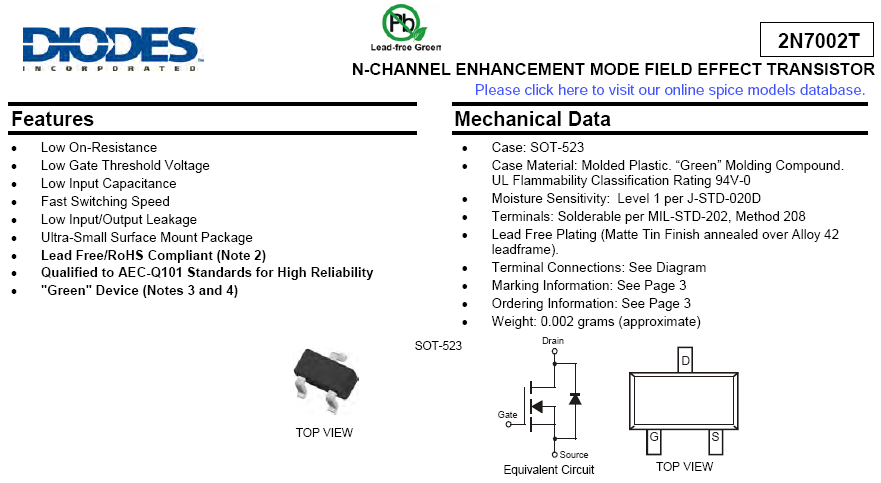

MOSFET Q1、Q2跟Q3應該選擇具有低壓柵極和非常低的導通電阻特性。 例如:Q2=Q3=PMN50XP,在Vgs=-3.3V時,Rds(on)為60mΩ。Q1可以選2N7002,僅供參考,實際應用根據不同的情況選擇合適的MOSFET。

本電路的一大優點就是,整個電路幾乎不存在壓降(當然電流很大的場合另說),巧妙的控制三個MOS管的開啟與截止,最大效率的實現的主副電源的自動切換。

?

MOS管參數詳解

對于實際項目應用,主要關注下面幾個參數,其他參數可以自己根據需求查看手冊。

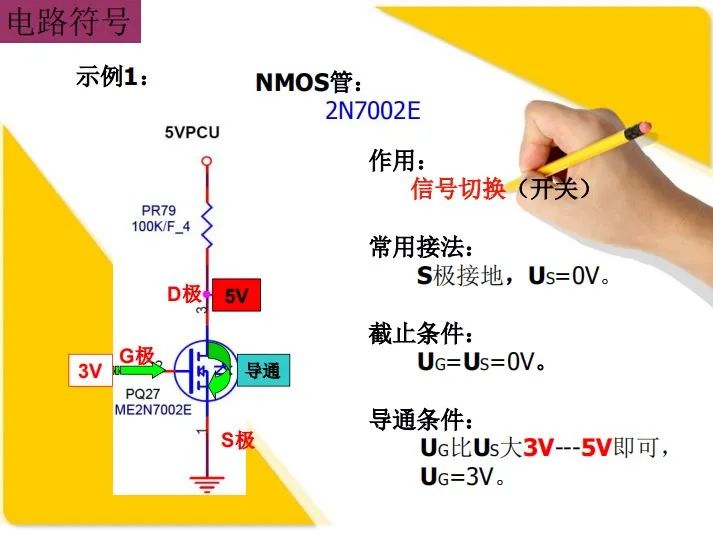

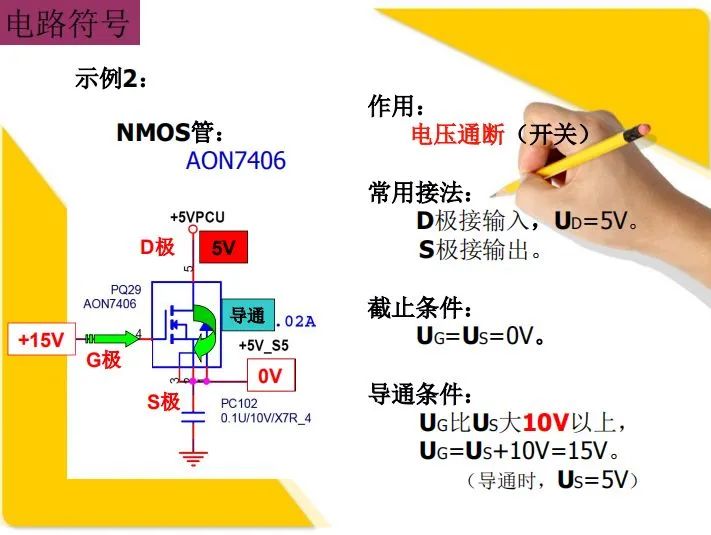

1、VGS(th)(開啟電壓)

當外加柵極控制電壓 VGS 超過 VGS(th) 時,漏區和源區的表面反型層形成了連接的溝道。應用中,常將漏極短接條件下ID等于1毫安時的柵極電壓稱為開啟電壓。此參數一般會隨結溫度的上升而有所降低。

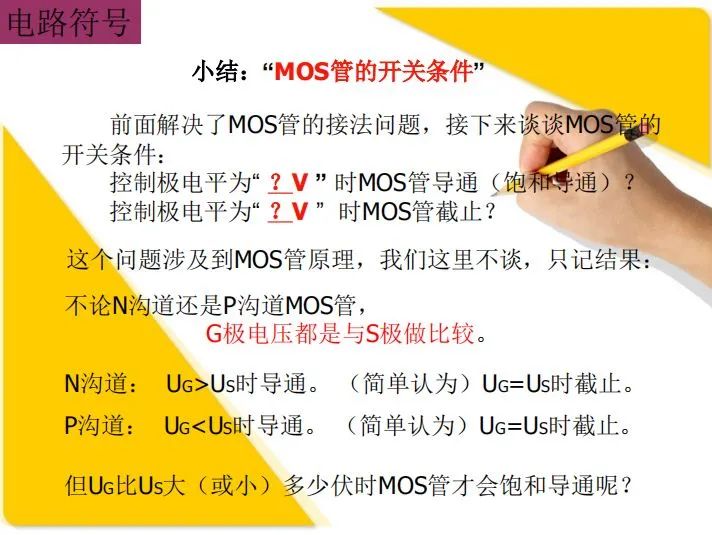

MOS管的導通條件:

N溝道:導通時 Vg>Vs,Vgs> Vgs(th)時導通;

P溝道:導通時 Vg

MOS管導通條件:|Vgs| > |Vgs(th)|

2、VGS(最大柵源電壓)

柵極能夠承受的最大電壓,柵極是MOS管最薄弱的地方,設計的時候得注意一下,加載柵極的電壓不能超過這個最大電壓。

3、RDS(on)(漏源電阻)

導通時漏源間的最大阻抗,它決定了MOSFET導通時的消耗功率。這個值要盡可能的小,因為一旦阻值偏大,就會使得功耗變大。MOS管導通后都有導通電阻存在,這樣電流就會在這個電阻上消耗能量,這部分消耗的能量叫做導通損耗。選擇導通電阻小的MOS管會減小導通損耗。現在的小功率MOS管導通電阻一般在幾十毫歐左右,幾毫歐的也有。

4、ID(導通電流)

最大漏源電流。是指場效應管正常工作時,漏源間所允許通過的最大電流。場效應管的工作電流不應超過ID。一般實際應用作為開關用需要考慮到末端負載的功耗,判斷是否會超過ID。

5、VDSS(漏源擊穿電壓)

漏源擊穿電壓是指柵源電壓VGS為0時,場效應管正常工作所能承受的最大漏源電壓。擊穿后會使得ID劇增。這是一項極限參數,加在場效應管上的工作電壓必須小于 V(BR)DSS 。

6、gfs(跨導)

是指漏極輸出電流的變化量與柵源電壓變化量之比,是表征MOS管放大能力的一個重要參數,是柵源電壓對漏極電流控制能力大小的量度。過小會導致MOS管關斷速度降低,過大會導致關斷速度過快, EMI特性差。

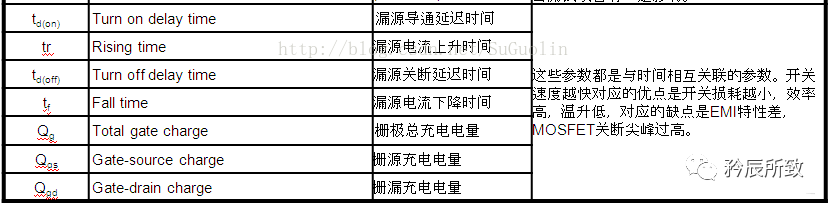

7、充電參數

柵極充電信息:

因為MOS管的都有寄生電容,其被大多數制造廠商分成**輸入電容,輸出電容以及反饋電容。**輸入電容值只給出一個大概的驅動電路所需的充電說明,而柵極充電信息更為有用,它表明為達到一個特定的柵源電壓柵極所必須充的電量。

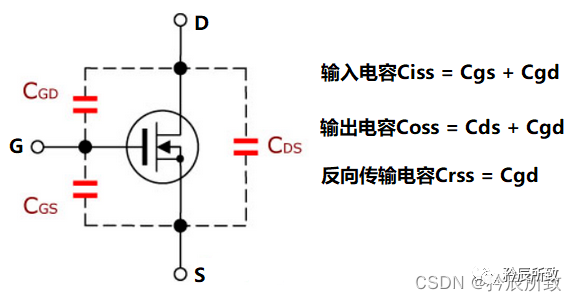

MOS管的寄生電容

寄生電容是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,一個電阻的串聯,低頻情況下表現不明顯,而高頻情況下,等效值會增大。MOS管用于控制大電流通斷,經常被要求數十K乃至數M的開關頻率,在這種用途中,柵極信號具有交流特征,頻率越高,交流成分越大,寄生電容就能通過交流電流的形式通過電流,形成柵極電流。消耗的電能、產生的熱量不可忽視。加在G極的弱驅動信號瞬間變為高電平,但是為了“灌滿”寄生電容需要時間,就會產生上升沿變緩,影響開關頻率。

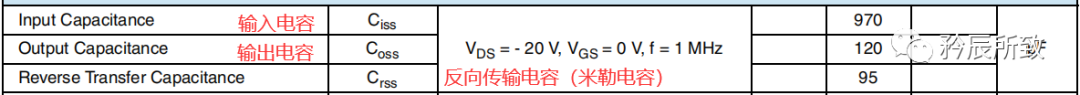

在MOS管的規格書中,有這么幾個電容參數:

對于這幾個電容參數,看下圖所示:

一般從單片機普通應用來說,我們對這個開關要求沒那么高,如果不是特殊應用場合可以不用深究。但是,不能忽略寄生電容,所以在我們的MOS使用時候,就會在GS級加上一個電阻,用來釋放寄生電容的電流。

MOS管的米勒電容

這三個等效電容是構成串并聯組合關系,它們并不是獨立的,而是相互影響,其中一個關鍵電容就是 米勒電容Cgd 。這個電容不是恒定的,它隨著柵極和漏極間電壓變化而迅速變化,同時會影響柵極和源極電容的充電。

額外說明一下,三極管也有米勒電容和米勒效應,但是相對來說MOS管的米勒電容會比三極管的大很多(具體原因由于工藝問題和MOS管特性問題,阻抗大 —> 電流小 —> 充電時間長 —> 等效電容大)。米勒效應會嚴重增加MOS的開通損耗,因為它延長了MOS的開通時間,同時會降低MOS的開關速度。但因為MOS管的制造工藝,一定會產生Cgd,也就是米勒電容一定會存在,所以米勒效應不能避免,只有采用適當的方法減緩。一般有四種方法:①選擇合適的門極驅動電阻RG;②在G和S之間增加電容;③采用負壓驅動;④門極有源鉗位。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論