1 簡(jiǎn)介

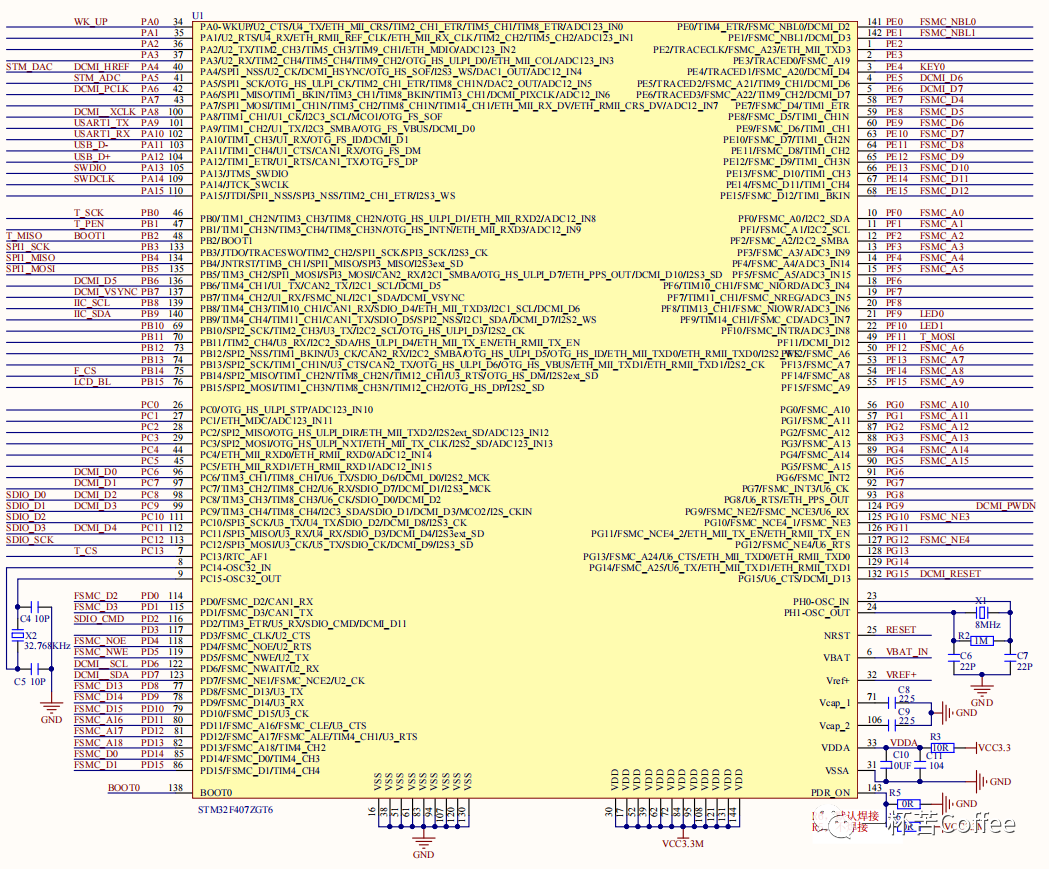

今天主要來(lái)談?wù)?a target="_blank">MCU的設(shè)計(jì),我使用過(guò)的MCU的型號(hào)包括意法半導(dǎo)體的STM32、華大GD32、Infineon的CY8C5868LTI-LP039以及MicroChip的ATSAME70,今天的主角是意法半導(dǎo)體的STM32最小系統(tǒng)設(shè)計(jì),其它MCU電路設(shè)計(jì)后續(xù)進(jìn)行分享。

2 最小系統(tǒng)

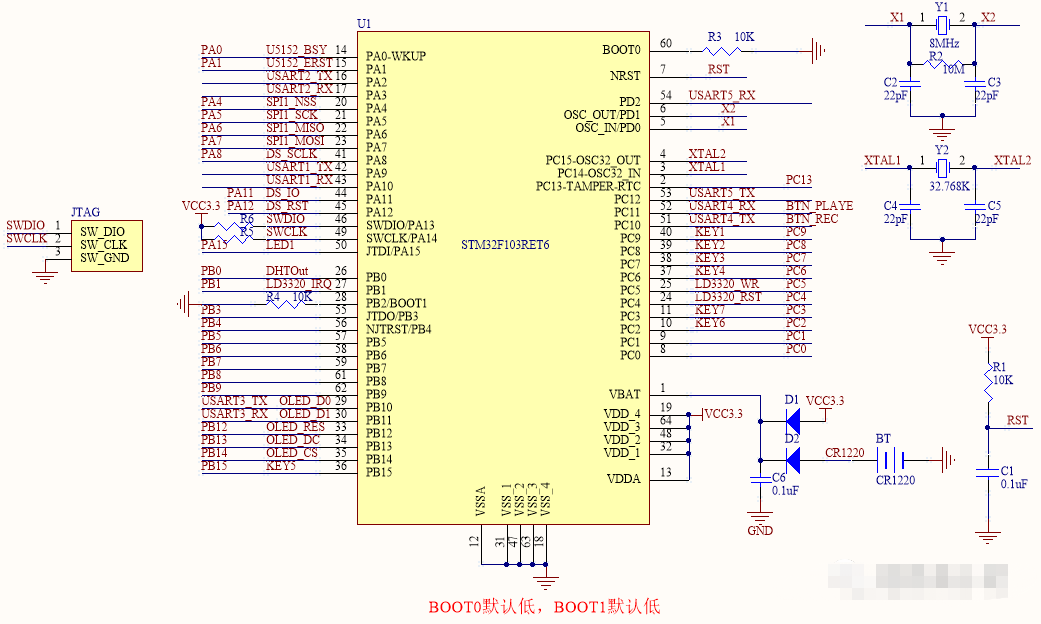

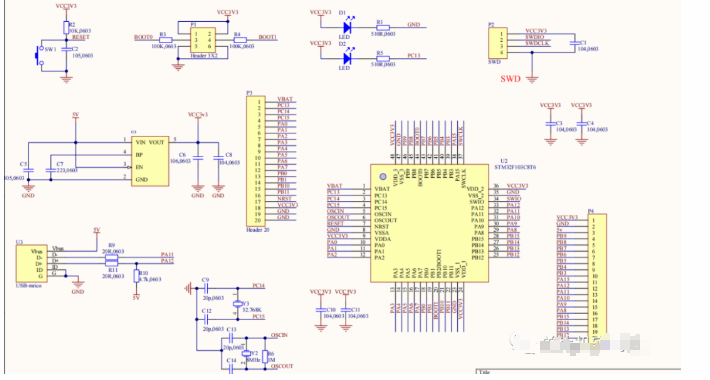

STM32的最小系統(tǒng)設(shè)計(jì)都是類似的,今天以STM32F429IGT6為例。STM32最小系統(tǒng)包含了 電源電路 、 配置電路 、 復(fù)位電路 、 時(shí)鐘電路 、下載電路。

2.1 電源電路設(shè)計(jì)

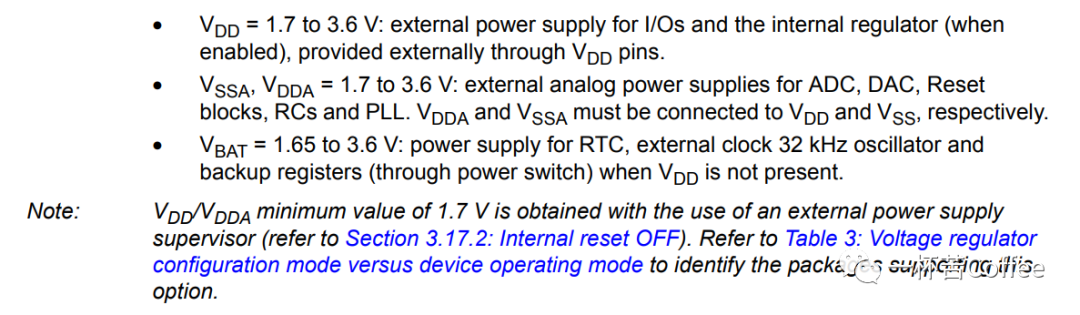

STM32手冊(cè)設(shè)計(jì)指導(dǎo):

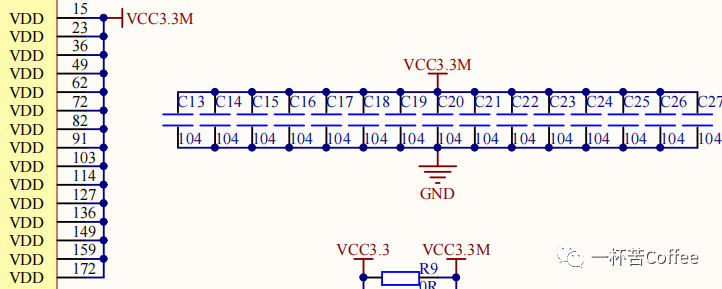

- VDD電源

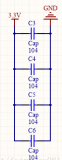

STM32一般采用3.3V供電,根據(jù)手冊(cè)VDD的供電范圍1.7V~3.6V,該電源一般用于外部IO,使能內(nèi)部?jī)?nèi)部穩(wěn)壓器,可對(duì)外供電。以下是VDD實(shí)戰(zhàn)設(shè)計(jì)電路,VDD的每個(gè)電源引腳附近需要放置一個(gè)0.1uF電容,且每個(gè)0.1uF電容需要放置在相應(yīng)PIN腳附近,另外建議在額外增加1到2個(gè)10uF的電容。

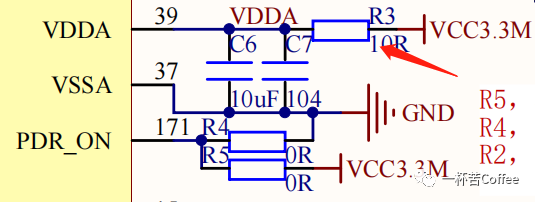

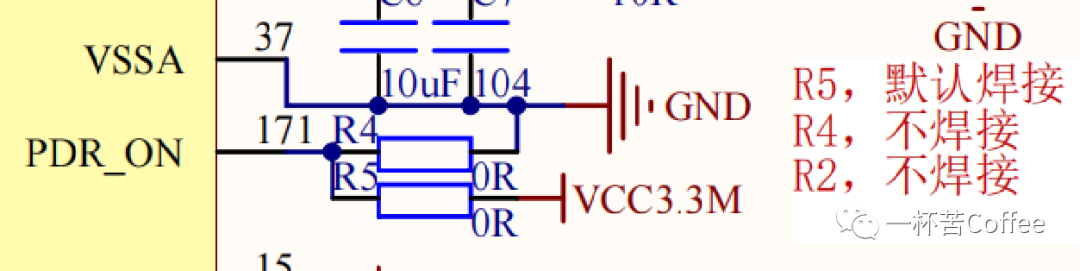

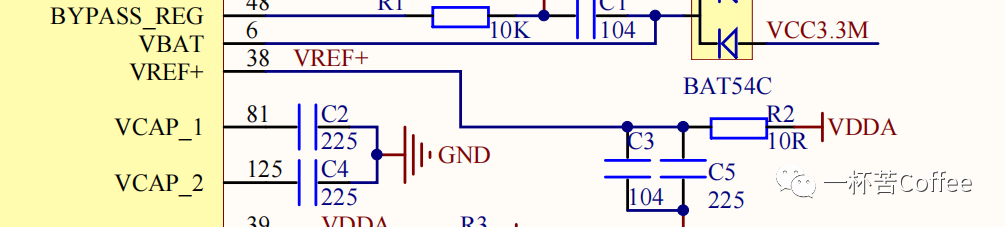

- VDDA電源

VSSA和VDDA的電壓范圍1.7V-3.6V,ADC, DAC,以及Reset模塊的模擬電源。以下是VDDA實(shí)戰(zhàn)設(shè)計(jì)電路,選用3.3V供電,此處R3可能是保守設(shè)計(jì),用于后期調(diào)試(也有可能用于RC濾波),不建議增加10R電阻。對(duì)應(yīng)的位置應(yīng)放置一個(gè)10uF電容和一個(gè)0.1uF電容, 10μF 電容放置在遠(yuǎn)離 IC 的位置,用于平滑電源中的低頻變化, 0.1μF 電容放在靠近 IC的位置,用于平滑高頻電源的變化。小電容器需要更靠近IC,這將更有效過(guò)濾IC產(chǎn)生的高頻信號(hào),或更有效地抑制線路引入的高頻信號(hào)對(duì)IC的影響。

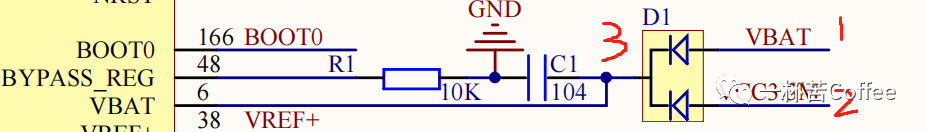

- VBAT電源

VBAT的供電范圍1.65V-3.6V,可作為RTC電源,外部時(shí)鐘32 kHz振蕩器和備份寄存器(通過(guò)電源開(kāi)關(guān))供電。VBAT用于連接紐扣電池,當(dāng)板卡上電時(shí),該P(yáng)IN腳使用板卡上的3.3V電源,當(dāng)板卡下電時(shí),使用紐扣電池供電。D1的型號(hào)為BAT54C主要有以下兩種場(chǎng)景:

- 當(dāng)板卡上電時(shí),即端口2為3.3V,端口1為3V,此時(shí)下二極管導(dǎo)通,端口3和端口2電壓近似相等,此時(shí)1端截止,VBAT=3.3V;

- 當(dāng)板卡不上電時(shí),即端口2浮空,此時(shí)可視為下二極管截止,端口1為3V,上二極管導(dǎo)通,端口3和端口1的電壓近似相等,VBAT=3V;

2.2 控制電路設(shè)計(jì)

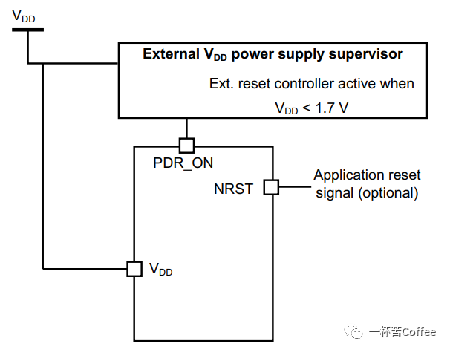

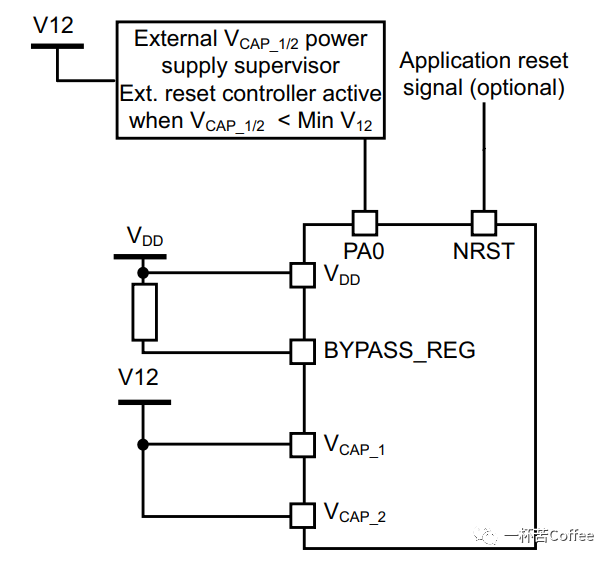

- PDR_ON控制

內(nèi)部上電復(fù)位(POR) /下電復(fù)位(PDR)電路通過(guò)PDR_ON引腳關(guān)閉。外部電源監(jiān)督員應(yīng)監(jiān)視VDD,只要VDD低于指定的閾值,就應(yīng)保持設(shè)備處于復(fù)位模式。

推薦的參考電路為:

- 參考電壓VREF+

在電路設(shè)計(jì)中,我們常常會(huì)用到ADC來(lái)采集電壓數(shù)據(jù),其中VREF+就是ADC的參考電壓,具體ADC的精度需要查看參考手冊(cè),一般為12為ADC。

- Regulator OFF

通過(guò)保持BYPASS_REG高來(lái)禁用調(diào)節(jié)器。Regulator OFF模式允許通過(guò)VCAP_1和VCAP_2引腳向外部提供V12電壓源。

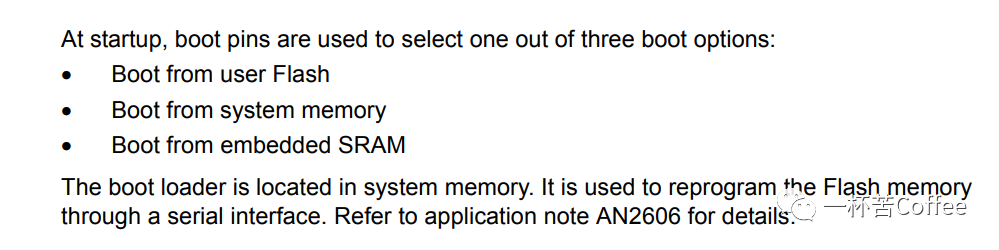

- 啟動(dòng)模式選擇

系統(tǒng)在進(jìn)行復(fù)位之,在系統(tǒng)時(shí)鐘的第四個(gè)上升沿BOOT引腳的值會(huì)被鎖存。用戶可以通過(guò)BOOT0和BOOT1的值,來(lái)設(shè)置系統(tǒng)啟動(dòng)模式。

| 啟動(dòng)模式選擇引腳 | 啟動(dòng)模式 | 說(shuō)明 |

|---|---|---|

| BOOT1 | BOOT0 | |

| X | 0 | 主閃存存儲(chǔ)器 |

| 0 | 1 | 系統(tǒng)存儲(chǔ)器 |

| 1 | 1 | 內(nèi)置SRAM |

手冊(cè)描述見(jiàn)下:

Flash memory啟動(dòng)方式(boot0 = 0)

這種啟動(dòng)方式地址為0x08000000,是STM32內(nèi)置的Flash。一般均使用這種方式,通過(guò)JATG或者SMD下載的代碼通常保存在該Flash中。

System memory啟動(dòng)方式(boot0 = 1;boot1 = 0)

這種啟動(dòng)方式地址為0x1FFF0000,該啟動(dòng)方式的程序一般由廠家提前燒錄好。STM32在出廠時(shí),廠家在內(nèi)部預(yù)置了BootLoader(通常被稱為ISP程序,該部分為ROM,掉電數(shù)據(jù)不丟失),且無(wú)法修改。 使用這種模式的好處是可以通過(guò)串口下載程序固件,將程序下載到BootLader 。

SRAM啟動(dòng)方式(boot0 = 1;boot1 = 1)

這種啟動(dòng)方式的地址為0x20000000,屬于內(nèi)置SRAM,無(wú)法存儲(chǔ)程序。這種啟動(dòng)方式僅用于快速調(diào)試。

2.3 時(shí)鐘電路設(shè)計(jì)

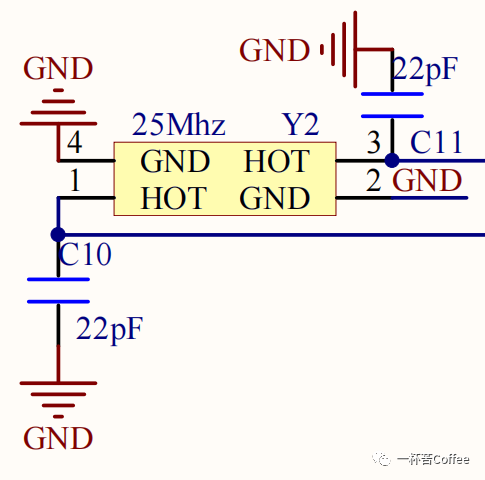

- 主時(shí)鐘

時(shí)鐘是STM32內(nèi)部最核心的器件,它可以提供時(shí)鐘信號(hào)。依賴于這個(gè)信號(hào),STM32中的器件才可以有條不紊地將工作進(jìn)行下去。主時(shí)鐘的范圍 4-25MHz ,此處按照25MHz進(jìn)行設(shè)計(jì),具體設(shè)計(jì)電路見(jiàn)下:

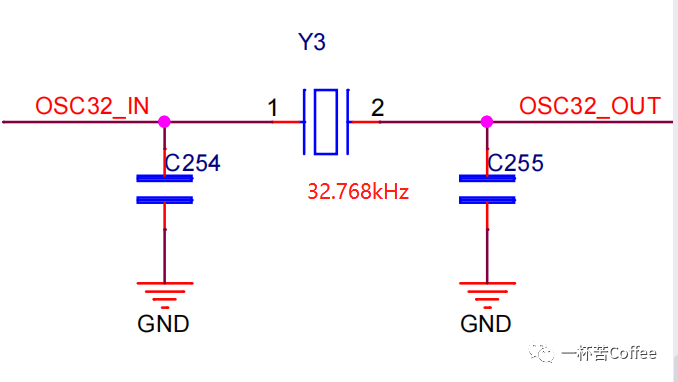

實(shí)時(shí)時(shí)鐘(RTC)是一個(gè)獨(dú)立的BCD定時(shí)器/計(jì)數(shù)器。專用寄存器包含秒,分,小時(shí)(12/24小時(shí)),星期,日期,月,年,BCD(二進(jìn)制編碼的十進(jìn)制)格式。每月28日、29日(閏年)、30日和31日的更正為自動(dòng)執(zhí)行。RTC提供可編程報(bào)警和可編程具有從停止和待機(jī)模式喚醒的周期性中斷。單位秒數(shù)為也有二進(jìn)制格式。

它的時(shí)鐘是由一個(gè)32.768 kHz的外部晶體,諧振器或振蕩器,內(nèi)部低功耗RC振蕩器或高速外部時(shí)鐘除以128。內(nèi)部低速RC典型頻率為32千赫。RTC可以使用外部512 Hz進(jìn)行校準(zhǔn)輸出補(bǔ)償任何天然石英偏差。

使用32.768 kHz的原因?

2的15次方正好等于32768,反過(guò)來(lái)講,如果要把32.768K的時(shí)鐘頻率經(jīng)過(guò)15次分頻的話,得到的頻率正好是1Hz,正好就是1秒鐘時(shí)間,這樣就可以計(jì)時(shí)了。

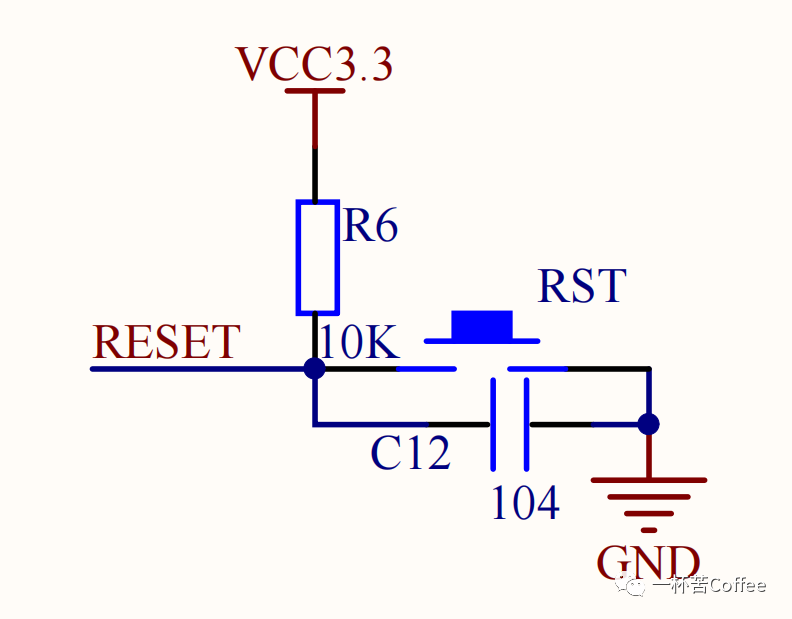

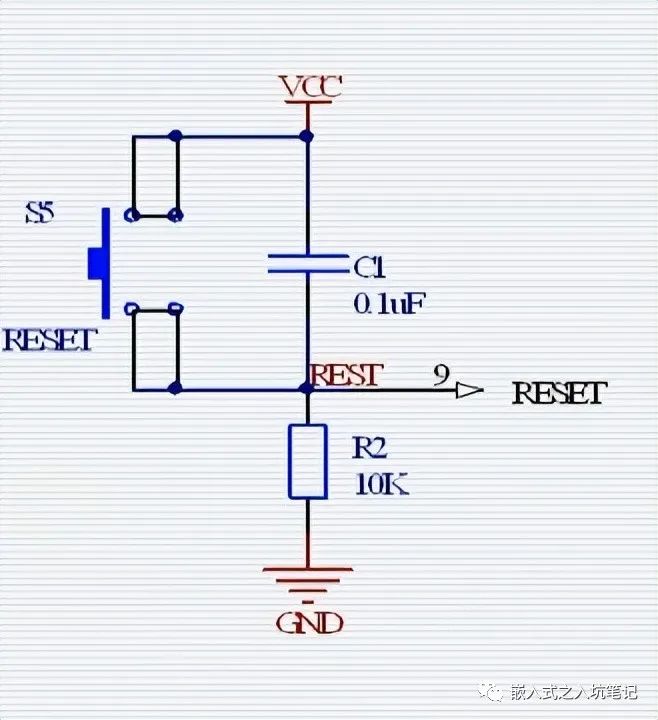

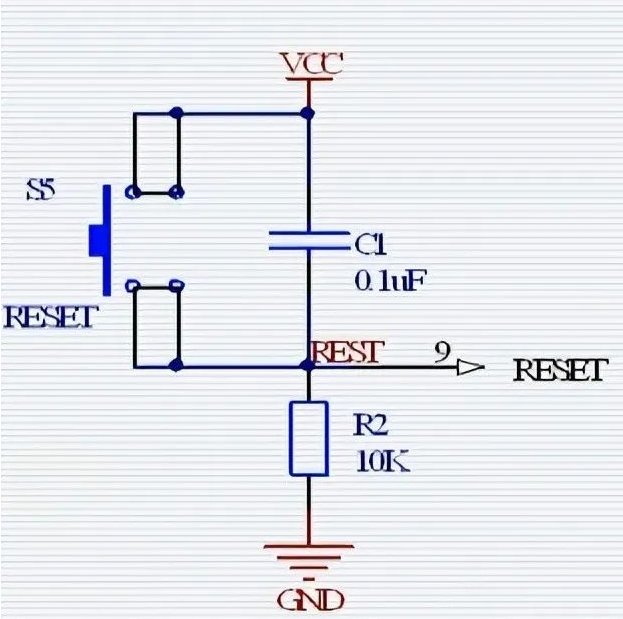

2.4 復(fù)位電路設(shè)計(jì)

復(fù)位電路使程序恢復(fù)到最開(kāi)始運(yùn)行的狀態(tài)。當(dāng)系統(tǒng)運(yùn)行出現(xiàn)異常時(shí),可以通過(guò)手動(dòng)復(fù)位的方式確保系統(tǒng)回到正常運(yùn)行狀態(tài)。其中,C12用于硬件消抖,同事建議增加TVS管,防止靜電損壞器件。看門狗后面有專門文章講解。

2.5 下載電路設(shè)計(jì)

程序下載有兩種方式,分別JTAG模式和 SMD模式 。

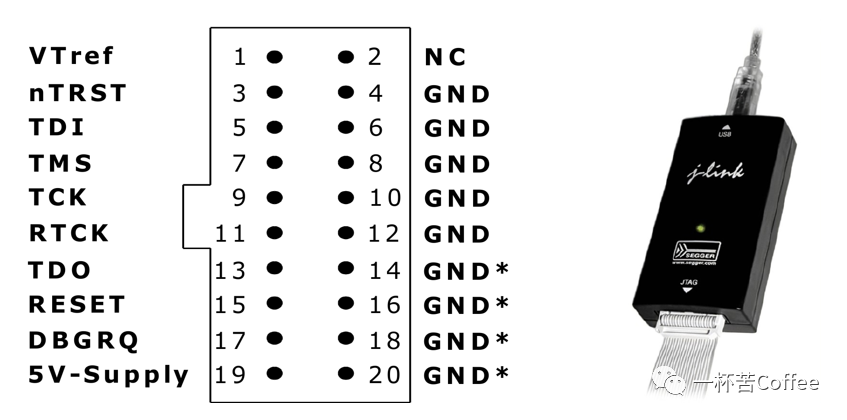

- JTAG模式

JTAG的全稱是Joint Test Action Group (測(cè)試行動(dòng)聯(lián)合組織),它是由幾家主要電子制造商發(fā)起制定的PCB 和IC 測(cè)試標(biāo)準(zhǔn),主要應(yīng)用于電路的邊界掃描測(cè)試和可編程芯片的在線系統(tǒng)編程。

JTAG調(diào)試接口必須使用VCC、GND電源信號(hào),以及TMS、TCK、TDI、TDO四根調(diào)試信號(hào)。

- SMD模式

SWD的全稱是Serial Wire Debug(串行調(diào)試)。SWD是ARM公司設(shè)計(jì)的協(xié)議,用于對(duì)其微控制器進(jìn)行編程調(diào)試。由于SWD專門從事編程和調(diào)試,因此它具有許多特殊的功能,通常在其他任何地方都無(wú)法使用,例如通過(guò)IO線將調(diào)試信息發(fā)送到計(jì)算機(jī)。

由于它是ARM專門為在其設(shè)備中使用而制造的,因此SWD的性能通常是同類產(chǎn)品中最好的。相對(duì)于JTAG接口,使用更少的信號(hào)。四根信號(hào)如下: VCC、GND、SWDIO、SWCLK 。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論