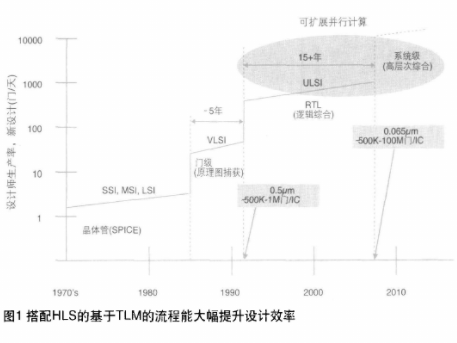

與電子產業的其它領域一樣,在設計自動化領域,借助標準化,許多技術和方法學得以被廣泛接受。例如,硬件描述語言Verilog的標準化使得RTL綜合在80年代中期就開始應用。

在驗證領域,使得基于事務的驗證方法學被廣泛接受的背后推動力是新興標準。諸如OSCI的TLM(事務級建模)2.0和Accellera的標準協同仿真建模接口(SCE-MI)等標準導致了對事務的興趣高漲。此外,驗證流程目前使用硬件加速和仿真來加速基于事務的驗證。

為什么要使用事務?

Cadence Design Systems系統設計和驗證產品管理部門總監Ran Avinun表示,在系統設計建模時,通常要實現三個目標。“第一個是早期軟件開發,第二個是早期系統定義,第三個是可執行規范的描述,當你進行架構權衡的最初會需要它們,”Avinun說。

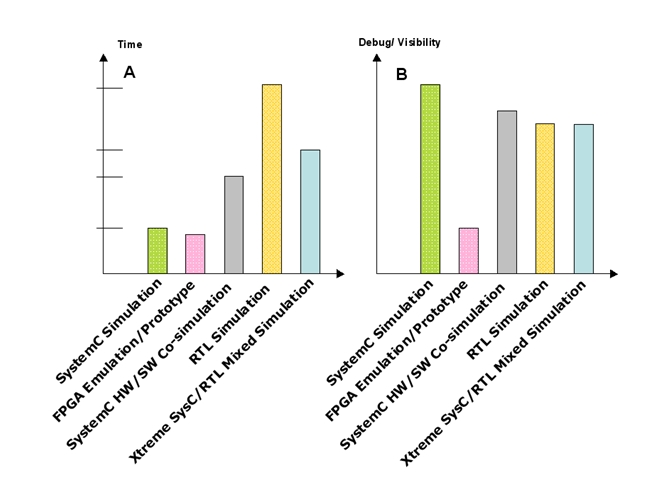

事務適合用在哪些地方?為什么設計工程師希望從事務級模型開始,并最終將這些模型用硬件加速實現?對許多用戶來說,答案在于它可實現快得多的模擬。“如果你將模型寫成TLM,或通過基于事務的驗證進行通信,就可實現更快速的模擬。”Avinun指出。

采用TLM的另一個好處是調試起來更快、更容易。“一般來說,如果你編寫TLM,則生成的錯誤更少,且調試所花的時間也更少。它還提供了一個區分功能和實現的機會,”Avinun稱。

“你想要編寫一個能表述功能的模型,然后將約束分開。它們可以是時鐘約束或是針對特定工藝節點,隨時間變化的東西。當你從一個應用轉到另一個應用或從一個節點轉向另一個節點時,復用模型會更容易。”Avinun說。

事務是如何使用的

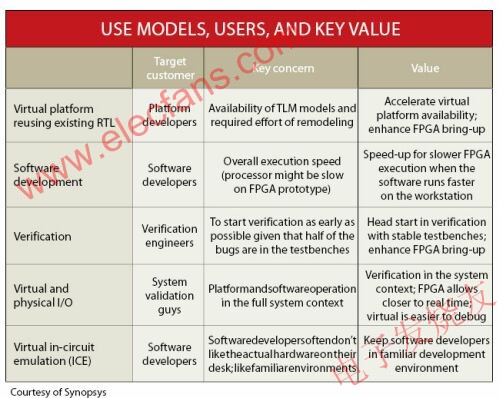

據Synopsys的系統級解決方案產品營銷總監Frank Schirrmeister介紹,當談及TLM時,至少有五種使用模型已成主流(見下表)。排在列表首位的是復用的情況。

在這種情況下,你的設計的很大一部分已經用RTL編寫。此時,最佳方案是一種混合模式的模擬方法學,其中,現有的RTL在FPGA上運行。與此同時,該設計中面向新模塊的TLM作為虛擬樣機運行。

排名第二位的是驗證使用模式。在這種情況下,你啟動一個測試平臺,然后在RTL可用之前開發一個虛擬樣機。這是借助無時序TLM實現的。

“人們從無時序模型著手定義其想要涵蓋的驗證場景。”Schirrmeister說,“當我用手機玩游戲和下載東西時,它還能接電話嗎?借助虛擬平臺,你可在早期很容易地定義這些情況,因為它們由運行在處理器上的軟件完成。隨后你可以在項目中使用它們。”

第三種使用模式是評估系統與外部世界之間的聯系。這些聯系既可以是物理的也可能是虛擬I/O形態。

“例如,對于USB接口,你希望在高保真條件下與真實世界建立連接。但如果這一接口還不存在,你可以用虛擬的方式與其建立連接,這樣你就能著手軟件開發,”Schirrmeister說。

雖然USB是一個具有說服力的例子,但Schirrmeister 還列舉了設計團隊采用該方法學在手機中接入無線接口的例子。它是通過FPGA軟件在虛擬端實現的。

第四個使用模型是針對遠程軟件開發的情況。為滿足物理硬件尚不存在這一情況下的需求,可借助于以虛擬原型形式出現的早期軟件開發環境。“在這種情況下,你要創建一個開發環境,工作在該環境下的軟件開發人員甚至不需要知道其軟件是運行在FPGA原型還是虛擬平臺上。”正如Schirrmeister 所言,這是一種“使軟件開發人員置身實驗室之外”的做法。

第五個(也是最后一個)使用模式是一種涉及在FPGA上構建硬件原型的更簡單的軟件開發方法。“事實證明,FPGA不是運行處理器的首選,因為FPGA更多地是關注DSP。”Schirrmeister 說。通過將處理器模型本身轉為軟件實現,你可以通過連接硬件原型以及在軟件側進行處理獲得更均衡的處理速度。此外,因不再需要考慮軟件的某些部分,可獲得非常快的運行速度。

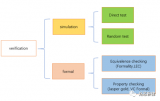

工具和流程演變

為實現進一步發展,TLM需滿足三個要求。其中最顯而易見的兩個是嵌入式軟件開發和設計驗證。“驗證工程師需要簡單、直接的測試。”Schirrmeister說。另一個不斷發展變化的要求是隨機測試生成,它采用校驗監控器以及包含用TLM表述的用于系統級芯片(SoC)綜合驗證的覆蓋范圍。隨機測試模式的生成、覆蓋檢查以及監視器的使用等情況將及時傳播到TLM領域和虛擬樣機。

TLM有待融合的第三個要求是與實現的直接鏈接。“我們稱這一流程為‘TLM到GDSII’。”Schirrmeister 說。 “過去有兩個世界。一個側重虛擬平臺,而另一個側重高級綜合。我們認為在將來某個時候,這兩個世界將合二為一。”

對許多設計工程師以及EDA供應商來說,問題是如何在虛擬平臺和高級綜合(HLS)流程之間建立鏈接。

“一直以來都試圖用TLM鏈接這些世界。”Forte Design Systems的市場和銷售副總裁Brett Cline說。“但問題始終是該標準只考慮了驗證而沒考慮綜合。在TLM規范中缺少了一些非常基本但對硬件設計而言至關重要的東西。例如,沒有專有的復位機制。”

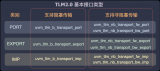

OSCI內部的努力最終導致了TLM 1.0標準的修訂,進而催生了TLM 2.0版本。 “我們對OSCI TLM 1.0進行了擴展,做了一些你或許期望我們做的一些事,也即對綜合的了解。”Cline說。“TLM 2.0是一個更加關注綜合的標準,它主要專注于基于總線的系統。”TLM 2.0包括各種面向基于總線系統的事務應用編程接口(API)。

Cline認為,由于驗證工程師和實現之間的鴻溝,虛擬平臺和HLS是分開的。“人們從兩個角度來看待它。你或者是一位驗證者(從虛擬平臺角度來看),或者是一位用SystemC進行硬件設計的實現者。”Cline說。“現在,驗證者已經認識到,TLM代表著一條無需重寫就能完成實現的可行途徑。同時,實現者也正開始明白該如何將一些東西集成進運行得非常快的系統模型。”

Schirrmeister表示,過去,大部分廠商和用戶在隔離時已經使用了虛擬平臺和/或HLS。“創制TLM 2.0是為有助于早期軟件開發和高性能模擬,但它對HLS考慮不多。實際上,我們正借助可綜合子集來推動TLM 2.0標準解決HLS需求。這是業界需應對的發展方向。”他說。

硬件生成

基于事務驗證的一個重要組成是借助TLM可實現極高速驗證的硬件。最近,Synopsys推出了其快速原型系統HAPS-60系列作為Confirma平臺的組成部分。基于賽靈思Virtex-6 FPGA構建的HAPS-60系統是對“自建還是購買”決策的最新回應,過去涉及快速原型技術時會面臨該問題。

該系列產品包括三種型號:HAPS-61(單 FPGA,多達450萬門容量),HAPS-62(雙FPGA,900萬門容量)以及HAPS-64(4 FPGA,1800萬門容量)。除了容量是上一代HAPS-50系列的一倍以外,HAPS-60還將性能到時鐘頻率高達200MHz。

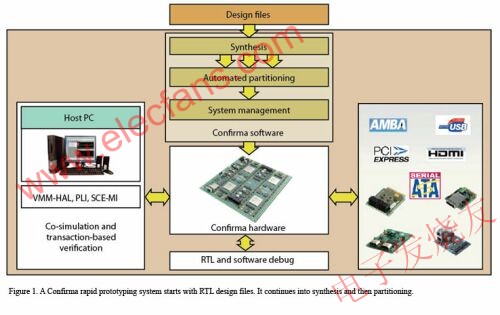

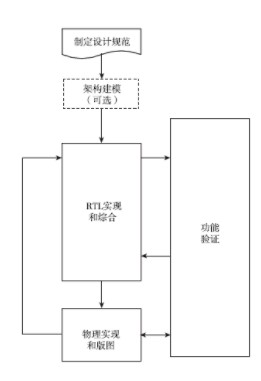

對Confirma快速原型系統(圖1)中組件的一種高級概述是從貫穿綜合始終的RTL設計文件開始。接著在快速原型板上對設計進行分割。系統的Confirma軟件執行這一分割過程,而且該軟件明白其目標是一塊HAPS板。然后,用戶就可以進行模擬原型所需的接口實例化,以及協同仿真和基于事務的驗證所需的將設計鏈接到其它環境中。

圖1:一個Confirma快速原型系統從RTL設計文件開始,接著進行綜合然后對設計進行分割。

早期的快速原型系統與帶寬的限制相沖突,這一限制是由FPGA引腳數無法跟上設計規模和速度要求而引起。過去,對該問題的解決辦法是互連復用,這可以作為權宜之計,但最終會限制系統的整體性能。

HAPS-60系統采用自動高速時分復用避免了這些帶寬限制。該系統的軟件自動(而不是強迫用戶手動)插入時分復用邏輯(圖2左)。“按照過去的方式將需要深入解讀RTL設計文件。”Synopsys方案營銷業務拓展經理Doug Amos說。

圖2:HAPS-60系統通過采用自動高速時分復用避免了帶寬限制。該系統的軟件自動(而不是強迫用戶手動)插入時分復用邏輯(圖2左)

這種自動化方法最終實現了一種與自動時序同步耦合的1Gb數據速率。這相當于將管腳帶寬效率提高7倍,以及將平均系統性能提高30%(圖2右)。

包含UMRbus架構使得HAPS-60系統尤其適用于基于事務的驗證(圖3)。UMRbus是一種高性能、低延時通信總線,它能為所有板載FPGA、存儲器、寄存器和其它資源提供連接。

“UMRbus被用于整個電路板控制,”Amos說。它支持用于配置和監控的對整個系統的遠程訪問。許多設計互動和監控功能(圖3右)均包括在內。“用戶可以控制設計、訪問設計、補充設計、回讀存儲器并調試糾錯,”Amos說。

UMRbus還支持若干先進模式,包括基于事務的驗證和協同仿真(圖3左)。 “用戶可編寫程序來實現各種設計互動和監控功能,” Amos說。該系統包含許多基于主機的調試模式,這些模式過去是與仿真關聯的。

當涉及基于事務的驗證時,通過使用SCE-MI 2.0事務接口(圖4),HAPS-60系統可以大大縮短驗證時間。“這正是開發SCE-MI 2.0的目的,”Amos說。“SCE-MI接口使我們能用軟件進行事務處理,將事務傳遞到硬件,以及硬件再生成事務。該技術被用在仿真器類型的環境中來模仿真實世界的做法。”

現在,HAPS-60系統使這種仿真器型方法學可以在一個快速原型系統上實現。SCE-MI允許在原型部分使用高級概念。“這個系統模糊了原型和仿真器之間的界限,而SCE-MI是使其得以實現的推手,”Amos說。其結果是,當在HAPS硬件上運行簡化的測試平臺時,速度可比仿真快10,000倍。

支持TLM 2.0

提供支持基于事務的驗證的另一家硬件供應商EVE,最近在其ZeBu仿真平臺產品線中增加了對TLM 2.0標準的支持。 TLM 2.0是Open SystemC Initiative(OSCI)用于SystemC模型互操作性和重用的接口標準。“考慮到我們在此背景下引入了仿真器,因此對我們來說,這更像是基于事務的協同仿真,”EVE-USA總經理Lauro Rizzatti說。

EVE已通過一種事務處理適配器(圖5)實現了對 TLM 2.0的支持。該適配器支持多個目標和發起人、阻斷和非阻斷傳輸接口,以及松散定時(LT)、松散定時時間解耦(LTD)和近似定時(AT)編碼方式。

在系統級,用戶可以將虛擬平臺、TLM 2.0事務處理適配器以及先進SystemVerilog硬件驗證環境整合起來。在仿真器級,ZeBu TLM-2.0事務處理適配器是一種可實現與其它ZeBu事務處理器的互操作的開放架構,其它的ZeBu事務處理器既或是來自EVE的事務處理器目錄,或是由ZEMI–3生成。ZEMI–3是EVE用于事務處理器總線功能模型(BFM)的行為SystemVerilog編譯器,該編譯器使得編寫周期精確的BFM以及與C++或SystemVerilog測試平臺進行信息交換變得非常容易。

據Rizzatti稱,在基于事務的模式中,70%至80%的EVE客戶使用ZeBu。“在簡單的基于C的循環模式(而不是事務模式)中,他們也可能將其用于調用。但即使這樣做,他們仍然因為事務模式的好處而采用該模式,”他說。

EVE營銷總監Ron Choi表示,對TLM 2.0的支持使EVE的仿真器在互操作性方面更上一層樓。“多年來,我們都采用一個事務級接口。但它必須通過一個專有API來實現。這是一種非常有用的方法學,但現在對于基于標準的方法有更強烈的訴求,”他說。

TLM 2.0事務處理適配器解決了設計工程師為橋接不同產品必須編寫不同代碼這個問題。“一般來說,ESL工具總是有能力通過編程語言接口(PLI)連接到RTL模擬器,以及通過API調用C/C++函數連接到仿真器,”Rizzatti說。“這要求他們針對不同的接口編寫外圍應用。他們在編程時必須寫入其自有的互操作性。一個更好的辦法是使用定義了互操作層的 TLM 2.0,它使用戶無需考慮底層實現。這樣,他們是否使用SystemC模型就不重要了。”

歡迎轉載,本文來電子發燒友網(http://m.xsypw.cn/)

電子發燒友App

電子發燒友App

評論