隨著軟件定義無(wú)線電平臺(tái)在軍事航空航天領(lǐng)域以及近在一些消費(fèi)無(wú)線電和電子領(lǐng)域的出現(xiàn),現(xiàn)場(chǎng)可編程邏輯 (FPGA) 作為可重新編程數(shù)字信號(hào)處理 (DSP) SDR 引擎的用途變得越來(lái)越重要。

現(xiàn)場(chǎng)可編程邏輯一直是連接寬帶 A/D 和 D/A 轉(zhuǎn)換器、數(shù)字接收器和通信鏈路等高速外設(shè)到嵌入式實(shí)時(shí)系統(tǒng)中可編程處理器的電路。

FPGA(現(xiàn)場(chǎng)可編程門陣列)特別適合處理時(shí)鐘、同步以及馴服這些專用設(shè)備所需的其他各種定時(shí)電路。此外,F(xiàn)PGA 非常適合數(shù)據(jù)格式化任務(wù),例如串并轉(zhuǎn)換、數(shù)據(jù)打包、時(shí)間戳、多路復(fù)用和數(shù)據(jù)包形成。

但它們的 DSP 功能已成為 FPGA 固有的重要功能之一,過(guò)去幾年 FPGA 供應(yīng)商對(duì)該技術(shù)的工程和營(yíng)銷投資急劇增加就證明了這一點(diǎn)。

數(shù)字信號(hào)處理任務(wù)

在傳統(tǒng)的軟件無(wú)線電接收器系統(tǒng)中,經(jīng)過(guò)轉(zhuǎn)換和濾波的基帶信號(hào)作為時(shí)域波形的復(fù)雜樣本流發(fā)送到 DSP。DSP 必須處理所有解調(diào)任務(wù)以及基于接收信號(hào)分析的更別決策。

信號(hào)智能接收器通常通過(guò)首先對(duì)信號(hào)進(jìn)行頻譜分析來(lái)估計(jì)使用的調(diào)制類型來(lái)對(duì)信號(hào)進(jìn)行分類,然后應(yīng)用解調(diào)算法來(lái)確定是否提取了有用的信息,例如可理解的語(yǔ)音或有意義的數(shù)據(jù)。

DSP 的其他重要任務(wù)包括解密、數(shù)據(jù)存儲(chǔ)、通道切換、到其他系統(tǒng)的信號(hào)路由、記錄??活動(dòng)以及向操作員發(fā)送音頻或數(shù)字?jǐn)?shù)據(jù)以供收聽或顯示。

在手機(jī)基站中,數(shù)字信號(hào)處理任務(wù)的數(shù)量隨著每個(gè)新通信標(biāo)準(zhǔn)的增加而增加。復(fù)雜的數(shù)字語(yǔ)音和數(shù)據(jù)協(xié)議的激增需要解碼、卷積、成幀、糾錯(cuò)和聲碼。

采樣率要求的穩(wěn)步增加加劇了這些額外任務(wù)的處理負(fù)載。為了支持寬帶 CDMA 等新應(yīng)用,DSP 距離天線越來(lái)越近。

為了滿足這些需求,DSP 時(shí)鐘速率已增加到 200 MHz 以上,并且許多新器件具有兩個(gè)或更多硬件乘法器。然而,作為系統(tǒng)中昂貴、耗電的資源之一,限度地減少 DSP 的大量工作負(fù)載顯然非常重要。

FPGA 在 SDR 中的作用

在過(guò)去五年中,為了適應(yīng) DSP 功能,F(xiàn)PGA 在幾個(gè)關(guān)鍵領(lǐng)域取得了巨大的進(jìn)步。這些器件的柵極密度很好地遵循摩爾定律,大約每年半增加一倍。近發(fā)布的一些設(shè)備號(hào)稱擁有 1000 萬(wàn)個(gè)門!門陣列通常被構(gòu)造為配備存儲(chǔ)器并能夠執(zhí)行數(shù)學(xué)函數(shù)的邏輯單元。這些高密度邏輯單元現(xiàn)在可用于各種基本“”,以支持快速乘法器、用于處理 FFT 處理的塊存儲(chǔ)器以及用于 FIR 濾波器的分布式存儲(chǔ)器。

FPGA 綜合工具現(xiàn)在支持“可參數(shù)化”內(nèi)核,這些內(nèi)核接受位寬定義并自動(dòng)生成內(nèi)核結(jié)構(gòu)以滿足信號(hào)處理精度要求,而不會(huì)浪費(fèi)門。

現(xiàn)在可以使用多種前端設(shè)計(jì)工具來(lái)滿足硬件和軟件系統(tǒng)工程師的各種輸入偏好。其中包括框圖系統(tǒng)生成器、原理圖處理器以及用于 Verilog 和 VHDL 的輸入語(yǔ)言編譯器。新模擬器的速度、準(zhǔn)確性和易用性簡(jiǎn)化了新設(shè)計(jì)的測(cè)試,并限度地減少了調(diào)試應(yīng)用程序所花費(fèi)的時(shí)間。

第三方供應(yīng)商現(xiàn)在提供 IP 內(nèi)核,以補(bǔ)充 FPGA 供應(yīng)商提供的標(biāo)準(zhǔn)內(nèi)核。這些范圍從完整的 DSP 處理器到高速互聯(lián)網(wǎng)調(diào)制解調(diào)器等特定應(yīng)用模塊。憑借這些新的商業(yè)“現(xiàn)成”功能,F(xiàn)PGA 現(xiàn)在能夠打入通用 ASIC 市場(chǎng)以及 DSP 市場(chǎng)。

更重要的是,F(xiàn)PGA 的數(shù)字信號(hào)處理能力通常可以勝過(guò)通用 DSP。例如,如果寬帶 FIR 數(shù)字濾波器在單個(gè)時(shí)鐘周期內(nèi)需要 32 個(gè) MAC(乘法/累加運(yùn)算),則僅具有兩個(gè)乘法器的通用 DSP 將遠(yuǎn)遠(yuǎn)達(dá)不到要求。另一方面,F(xiàn)PGA 可以輕松整合 32 個(gè) MAC 內(nèi)核來(lái)處理任務(wù)。

靈活且可重復(fù)使用

這種基于 COTS 的軟件無(wú)線電系統(tǒng)是實(shí)現(xiàn)各種應(yīng)用的理想平臺(tái)。通過(guò)將新的 FPGA 設(shè)計(jì)工具和 IP 庫(kù)用于這些高度可配置的基于 FPGA 的 COTS 板級(jí)產(chǎn)品,系統(tǒng)設(shè)計(jì)人員可以消除對(duì)定制板的需求。由于 FPGA“硬件”可以從根本上重新配置,無(wú)需新的電路板設(shè)計(jì),因此當(dāng)前項(xiàng)目中使用的相同產(chǎn)品可以輕松地重新配置以適應(yīng)未來(lái)的應(yīng)用。

隨著新的軟件無(wú)線電算法的開發(fā),它們可以首先在 DSP 上進(jìn)行測(cè)試,利用更廣泛的代碼生成、仿真和優(yōu)化工具。完成后,該算法可以移植到 FPGA,以實(shí)現(xiàn)更好的實(shí)時(shí)操作或支持許多并行通道的處理負(fù)擔(dān)。,為了過(guò)渡到大批量生產(chǎn),大多數(shù) FPGA 設(shè)計(jì)都可以輕松轉(zhuǎn)換為定制 ASIC 的掩模工具。

雖然重新編程 FPGA 來(lái)處理新功能可能比為 DSP 編寫新算法復(fù)雜一些,但這種努力程度的差距似乎正在縮小。FPGA 設(shè)計(jì)工具不再是硬件設(shè)計(jì)人員的專屬領(lǐng)域,現(xiàn)在越來(lái)越廣泛地被軟件工程師使用,確保這一重大技術(shù)轉(zhuǎn)變將代表未來(lái)嵌入式系統(tǒng)設(shè)計(jì)的主流范例。

軟件無(wú)線電模塊應(yīng)用

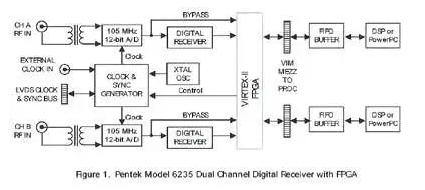

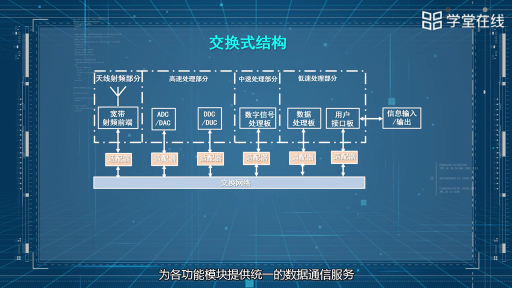

DSP 驅(qū)動(dòng)的 FPGA SDR 平臺(tái)的強(qiáng)大功能和靈活性的一個(gè)說(shuō)明性示例(如下圖 1 所示)是連接到四路 DSP 處理器 VME 板的雙通道數(shù)字接收器子卡模塊。它包含兩個(gè)能夠以高達(dá) 100 MHz 采樣率運(yùn)行的 12 位 A/D 轉(zhuǎn)換器,以及兩個(gè)可轉(zhuǎn)換和過(guò)濾寬帶數(shù)字化輸入的選定部分的數(shù)字下轉(zhuǎn)換器。

板載 FPGA 接受兩個(gè) A/D 轉(zhuǎn)換器的實(shí)際輸出以及兩個(gè)數(shù)字下變頻器的復(fù)雜基帶輸出。FPGA 實(shí)現(xiàn) VIM(速度接口夾層)接口,將數(shù)據(jù)直接傳送到處理器板上的每個(gè) DSP 或 PowerPC,其中 FIFO 緩沖區(qū)支持 DMA 塊數(shù)據(jù)傳輸,速率高達(dá) 400 MB/秒。

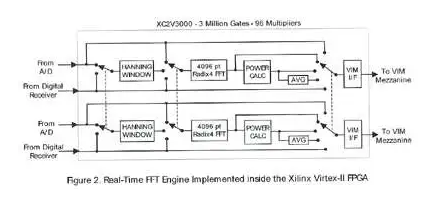

著眼于添加 DSP 功能,此類平臺(tái)中 FPGA 的自然選擇是 Xilinx Virtex-II 系列。XC2V3000 具有 96 個(gè)專用 18×18 乘法器模塊和超過(guò) 200 KB 的塊 RAM,可提供豐富的信號(hào)處理資源組合,甚至適用于一些更重要的應(yīng)用。

在模塊的基本工廠配置中,F(xiàn)PGA 仍然為板上的各種器件執(zhí)行傳統(tǒng)的定時(shí)、格式化和粘合邏輯任務(wù)。由于這些功能相對(duì)簡(jiǎn)單,因此僅消耗 6% 的可編程邏輯。這使得 94% 的邏輯塊、所有 96 個(gè)乘法器以及幾乎整個(gè)塊 RAM 可用于添加 DSP 算法。

為了幫助展示這些未開發(fā)資源的力量,啟動(dòng)了一個(gè)工程項(xiàng)目來(lái)實(shí)施高性能 FFT 引擎。由于通信、雷達(dá)和信號(hào)智能系統(tǒng)都利用 FFT 進(jìn)行跟蹤、調(diào)諧和圖像處理操作,因此 FFT 仍然是的處理器性能基準(zhǔn)測(cè)試算法之一。

簡(jiǎn)而言之,F(xiàn)FT 接受輸入時(shí)域樣本塊,并將其轉(zhuǎn)換為輸出頻域樣本塊。由于計(jì)算相當(dāng)復(fù)雜,它消耗了大量DSP處理資源,成為FPGA實(shí)現(xiàn)的主要候選者。

構(gòu)建 FFT

執(zhí)行 FFT 計(jì)算有效的方法之一是 radix-4“蝴蝶”算法的迭代。在每個(gè)蝶形內(nèi)部,四個(gè)輸入數(shù)據(jù)點(diǎn)乘以正弦表中的系數(shù),然后組合起來(lái)產(chǎn)生四個(gè)輸出點(diǎn)。重復(fù)這種蝶形運(yùn)算,直到處理完所有輸入點(diǎn),四個(gè),代表一個(gè)“階段”。要實(shí)現(xiàn) 4,096 點(diǎn) FFT,需要六級(jí)蝶形運(yùn)算。

與傳統(tǒng)可編程處理器相比,使用 FPGA 計(jì)算 FFT 的好處之一是可以同時(shí)計(jì)算大量乘法器。

在上面的 4,096 示例中,總共需要 60 個(gè)乘法器來(lái)并行實(shí)現(xiàn)所有六個(gè) FFT 蝶形級(jí)。由于 XC2V3000 具有 96 個(gè)可用乘法器,因此很明顯為什么 FPGA 通常可以顯著優(yōu)于僅具有兩個(gè)或四個(gè)硬件乘法器的標(biāo)準(zhǔn) DSP 處理器,特別是對(duì)于 FFT 等算法。

由于 FFT 本質(zhì)上是一種面向塊的算法,因此當(dāng)可自由尋址的 RAM 支持快速訪問(wèn)所有輸入和輸出樣本時(shí),F(xiàn)FT 的運(yùn)行效率。然而,這種隨機(jī)數(shù)據(jù)可用性的理想模型與來(lái)自 A/D 轉(zhuǎn)換器的順序輸入數(shù)據(jù)樣本流相反。

幸運(yùn)的是,F(xiàn)PGA 的可配置塊 RAM 資源可以重組,形成一個(gè)存儲(chǔ)器結(jié)構(gòu),將適當(dāng)?shù)臉颖静⑿休斎氲揭娴乃膫€(gè)輸入數(shù)據(jù)存儲(chǔ)器端口,從而解決數(shù)據(jù)可用性問(wèn)題。這種專有的內(nèi)存架構(gòu)允許以連續(xù)的脈動(dòng)方式處理后續(xù)輸入塊,以便所有六個(gè)階段中的所有乘法器都可以始終高效地使用。

對(duì)于每個(gè) FPGA 時(shí)鐘周期,每個(gè) radix-4 蝶形運(yùn)算處理四個(gè)輸入樣本。因此,當(dāng)FPGA處理時(shí)鐘等于A/D時(shí)鐘時(shí),上述架構(gòu)的運(yùn)行速度比實(shí)時(shí)快四倍。通過(guò)合適的硬件復(fù)用方案,同一 FFT 引擎可用于處理四個(gè)輸入數(shù)據(jù)流,而不是僅一個(gè)。

在此示例中,由于兩個(gè) A/D 轉(zhuǎn)換器和 FPGA 的時(shí)鐘頻率均為 100 MHz,因此 FPGA 僅以一半容量工作。但只要付出一點(diǎn)額外的努力,引擎就可以設(shè)置為處理兩個(gè)通道的 50% 輸入重疊處理,以充分利用硬件。在這種情況下,每個(gè) FFT 的流水線執(zhí)行時(shí)間是驚人的 10.24 微秒!這比以 100 MHz 采樣率收集 4,096 個(gè)輸入點(diǎn)所需的時(shí)間快四倍,與實(shí)時(shí)執(zhí)行四次 FFT 一致。

FFT 增強(qiáng)

由于 96 個(gè)乘法器中僅使用了 60 個(gè)用于 FFT 算法,因此結(jié)合了其他功能。在四個(gè)復(fù)數(shù)輸入流中的每一個(gè)上,都可以應(yīng)用一個(gè)可選的漢寧窗,需要八個(gè)額外的乘法器。由于 FFT 和 Hanning 窗的系數(shù)使用單獨(dú)的 FPGA 表存儲(chǔ)器,因此可以用替代輸入窗函數(shù)代替 Hanning 窗。

另外八個(gè)乘法器用于在 FFT 輸出處執(zhí)行可選的功率計(jì)算,其中四個(gè)輸出中每一個(gè)輸出的實(shí)部和虛部進(jìn)行平方,然后相加。,平均器級(jí)將 50% 輸入重疊 FFT 的兩個(gè)輸出相加,以改善信噪比特性。

在 FPGA 的輸出端,多路復(fù)用器允許將每個(gè)信號(hào)處理階段的結(jié)果定向到處理器接口。下圖2 顯示了圖1所示子卡模塊的FPGA內(nèi)部的所有基本功能塊。

結(jié)論

對(duì)于 4,096 點(diǎn)復(fù)雜 FFT,該 FPGA 引擎的執(zhí)行速度為 10.24 微秒,其性能比在 400 MHz G4 PowerPC 上運(yùn)行的優(yōu)化 FFT 算法的基準(zhǔn)高出十倍!

為了實(shí)現(xiàn)優(yōu)于 90 dB 的計(jì)算動(dòng)態(tài)范圍,采用了多種技術(shù)來(lái)減少 FPGA 整數(shù)運(yùn)算中固有的舍入和截?cái)嗾`差。通過(guò)部署可用的 FPGA 資源優(yōu)化執(zhí)行速度后,整個(gè)設(shè)計(jì)利用了 XC2V3000 器件 96 個(gè)乘法器中的 76 個(gè)、99% 的邏輯片和 97% 的塊 RAM。

盡管這種特殊的 FPGA 組件由于近推出而仍然價(jià)格昂貴,但球柵陣列封裝圖案的兩個(gè)同心子集可容納同一系列中的兩個(gè)較小的器件,從而為要求不高的應(yīng)用節(jié)省成本。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論