引言

隨著微電子技術(shù)的飛速發(fā)展,集成電路規(guī)模按照摩爾定律(微芯片上集成的晶體管數(shù)目每18個(gè)月翻一番)飛速提高,片上系統(tǒng)(SystemOnChip,簡(jiǎn)稱SOC)技術(shù)成為國(guó)際超大規(guī)模集成電路的發(fā)展趨勢(shì)。在SOC系統(tǒng)設(shè)計(jì)中,為了能夠快速、穩(wěn)定的形成產(chǎn)品,IP核積累和復(fù)用技術(shù)逐漸成為各個(gè)芯片廠商的首選。在這樣的背景下,IP復(fù)用技術(shù)成為了集成電路設(shè)計(jì)的一個(gè)重要分支,很多設(shè)計(jì)廠商在購(gòu)買其它公司的IP核的同時(shí),也越來(lái)越重視本公司的IP核設(shè)計(jì)和積累。

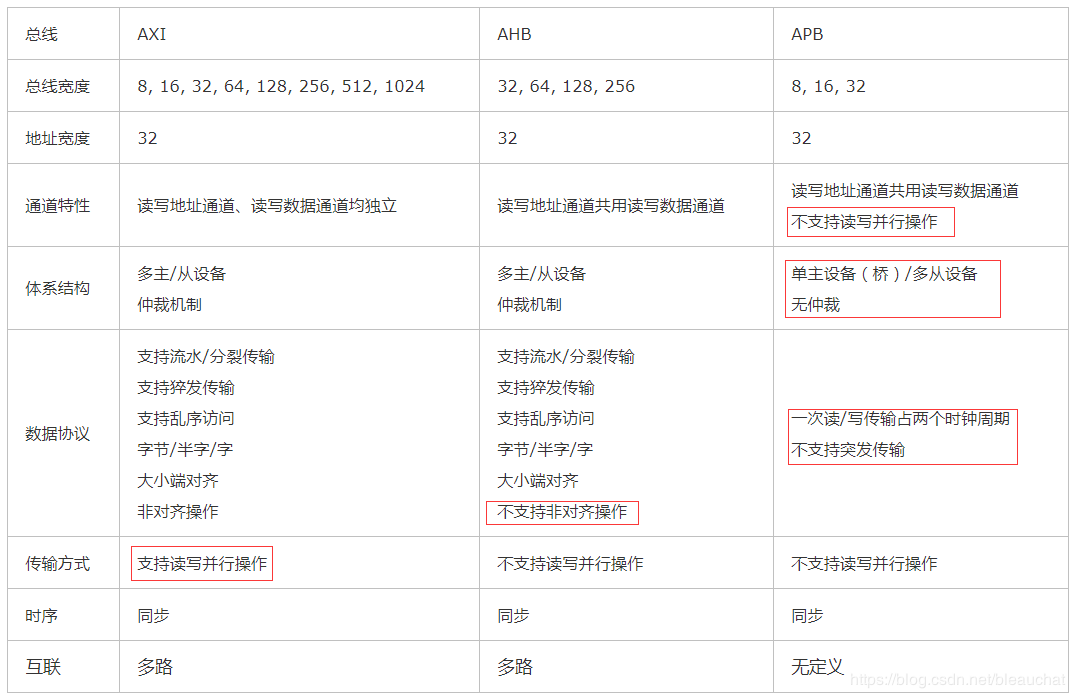

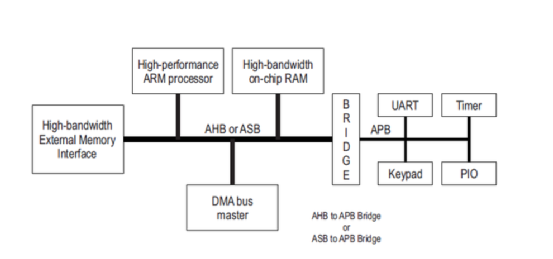

DMA控制器是常見(jiàn)的總線設(shè)備之一,很多廠商都有自己的DMA控制器IP核。比如嵌入式處理器的龍頭ARM公司就有自己的DMA控制器解決方案提供給客戶,另外像Freescale,F(xiàn)ujitsu等芯片制造廠商都有自己的解決方案。本文通過(guò)介紹一種基于ARM總線之一的AHB總線的DMA控制器的IP核設(shè)計(jì),簡(jiǎn)述了IP核設(shè)計(jì)的流程和需要重點(diǎn)注意的地方。

DMA控制器

功能描述

一般而言,DMA控制器的功能與結(jié)構(gòu)是由本單位特定的系統(tǒng)結(jié)構(gòu)決定的。但是作為IP而言,DMA控制器又要有其一般性。DMA是指外部設(shè)備直接對(duì)計(jì)算機(jī)存儲(chǔ)器進(jìn)行讀寫操作的I/O方式。這種方式下數(shù)據(jù)的讀寫無(wú)需CPU執(zhí)行指令,也不經(jīng)過(guò)CPU內(nèi)部寄存器,而是利用系統(tǒng)的數(shù)據(jù)總線,由外設(shè)直接對(duì)存儲(chǔ)器寫入或讀出,從而達(dá)到極高的傳輸速率。現(xiàn)在DMA也可以在內(nèi)存之間或是外設(shè)之間直接進(jìn)行數(shù)據(jù)操作。DMA技術(shù)的重要性在于,利用它進(jìn)行數(shù)據(jù)存取時(shí)不需要CPU進(jìn)行干預(yù),可提高系統(tǒng)執(zhí)行應(yīng)用程序的效率。利用DMA傳送數(shù)據(jù)的另一個(gè)好處是數(shù)據(jù)直接在源地址和目的地址之間傳送,不需要是中間媒介。

通用的DMA控制器應(yīng)具有一下功能:

1.編程設(shè)定DMA的傳輸模式及其所訪問(wèn)內(nèi)存的地址區(qū)域。

2.屏蔽或接受外設(shè)或軟件的DMA請(qǐng)求。當(dāng)有多個(gè)設(shè)備同時(shí)請(qǐng)求時(shí),還要進(jìn)行優(yōu)先級(jí)排隊(duì),首先響應(yīng)最高級(jí)的請(qǐng)求。

3.向CPU或總線仲裁設(shè)備提出總線請(qǐng)求。

4.接收總線響應(yīng)信號(hào),接管總線控制。

5.在DMA控制器的管理下實(shí)現(xiàn)外設(shè)和存儲(chǔ)器、外設(shè)和外設(shè)或存儲(chǔ)器之間的數(shù)據(jù)直接傳輸。

6.在傳輸過(guò)程中進(jìn)行地址修改和傳輸量計(jì)數(shù)。當(dāng)要求的數(shù)據(jù)傳送完后,撤銷總線請(qǐng)求,交還總線控制權(quán)。

總而言之,DMA控制器一方面可以接管總線,直接在I/O接口和存儲(chǔ)器之間進(jìn)行讀寫操作,即可以像CPU一樣視為總線的主設(shè)備,這是DMA與其它外設(shè)最根本的區(qū)別;另一方面,作為一個(gè)I/O器件,其DMA控制功能正式通過(guò)初始化編程來(lái)設(shè)置的。當(dāng)CPU對(duì)其寫入或讀出時(shí),它又和其它的外設(shè)一樣成為總線的從屬器件。

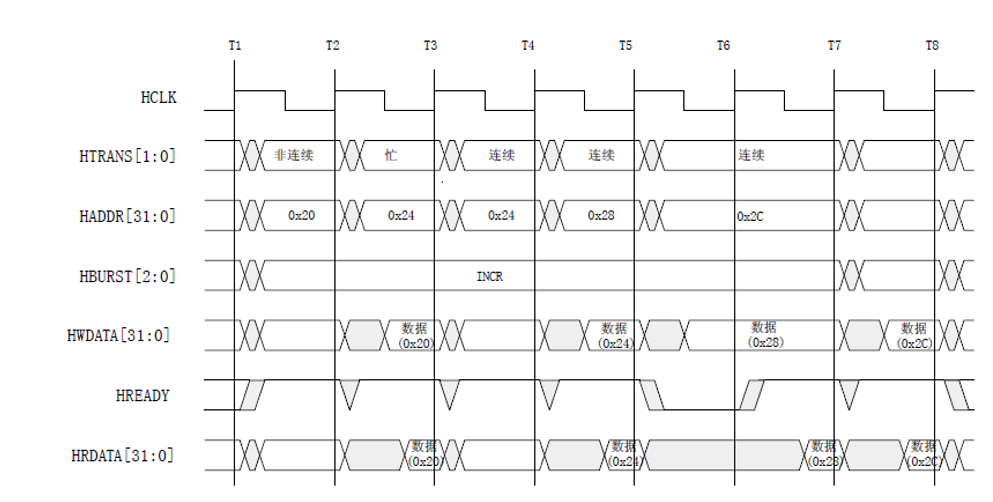

而作為專用的DMA控制器又會(huì)有其特定的功能要求。比如對(duì)于AHB總線而言,需要支持Burst操作。另一方面,現(xiàn)在多數(shù)支持操作系統(tǒng)的嵌入式系統(tǒng)或計(jì)算機(jī)系統(tǒng)都使用虛擬內(nèi)存技術(shù)。這一技術(shù)的使用使得在操作系統(tǒng)層面上看到內(nèi)存地址與物理地址間并非一一映射,操作系統(tǒng)層面上連續(xù)的內(nèi)存地址在真實(shí)的物理內(nèi)存上并不一定連續(xù)。但是DMA控制器并不一定了解這一現(xiàn)象。為了解決這一問(wèn)題并提高傳輸效率,多數(shù)在高級(jí)嵌入式系統(tǒng)中使用的DMA控制器支持分散/集合LLI(LogicLinkItem)技術(shù)。

設(shè)計(jì)指標(biāo)本

DMA控制器的主要指標(biāo)如下:

$16個(gè)DMA通道,其中6個(gè)為獨(dú)立的軟件通道,另10個(gè)為軟硬件復(fù)用的通道。

$DMA讀數(shù)據(jù)與寫數(shù)據(jù)獨(dú)立進(jìn)行。

$各通道獨(dú)立編程,獨(dú)立初始化。

$支持軟件復(fù)位。

$全面支持AHB總線協(xié)議。

$支持LLI技術(shù)。

總體設(shè)計(jì)

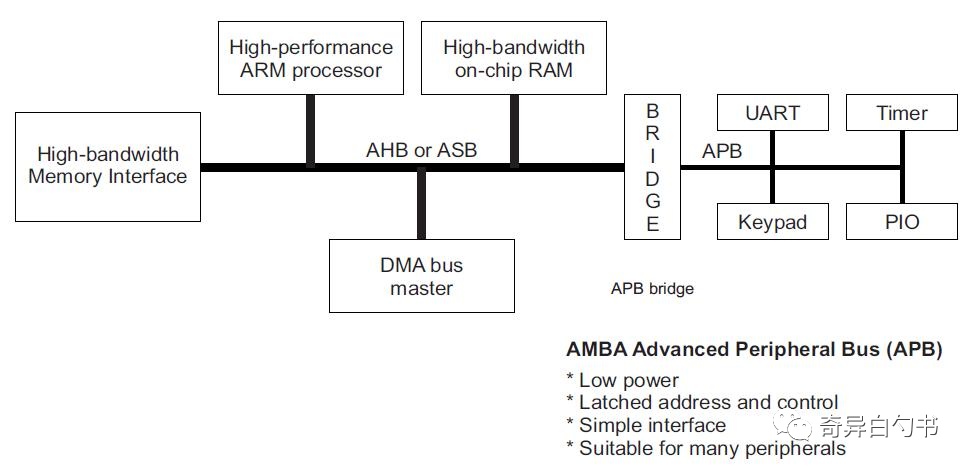

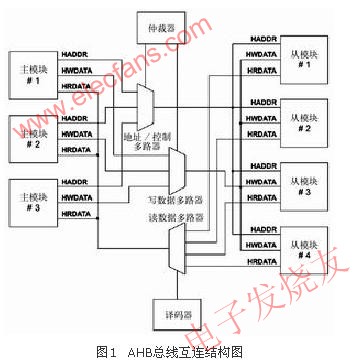

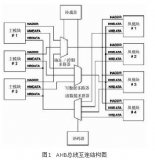

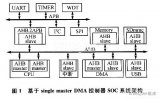

DMA控制器主要包括以下幾個(gè)模塊,其結(jié)構(gòu)圖如圖1所示。

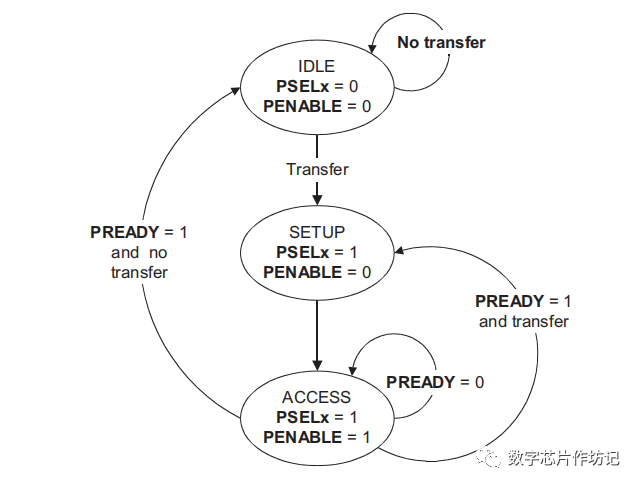

$APB接口模塊:該部分主要實(shí)現(xiàn)APB總線讀寫協(xié)議,并通過(guò)ARM配置DMA控制器的寄存器。

$控制寄存器模塊:該部分通過(guò)APB總線進(jìn)行配置,獲得DMA控制器的控制信息。該模塊主要由命令控制寄存器、狀態(tài)寄存器和中斷寄存器組成。

$DMA控制狀態(tài)機(jī)模塊:本模塊是DMA控制器的核心部分,負(fù)責(zé)發(fā)起和中止每一次DMA傳輸,同時(shí)負(fù)責(zé)每次DMA傳輸過(guò)程中的狀態(tài)轉(zhuǎn)換。

$通道模塊:該模塊包含了16個(gè)通道,其中10個(gè)是軟、硬件復(fù)用的,另外6個(gè)是軟件專用的。前者除了有常規(guī)的寄存器組外,還要負(fù)責(zé)檢測(cè)硬件的DMA傳輸請(qǐng)求;而后者則沒(méi)有這部分功能,但后者要支持LLI功能。常規(guī)的通道寄存器組由各個(gè)通道的源地址、目的地址、傳輸長(zhǎng)度以及通道控制寄存器等組成。

$優(yōu)先級(jí)控制模塊:本模塊有狀態(tài)寄存器和請(qǐng)求寄存器。ARM通過(guò)編程確定各個(gè)通道的優(yōu)先級(jí)順序。當(dāng)有多個(gè)DMA請(qǐng)求同時(shí)出現(xiàn)的時(shí)候,通過(guò)此模塊確定哪個(gè)請(qǐng)求優(yōu)先被響應(yīng)。

$AHB總線接口模塊:本模塊負(fù)責(zé)實(shí)現(xiàn)AHB總線讀寫協(xié)議。

工作原理及流程

作為DMA控制器有其特殊性,主要體現(xiàn)在它既是總線的從設(shè)備,又是總線的主設(shè)備。因此,DMA控制器有兩個(gè)主要的狀態(tài)——空閑態(tài)與工作態(tài)。當(dāng)DMA控制器處于空閑態(tài)時(shí),它就相當(dāng)于一個(gè)總線的從設(shè)備,受到ARM的管理與控制。ARM通過(guò)編程配置DMA控制器的寄存器。

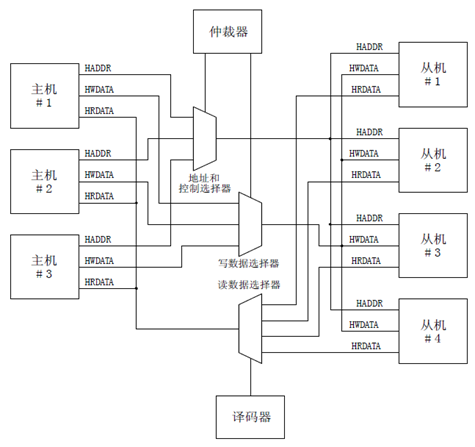

作為嵌入式系統(tǒng)常用的AMBA總線結(jié)構(gòu)和一般的計(jì)算機(jī)系統(tǒng)有一定的區(qū)別。AMBA總線控制權(quán)是由總線仲裁器給予的,DMA控制器與CPU一樣,向總線仲裁器提出總線使用需求,總線仲裁器根據(jù)優(yōu)先級(jí)算法決定是否給予總線使用權(quán)。而一般計(jì)算機(jī)系統(tǒng)默認(rèn)CPU控制總線,若DMA有占用總線的需求是直接向CPU提出申請(qǐng)。

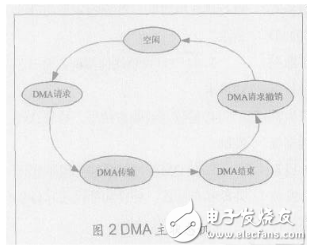

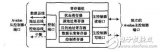

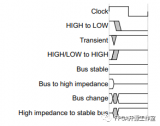

DMA主狀態(tài)機(jī)如圖2所示。當(dāng)有硬件或軟件提出DMA傳輸請(qǐng)求時(shí),DMA控制器將轉(zhuǎn)到工作態(tài)的第一個(gè)子狀態(tài)——準(zhǔn)備狀態(tài),DMA向總線仲裁器發(fā)出總線控制請(qǐng)求。若此時(shí)總線仲裁器沒(méi)有更高優(yōu)先級(jí)的總線需求請(qǐng)求,它會(huì)將總線控制權(quán)交給DMA控制器。當(dāng)DMA控制器拿到總線控制權(quán)后會(huì)轉(zhuǎn)到傳輸狀態(tài)。根據(jù)選定的通道及其寄存器組的要求,進(jìn)行DMA傳輸。在傳輸狀態(tài)中,DMA讀數(shù)據(jù)部分會(huì)率先動(dòng)作,從源地址讀取數(shù)據(jù)至FIFO中,當(dāng)FIFO中的數(shù)據(jù)量夠一次Burst操作后,寫數(shù)據(jù)部分會(huì)行動(dòng),將數(shù)據(jù)從FIFO中寫到目的地址所對(duì)應(yīng)的模塊中。若圖2DMA主狀態(tài)機(jī)FIFO滿,則自動(dòng)停止讀數(shù)據(jù),若FIFO空則自動(dòng)停止寫數(shù)據(jù)。當(dāng)讀數(shù)據(jù)部分完成了此次DMA傳輸要求的長(zhǎng)度后,狀態(tài)機(jī)進(jìn)入下一個(gè)子狀態(tài),等待寫數(shù)據(jù)部分將數(shù)據(jù)全部寫完。當(dāng)完成全部操作后,DMA控制器會(huì)向發(fā)起DMA傳輸請(qǐng)求的設(shè)備發(fā)出信號(hào),告知DMA傳輸順利完成,要求該設(shè)備撤銷DMA傳輸請(qǐng)求,并歸還總線控制權(quán)。至此DMA控制器回到空閑狀態(tài),等待下一次DMA傳輸請(qǐng)求。

一般而言,DMA控制器在總線仲裁器中是優(yōu)先級(jí)最低的設(shè)備。因此,當(dāng)有其它更高優(yōu)先級(jí)的總線主設(shè)備要求總線資源時(shí),DMA控制器會(huì)被剝奪總線使用的權(quán)利,此時(shí)DMA控制器將進(jìn)入等待狀態(tài),直到優(yōu)先級(jí)更高的總線主設(shè)備釋放總線控制權(quán)后再進(jìn)入傳輸狀態(tài)。

當(dāng)軟件提出申請(qǐng),完成內(nèi)存之間的大量DMA傳輸時(shí),一般會(huì)使用LLI功能。LLI功能針對(duì)的虛擬內(nèi)存空間與物理內(nèi)存空間映射的不一致性,為了提高傳輸性能而引入的一種傳輸機(jī)制。作為L(zhǎng)LI傳輸,ARM需要編程給DMA控制器,告知LLI列表的地址,并啟動(dòng)DMA傳輸。當(dāng)DMA控制器發(fā)現(xiàn)是LLI傳輸時(shí),它會(huì)到LLI列表中讀取第一次DMA傳輸?shù)脑吹刂贰⒛康牡刂贰鬏旈L(zhǎng)度以及下一個(gè)LLI列表的地址并存入寄存器。當(dāng)此次DMA傳輸結(jié)束后,DMA控制器會(huì)自動(dòng)到下一個(gè)LLI列表中讀取下一次DMA傳輸?shù)男畔ⅰ_@個(gè)鏈表傳輸過(guò)程直到LLI寄存器中的內(nèi)容為“0”時(shí)中止。

基于ASIC的考慮

關(guān)于總線

根據(jù)AMBA協(xié)議,AHB總線支持字節(jié)、半字和全字操作。因此DMA控制器在這點(diǎn)上符合AHB協(xié)議的要求DMA控制器默認(rèn)32位數(shù)據(jù)線,因此需要根據(jù)讀寫地址以及讀數(shù)據(jù)操作類型將讀入的數(shù)據(jù)放入32位的FIFO中,寫出的時(shí)候再根據(jù)地址和寫數(shù)據(jù)的操作類型將數(shù)據(jù)從FIFO中放到寫數(shù)據(jù)總線上。如字節(jié)操作時(shí),根據(jù)讀地址從讀到的一個(gè)字的數(shù)據(jù)中選取合適的字節(jié)放到FIFO中的最低字節(jié);寫的時(shí)候從FIFO最低部分取數(shù),根據(jù)寫地址將此字節(jié)放到寫數(shù)據(jù)相應(yīng)的部分,其余位補(bǔ)零。

作為ASIC而言,一般情況下,三態(tài)只用于輸入輸出的管腳上。即使是總線在芯片內(nèi)部也是將讀數(shù)據(jù)線與寫數(shù)據(jù)線分開使用的。本設(shè)計(jì)秉承這一原則,將讀寫數(shù)據(jù)線分開。

作為DMA傳輸,地址的變更需要靈。有時(shí)候讀寫地址需要增加,有時(shí)候地址需要不變。當(dāng)增加的時(shí)候,也要根據(jù)傳輸?shù)念愋蜎Q定地址增加1、2或4

關(guān)于復(fù)位

復(fù)位是ASIC設(shè)計(jì)中最容易出問(wèn)題的一環(huán)。DMA控制器主要有兩種復(fù)位方式,一種是上電復(fù)位,即異步復(fù)位,另一種是軟件復(fù)位,即同步復(fù)位。

異步復(fù)位通過(guò)將全部D-觸發(fā)器的Reset端接到復(fù)位信號(hào)線上,無(wú)需時(shí)鐘就可以實(shí)現(xiàn)的復(fù)位。一般情況下在上電的時(shí)候作一次。而根據(jù)功能的需要當(dāng)系統(tǒng)出現(xiàn)故障,或軟件需要強(qiáng)行中止一次DMA傳輸?shù)臅r(shí)候,則需要軟件通過(guò)配置寄存器實(shí)現(xiàn)復(fù)位功能。此時(shí)就需要同步復(fù)位。

關(guān)于綜合

由于DMA控制器工作在高速總線上,總線時(shí)鐘最高可以達(dá)到200M,故在做前端設(shè)計(jì)的時(shí)候要特別注意。

以優(yōu)先級(jí)判斷為例。優(yōu)先級(jí)判斷本質(zhì)就是16個(gè)數(shù)字比大小。為了使時(shí)間復(fù)雜度最小,不采取經(jīng)典的“冒泡排序”,而是對(duì)半排序法。這樣比較4次就可以得到需要的數(shù)據(jù)。四級(jí)MUX對(duì)于低頻而言不算很困難,但是對(duì)于高頻而言,為了能夠滿足時(shí)序要求,就需要在第二次比較之后插入一組觸發(fā)器。

結(jié)語(yǔ)

本文討論了一種基于AMBA總線的DMA控制器的IP核設(shè)計(jì),結(jié)合這個(gè)實(shí)際的設(shè)計(jì),討論了IP復(fù)用技術(shù)的設(shè)計(jì)方法。這個(gè)設(shè)計(jì)不依賴于具體的FPGA或ASIC型號(hào)或工藝,因此其可移植性被大大增加。另一方面本設(shè)計(jì)綜合出來(lái)的DMA控制器是20K門,比起ARM公司的DMAC控制器的68K門,在面積方面也有很大的優(yōu)勢(shì)。

IP復(fù)用技術(shù)越來(lái)越成為嵌入式系統(tǒng)的發(fā)展趨勢(shì)。這種設(shè)計(jì)方法順應(yīng)了超大規(guī)模集成電路的發(fā)展潮流,必將成為這一領(lǐng)域發(fā)展的方向。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論