1、引言

在計算機系統(tǒng)里,為了加快傳送大批量數(shù)據(jù)的速度,常采用DMA方式,通過集成片上DMA控制器接口部件實現(xiàn),在存儲器和外設(shè)之間開辟直接傳輸數(shù)據(jù)通道,DMA控制器的訪問策略跟控制協(xié)議的好壞,直接影響著整個處理器系統(tǒng)性能的好壞14。文中采用SystemC系統(tǒng)級設(shè)計語言,實現(xiàn)了一個快速的可配置多功能DMA控制器。

SystrmC語言是在1999年推出,并由OSCI負(fù)責(zé)支持。維護和發(fā)展目。它是建立C++基礎(chǔ)上的開放的系統(tǒng)級設(shè)計語言,可同時支持軟件級和硬件級的建模,能夠?qū)崿F(xiàn)軟硬件協(xié)同仿真,還可以將系統(tǒng)逐步細(xì)化至用于綜合的寄存器傳輸級,可以有效地簡化設(shè)計過程,降低設(shè)計所需時間,節(jié)約成本。

2、DMA控制器的基本組成

外圍設(shè)備跟內(nèi)核進行數(shù)據(jù)傳輸或者發(fā)送控制信息是通過不同類型的總線實現(xiàn)的O.為了提高整個系統(tǒng)的效率,在處理器中往往存在著不同級別的總線,分別用于連接不同的設(shè)備。一級內(nèi)部總線往往用來實現(xiàn)內(nèi)核對內(nèi)部存儲器的直接訪問;二級系統(tǒng)外設(shè)總線用于實現(xiàn)高速的外設(shè)跟內(nèi)部存儲器之間的訪問; 三級總線則用來連接較低速的外設(shè),并通過橋接器連接到二級總線上。DMA控制器也相當(dāng)于一個外設(shè),跟中斷控制器定時器。外部存儲器接口、主機接口。片內(nèi)有儲器接口一起連接在二級外設(shè)總線上。

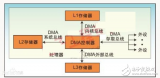

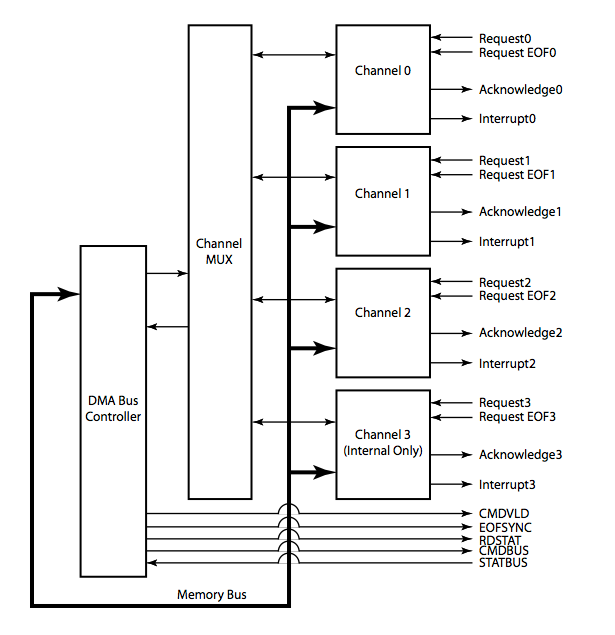

DMA控制器主要由以下幾部分組成: 寄存器狀態(tài)寄存器、控制寄存器、地址寄存器。計數(shù)寄存器和屏蔽寄存器) 。數(shù)據(jù)緩沖器用于接收從源設(shè)備發(fā)送來的數(shù)據(jù),等待轉(zhuǎn)發(fā)給目的設(shè)備) 。地址計數(shù)器運算單元、優(yōu)先級仲裁邏輯。中斷控制邏輯。外設(shè)總線DMA控制器的具體結(jié)構(gòu)如圖1所示(圖中畫出的是僅四通道DMA控制器,更多通道的DMA控制器架構(gòu)與此類似)。

3、DMA方式的工作流程e#

3、DMA方式的工作流程

DMA工作方式下的流程見圖2具體可以劃分為如下4個:主要部 分。

1) DMA傳送開始前的準(zhǔn)備工作

內(nèi)核開始進行DMA傳送之前,首先執(zhí)行一系列的IO指令用來檢測外設(shè)的狀態(tài),初始化寄存器。根據(jù)設(shè)備傳輸速度的不同。在控制寄存器中設(shè)置是否需要等待外設(shè)請求信號進行同步。

在設(shè)計中,采用兩種請求方式來開啟DMA傳送:軟件DMA請求和硬件DMA請求。軟件DMA請求一般用來進行速度較快的設(shè)備之間的數(shù)據(jù)傳送,假定設(shè)備一直處于準(zhǔn)備好狀態(tài)可以隨時進行數(shù)據(jù)的傳輸,比如存儲器;硬件DMA請求則需要等待外設(shè)的請求信號到來時才能進行DMA傳輸,一般用于速度較慢的設(shè)備之間的數(shù)據(jù)傳輸。在這種方式下,DMA響應(yīng)設(shè)備的請求之后,還會發(fā)送響應(yīng)信號給等待的外設(shè)。通過在控制寄存器里面設(shè)置一個信息位,預(yù)先設(shè)置好當(dāng)前通道的傳輸是否需要硬件請求信號,即可實現(xiàn)這兩種方式的傳輸。寄存器還設(shè)置地址改變的方式。數(shù)據(jù)傳送的大小等等信息,初始化完畢后,內(nèi)核維續(xù)執(zhí)行其他操作,等待外設(shè)數(shù)據(jù)準(zhǔn)備好或者等待DMA控制發(fā)送總線請求信號。

2) 獲取總線使用權(quán)

DMA跟CPU共用一套總線,并且二者都可以作為總線的主控設(shè)備,因此,在進行訪問的時候,需要考慮到總線使用權(quán)的問題,獲得總線使用權(quán)的設(shè)備占用總線進行傳輸,其余設(shè)備等待。DMA通道使能信號有效或者外圍設(shè)備發(fā)送DMA請求信號的時候,DMA發(fā)送總線請求信號給內(nèi)核。要求獲得總線的使用權(quán)。

內(nèi)核響應(yīng)總線請求信號以后,如果存在多個模需要先進行優(yōu)先級模塊同時請求DMA訪問的時候,判斷。通道之間的優(yōu)先級可通過寄存器編程,具有最高優(yōu)先級的通道獲得總線的使用權(quán),發(fā)送響應(yīng)信號給對應(yīng)外設(shè),并發(fā)送總線忙信號告知其他模塊總線正在被占用。這時,CPU的操作仍可繼續(xù)進行,遇到需要使用該總線就進入等待。

3)驅(qū)動地址、數(shù)據(jù)總線進行DMA傳送

獲得總線使用權(quán)的通道通過地址寄存器驅(qū)動地址總線,選擇源設(shè)備與目的設(shè)備,并發(fā)送讀寫控制信號,同時通過數(shù)據(jù)總線發(fā)送或者接收數(shù)據(jù)。

DMA的數(shù)據(jù)傳輸方式有兩種:存儲轉(zhuǎn)發(fā)方式和直接數(shù)據(jù)傳輸方式。對于慢速的設(shè)備,采用存儲轉(zhuǎn)發(fā)的模式,即先將數(shù)據(jù)接收到控制器中的數(shù)據(jù)緩沖器,然后再將數(shù)據(jù)發(fā)送到目的設(shè)備;對于高速的外圍設(shè)備,當(dāng)源地址跟目的地址指向的不是同一設(shè)備時,可以采取直接數(shù)據(jù)傳輸?shù)哪J剑瑪?shù)據(jù)直接從源設(shè)備讀出并寫往目的設(shè)備,這樣可以有效地節(jié)省時間,最佳的使用方案是將這兩種方式有效結(jié)合起來進行傳輸。

每傳輸完一次數(shù)據(jù),源地址。目的地址相應(yīng)改變。計數(shù)器遞減,如果數(shù)據(jù)沒有傳輸完,維續(xù)進行傳送,否則,轉(zhuǎn)入下一步操作。DMA傳送完畢后的處理工作

4)通道上的數(shù)據(jù)傳輸完畢后,DMA控制器釋放總線,總線請求信號。總線忙信號無效,并采用專門的機制向內(nèi)核提出中斷,以便內(nèi)核處理器重新獲得總線的使用權(quán)并執(zhí)行相應(yīng)的操作。

但是,中斷提出并被響應(yīng)以后,處理器就要轉(zhuǎn)向執(zhí)行中斷服務(wù)子程序,需要占用處理器的執(zhí)行時間。一種有效的方法是對每個通道設(shè)置中斷屏蔽寄存位,數(shù)據(jù)傳輸完畢的時候,在不要處理器響應(yīng)時禁止通道提出中斷請求。每一個通道都有對應(yīng)的狀態(tài)寄存器,用來表示當(dāng)前數(shù)據(jù)是否傳輸完畢。只有通道的數(shù)據(jù)傳輸完畢,并且該通道對應(yīng)的屏蔽位無效的時候,該通道的中斷請求信號才有效,,各個通道中斷請求信號相或,如果結(jié)果有效,就向內(nèi)核發(fā)送中斷請求,否則DMA傳輸繼續(xù)進行。

4、DMA控制器設(shè)計實現(xiàn)

基于前面對DMA控制器工作流程的詳細(xì)分析。運用SystemC 語言,建立DMA控制器的Cye le-Accurat級參考模型。控制器由以下幾個模塊組成:寄存器賦值、狀態(tài)轉(zhuǎn)換。輸出模塊和頂層模塊。具體工作過程可以參考如圖3所示的有限狀態(tài)機。

5 結(jié)束語

設(shè)計完畢,采用Mode1Sim61進行系統(tǒng)功能仿真驗證。片內(nèi)存儲器采用工具生成的SRAM模塊,輸入激勵中需要的地址。數(shù)據(jù)均采用隨機生成的方式進行,對各個通道的寄存器進行隨機的初始化賦值后,發(fā)送DMA傳送請求信號,分析讀寫的數(shù)據(jù)是否正確,進行驗證。結(jié)果表明,文中設(shè)計的DMA控制器功能正確并且具有較好的性能。

電子發(fā)燒友App

電子發(fā)燒友App

評論