74LS164串轉(zhuǎn)并實(shí)驗(yàn)

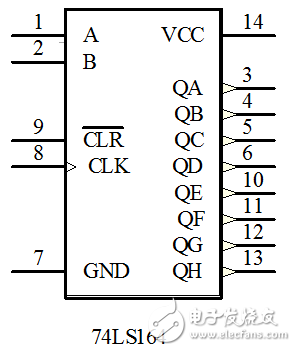

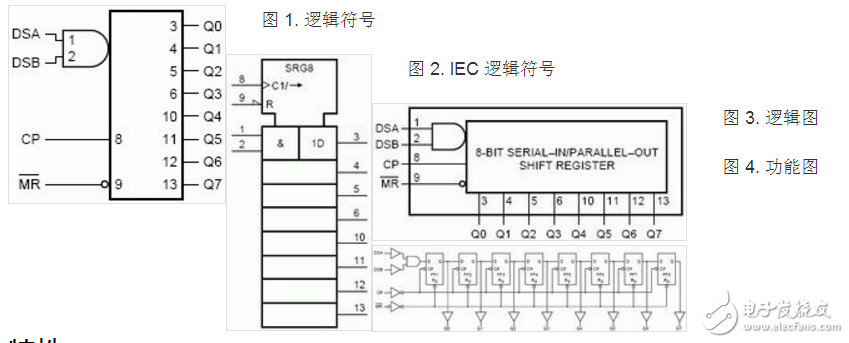

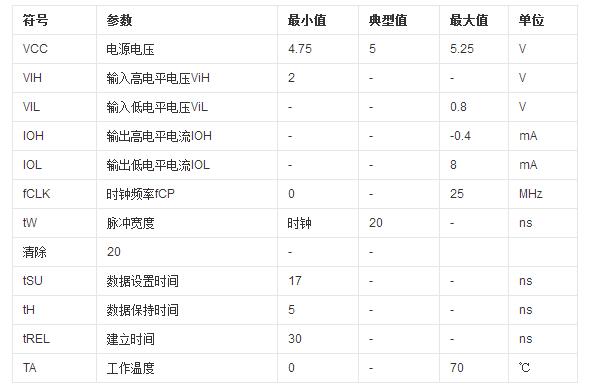

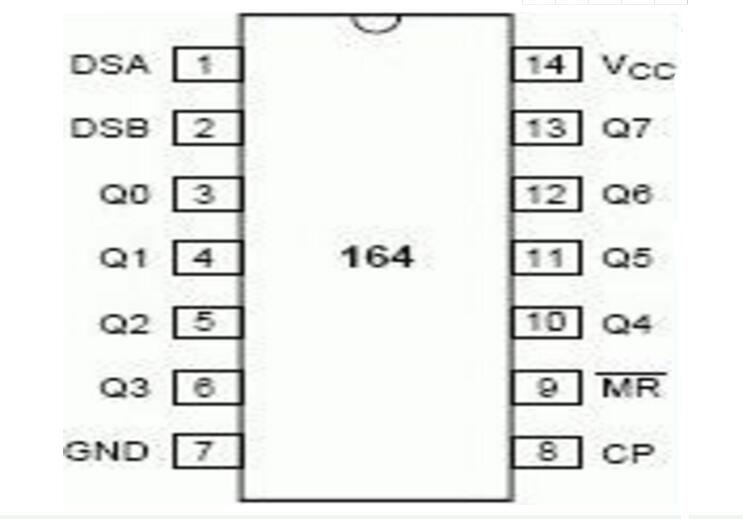

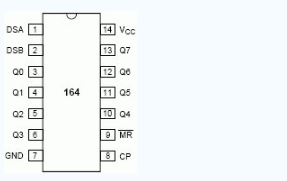

本實(shí)驗(yàn)是用74LS164把輸入的串行數(shù)轉(zhuǎn)換成并行數(shù)輸出,74LS164為串行輸入并行輸出移位寄存器,其引腳圖及功能如下:

A、B:串行輸入端;

QA~QH:并行輸出端;

CLR:清零端,低電平有效;

CLK:時(shí)鐘脈沖輸入端,上升沿有效。

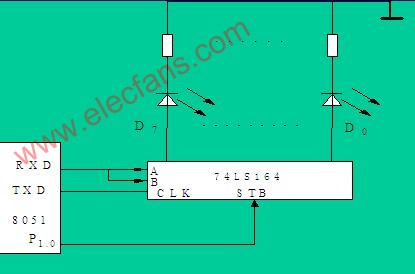

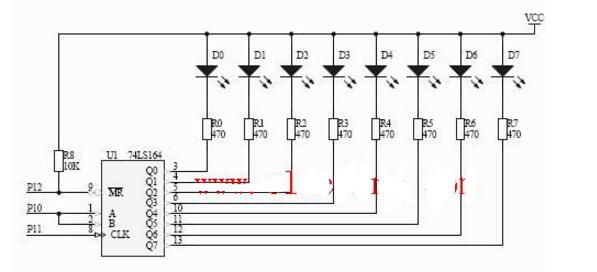

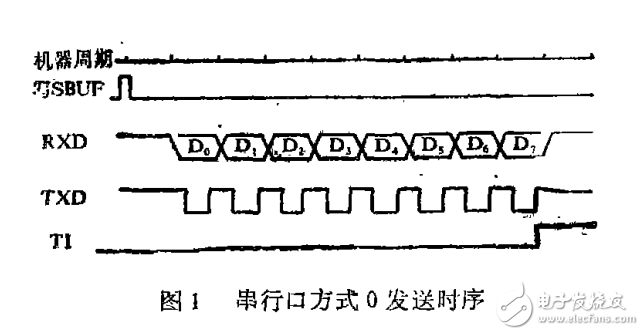

實(shí)驗(yàn)采用單片機(jī)串行工作方式0和P1端口兩種方式串行輸出數(shù)據(jù)。串行口工作方式0時(shí),數(shù)據(jù)為8位,從RXD端輸出,TXD端輸出移位信號(hào),其波特率固定為Fosc/12。在CPU將數(shù)據(jù)寫(xiě)入SBUF寄存器后,立即啟動(dòng)發(fā)送。待8位數(shù)據(jù)輸完后,硬件將狀態(tài)寄存器的TI位置1,TI必須由軟件清零。

串行口工作方式0數(shù)據(jù)/時(shí)鐘是自動(dòng)移位輸出,用P1端口輸出數(shù)據(jù)時(shí),要編程位移數(shù)據(jù),每輸出一個(gè)數(shù)據(jù)位,再輸出一個(gè)移位脈沖。

內(nèi)容及步驟:

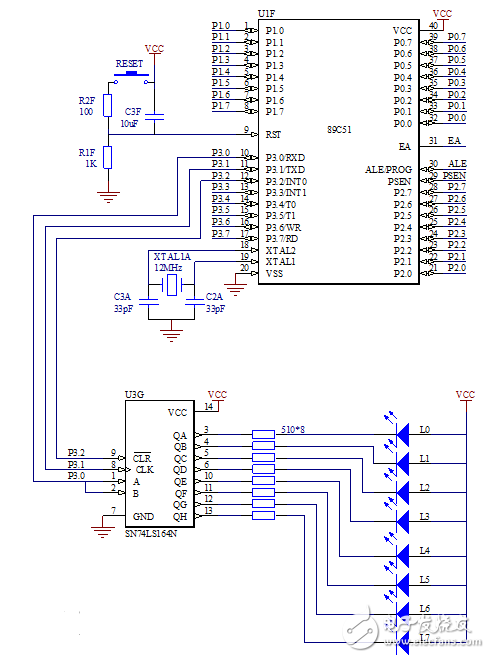

本實(shí)驗(yàn)需要用到單片機(jī)最小系統(tǒng)(F1區(qū))、十六位邏輯電平顯示(I4區(qū))和74LS164(G3區(qū))。

1、選用89C51單片機(jī)最小應(yīng)用系統(tǒng)模塊,用八位數(shù)據(jù)線連接74LS164的并行輸出JD5G與十六位邏輯電平顯示模塊JD2I,將74LS164的串行輸入端A/B(1和2腳)接到RXD上,CLK接到TXD上,CLR接INT0。

2、用串行數(shù)據(jù)通信線連接計(jì)算機(jī)與仿真器,把仿真器插到模塊的鎖緊插座中,請(qǐng)注意仿真器的方向:缺口朝上。

3、打開(kāi)KeiluVision2仿真軟件,首先建立本實(shí)驗(yàn)的項(xiàng)目文件,接著添加“TH23_74164.ASM”源程序,進(jìn)行編譯,直到編譯無(wú)誤。

4、全速運(yùn)行程序,觀察發(fā)光二極管亮滅情況,先右移動(dòng)兩次,再左移動(dòng)兩次,然后閃爍兩次。

5、也可以把源程序編譯成可執(zhí)行文件,用ISP燒錄器燒錄到89S52/89S51芯片中。

74LS164串進(jìn)并出實(shí)驗(yàn)及165并串轉(zhuǎn)換實(shí)驗(yàn)

實(shí)驗(yàn)內(nèi)容

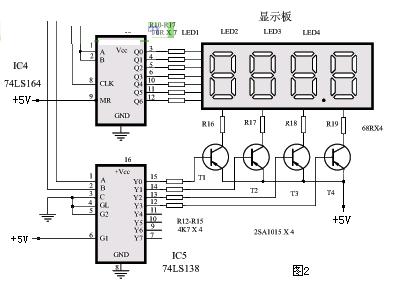

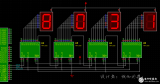

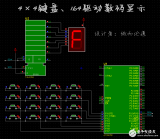

1、用74LS164芯片擴(kuò)展并行輸出口,本實(shí)驗(yàn)中我們用74LS164擴(kuò)展兩個(gè)8位輸出口的接口顯示電路,兩位數(shù)碼管循環(huán)顯示00~99之間的數(shù)字。

2、利用實(shí)驗(yàn)系統(tǒng)上的74LS165芯片,編程實(shí)現(xiàn)8位數(shù)據(jù)并行輸入,串行口串行接收,并將接收的數(shù)據(jù)存放在CPU內(nèi)部存儲(chǔ)區(qū)50H~59H中,共10個(gè)數(shù)據(jù)。(并行輸入數(shù)據(jù)由P1口來(lái)送入)

編程指南

1、74LS164串進(jìn)并出實(shí)驗(yàn)。

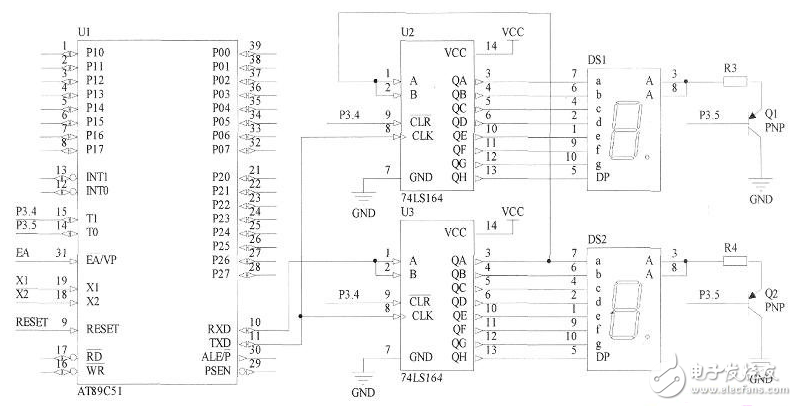

(1)本實(shí)驗(yàn)中MCS-51單片機(jī)串行口工作在方式0(移位寄存器方式,用于并行I/0口擴(kuò)展)的發(fā)送狀態(tài)時(shí),串行數(shù)據(jù)由P3.0(RXD)送出,移位時(shí)鐘由P3.1(TXD)送出。在移位時(shí)鐘的作用下,串行口發(fā)送緩沖器的數(shù)據(jù)一位一位地移入74LS164中。需要指出的是,由于741S164無(wú)并行輸出控制端,因而在串行輸入過(guò)程中,其輸出端的狀態(tài)會(huì)不斷變化,故在某些應(yīng)用場(chǎng)合,在74LS164的輸出端應(yīng)加接輸出三態(tài)門(mén)控制,以便保證串行輸入結(jié)束后再輸出數(shù)據(jù)。

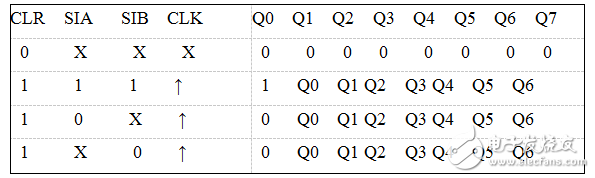

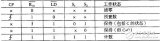

(2)74LS164引腳功能表

2、165并串轉(zhuǎn)換實(shí)驗(yàn)。

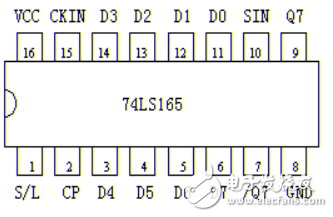

(1)74LS165芯片引腳圖

管腳說(shuō)明:

D0throughD7--Parallelinputs

SI--Serialinput

Q7,/Q7--Dataoutputs

CLK--Clock

CKIN--Clockinhibit

S/L--(高有效)Shift/Parallel-loadcontrol(低有效)

(2)編程說(shuō)明

74LS165是8位并行置入移位寄存器。當(dāng)移位/置入端(S/L)由高到低跳變時(shí),并行輸入端的數(shù)據(jù)被置入寄存器;當(dāng)S/L=1,且時(shí)鐘禁止端(第15腳)為低電平時(shí),允許時(shí)鐘輸入,這時(shí)在時(shí)鐘脈沖的作用下,數(shù)據(jù)由D0到D7方向移位。如下的電路原理圖中,TXD(P3.1)作為移位脈沖輸出端與所有74LS165的移位脈沖輸入端CP相連;RXD(P3.0)作為串行輸入端與74LS165的串行輸出端Q7相連;P3.2用來(lái)控制74LS165的移位與置入而同S/L相連;74LS165的時(shí)鐘禁止端(15腳)接地,表示允許時(shí)鐘輸入。當(dāng)擴(kuò)展多個(gè)8位并行輸入口時(shí),兩芯片的首尾(Q7與Sin)相連。

實(shí)驗(yàn)接線圖

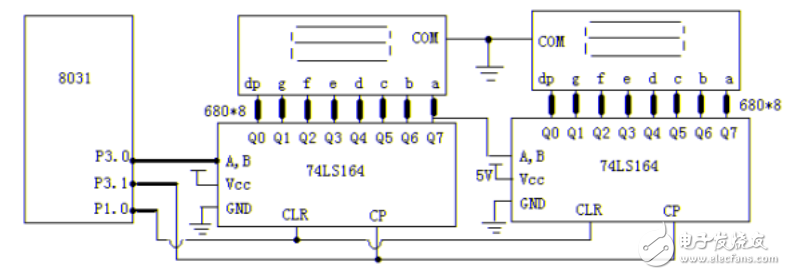

1、74LS164串進(jìn)并出實(shí)驗(yàn)

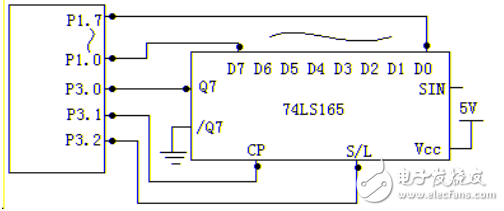

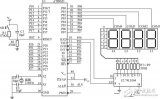

2、165并串轉(zhuǎn)換實(shí)驗(yàn)

實(shí)驗(yàn)步驟

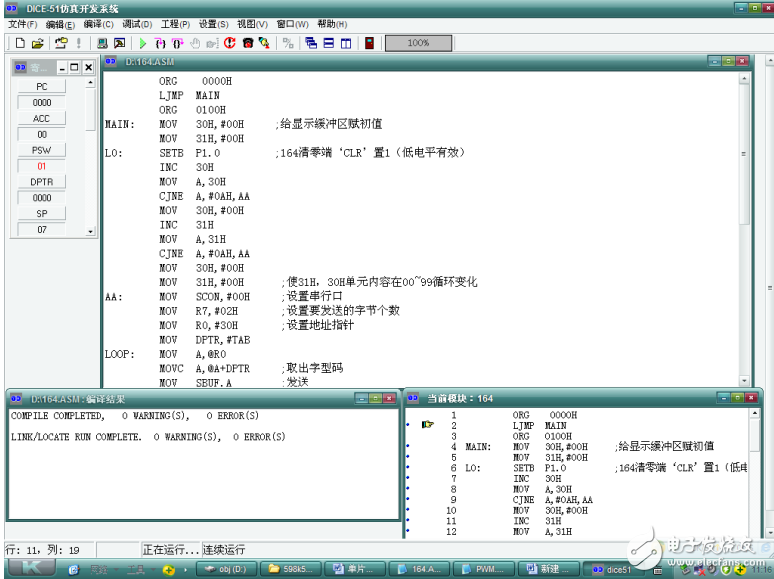

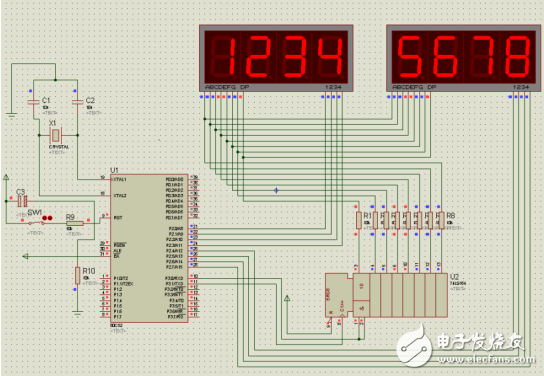

1、在74LS164串進(jìn)并出實(shí)驗(yàn)中,用雙頭線連接,P3.0接插孔A/B,P3.1接插孔CP,P1.0接插孔/CLR,調(diào)入程序運(yùn)行,兩位數(shù)碼管上循環(huán)顯示數(shù)字00~99。下面是74LS164串進(jìn)并出程序運(yùn)行仿真的情況:

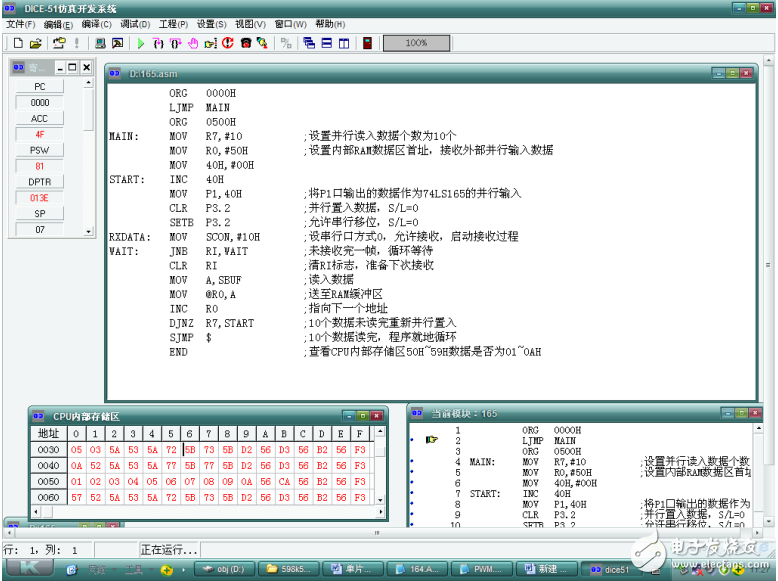

2、在165并串轉(zhuǎn)換實(shí)驗(yàn)中,P1.0~P1.7接D7~D0,P3 .0接Q7,P3.1接CP,P3.2接S/L。調(diào)入程序165.ASM,編譯、裝載、運(yùn)行。檢查CPU內(nèi)部存儲(chǔ)器50H~59H中的數(shù)據(jù)是否為01H~0AH(注意刷新存儲(chǔ)器)。下面是165并串轉(zhuǎn)換程序仿真運(yùn)行的情況:

程序

1、74LS164串進(jìn)并出實(shí)驗(yàn)程序

ORG 0000H

LJMP MAIN

ORG 0100H

MAIN: MOV 30H,#00H ;給顯示緩沖區(qū)賦初值

MOV 31H,#00H

L0: SETB P1.0 ;164清零端‘CLR’置1(低電平有效)

INC 30H

MOV A,30H

CJNE A,#0AH,AA

MOV 30H,#00H

INC 31H

MOV A,31H

CJNE A,#0AH,AA

MOV 30H,#00H

MOV 31H,#00H ;使31H,30H單元內(nèi)容在00~99循環(huán)變化

AA: MOV SCON,#00H ;設(shè)置串行口

MOV R7,#02H ;設(shè)置要發(fā)送的字節(jié)個(gè)數(shù)

MOV R0,#30H ;設(shè)置地址指針

MOV DPTR,#TAB

LOOP: MOV A,@R0

MOVC A,@A+DPTR ;取出字型碼

MOV SBUF,A ;發(fā)送

WAIT: JNB TI,WAIT ;等待一幀發(fā)關(guān)完畢

CLR TI

INC R0 ;指向下一個(gè)字形碼

DJNZ R7,LOOP

MOV R2,#30H ;調(diào)用延時(shí)子程序

LCALL DELYA

CLR P1.0 ;164清零端‘CLR’置0(低電平有效)

SJMP L0

TAB: DB 3FH,06H,5BH,04FH,66H,6DH,7DH,07H,7FH,6FH ;七段LED段選碼(共陰極)

DB 77H,7CH,39H,5EH,86H,8EH,0FFH,0F1H,0C6H,092H,0BFH

DELYA: PUSH 02H ;延時(shí)子程序

DELYB: PUSH 02H

DELYC: PUSH 02H

DELYD: DJNZ R2,DELYD

POP 02H

DJNZ R2,DELYC

POP 02H

DJNZ R2,DELYB

POP 02H

DJNZ R2,DELYA

RET

END

2、165并串轉(zhuǎn)換實(shí)驗(yàn)程序

ORG 0000H

LJMP MAIN

ORG 0500H

MAIN: MOV R7,#10 ;設(shè)置并行讀入數(shù)據(jù)個(gè)數(shù)為10個(gè)

MOV R0,#50H ;設(shè)置內(nèi)部RAM數(shù)據(jù)區(qū)首址,接收外部并行輸入數(shù)據(jù)

MOV 40H,#00H

START: INC 40H

MOV P1,40H ;將P1口輸出的數(shù)據(jù)作為74LS165的并行輸入

CLR P3.2 ;并行置入數(shù)據(jù),S/L=0

SETB P3.2 ;允許串行移位,S/L=0

RXDATA: MOV SCON,#10H ;設(shè)串行口方式0,允許接收,啟動(dòng)接收過(guò)程

WAIT: JNB RI,WAIT ;未接收完一幀,循環(huán)等待

CLR RI ;清RI標(biāo)志,準(zhǔn)備下次接收

MOV A,SBUF ;讀入數(shù)據(jù)

MOV @R0,A ;送至RAM緩沖區(qū)

INC R0 ;指向下一個(gè)地址

DJNZ R7,START ;10個(gè)數(shù)據(jù)未讀完重新并行置入

SJMP $ ;10個(gè)數(shù)據(jù)讀完,程序就地循環(huán)

END ;查看CPU內(nèi)部存儲(chǔ)區(qū)50H~59H數(shù)據(jù)是否為01~0AH

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論