PC機發送字符給單片機控制發光管亮,同時將其傳回PC機,其中單片機的發送和接收都采用查詢方式

1、USART的主要特點

通用同步和異步串行接收器和轉發器(USART) 是一個高度靈活的串行通訊設備。主要特點為:

全雙工操作( 獨立的串行接收和發送寄存器)

異步或同步操作

主機或從機提供時鐘的同步操作

高精度的波特率發生器

支持5, 6, 7, 8, 或9 個數據位和1 個或2 個停止位

支持的奇偶校驗操作

數據過速檢測? 幀錯誤檢測

噪聲濾波,包括錯誤的起始位檢測,以及數字低通濾波器?三個獨立的中斷:發送結束中斷, 發送數據寄存器空中斷,以及接收結束中斷

多處理器通訊模式

倍速異步通訊模式

2、異步串行收發器

USART 分為了三個主要部分: 時鐘發生器,發送器和接收器。控制寄存器由三個單元共享。時鐘發生器包含同步邏輯,通過它將波特率發生器及為從機同步操作所使用的外部輸入時鐘同步起來。XCK ( 發送器時鐘) 引腳只用于同步傳輸模式。發送器包括一個寫緩沖器,串行移位寄存器,奇偶發生器以及處理不同的幀格式所需的控制邏輯。寫緩沖器可以保持連續發送數據而不會在數據幀之間引入延遲。由于接收器具有時鐘和數據恢復單元,它是USART 模塊中最復雜的。恢復單元用于異步數據的接收。除了恢復單元,接收器還包括奇偶校驗,控制邏輯,移位寄存器和一個兩級接收緩沖器UDR。接收器支持與發送器相同的幀格式,而且可以檢測幀錯誤,數據過速和奇偶校驗錯誤。

3、時鐘產生

1)USART支持4種模式的時鐘

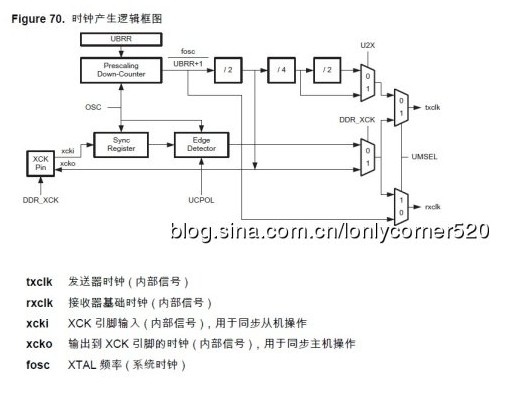

時鐘產生邏輯為發送器和接收器產生基礎時鐘。USART 支持4 種模式的時鐘:正常的異步模式,倍速的異步模式,主機同步模式,以及從機同步模式。USART 控制位UMSEL和狀態寄存器C (UCSRC) 用于選擇異步模式和同步模式。倍速模式( 只適用于異步模式) 受控于UCSRA 寄存器的U2X。使用同步模式 (UMSEL = 1) 時,XCK 的數據方向寄存器(DDR_XCK)決定時鐘源是由內部產生(主機模式)還是由外部生產(從機模式)。僅在同步模式下XCK 有效。

2)內部時鐘用于異步模式和同步主機模式

USART 的波特率寄存器UBRR 和降序計數器相連接,一起構成可編程的預分頻器或波特率發生器。降序計數器對系統時鐘計數,當其計數到零或UBRRL 寄存器被寫時,會自動裝入UBRR 寄存器的值。當計數到零時產生一個時鐘,該時鐘作為波特率發生器的輸出時鐘,輸出時鐘的頻率為fosc/(UBRR+1)。發生器對波特率發生器的輸出時鐘進行2、8或16 的分頻,具體情況取決于工作模式。波特率發生器的輸出被直接用于接收器與數據恢復單元。數據恢復單元使用了一個有2、8或16個狀態的狀態機,具體狀態數由UMSEL、U2X 與 DDR_XCK 位設定的工作模式決定。Table 60 給出了計算波特率(位/秒)以及計算每一種使用內部時鐘源工作模式的UBRR值的公式。

3)倍速工作模式

通過設定UCSRA 寄存器的U2X 可以使傳輸速率加倍。該位只對異步工作模式有效。當工作在同步模式時,設置該位為“0”。設置該位把波特率分頻器的分頻值從16 降到8,使異步通信的傳輸速率加倍。此時接收器只使用一半的采樣數對數據進行采樣及時鐘恢復,因此在該模式下需要更精確的系統時鐘與更精確的波特率設置。發送器則沒有這個要求。

4)外部時鐘(這些東西感覺都是扯淡的~~呵呵)

同步從機操作模式由外部時鐘驅動,如Figure 70 所示。

輸入到XCK 引腳的外部時鐘由同步寄存器進行采樣,用以提高穩定性。同步寄存器的輸出通過一個邊沿檢測器,然后應用于發送器與接收器。這一過程引入了兩個CPU 時鐘周期的延時,因此外部XCK 的最大時鐘頻率由以下公式限制:fsck要注意fosc 由系統時鐘的穩定性決定,為了防止因頻率漂移而丟失數據,建議保留足夠的裕量。

5)同步時鐘操作

使用同步模式時(UMSEL = 1)XCK 引腳被用于時鐘輸入( 從機模式) 或時鐘輸出( 主機模式)。時鐘的邊沿、數據的采樣與數據的變化之間的關系的基本規律是:在改變數據輸出端TxD 的XCK 時鐘的相反邊沿對數據輸入端RxD 進行采樣。

4、幀格式

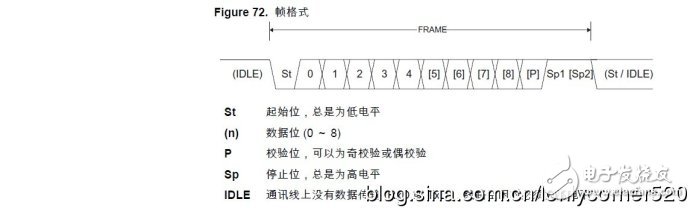

串行數據幀由數據字加上同步位( 開始位與停止位) 以及用于糾錯的奇偶校驗位構成。

1)數據幀格式

? 1 個起始位

? 5、 6、 7、 8 或9 個數據位

? 無校驗位、奇校驗或偶校驗位

? 1或2 個停止位

數據幀以起始位開始;緊接著是數據字的最低位,數據字最多可以有9 個數據位,以數據的最高位結束。如果使能了校驗位,校驗位將緊接著數據位,最后是結束位。當一個完整的數據幀傳輸后,可以立即傳輸下一個新的數據幀,或使傳輸線處于空閑狀態。Figure72 所示為可能的數據幀結構組合。括號中的位是可選的。

數據幀的結構由UCSRB 和 UCSRC 寄存器中的UCSZ2:0、 UPM1:0、USBS 設定。接收與發送使用相同的設置。設置的任何改變都可能破壞正在進行的數據傳送與接收。USART的字長位UCSZ2:0確定了數據幀的數據位數;校驗模式位UPM1:0用于使能與決定校驗的類型; USBS 位設置幀有一位或兩位結束位。接收器忽略第二個停止位,因此幀錯誤(FE) 只在第一個結束位為”0” 時被檢測到。

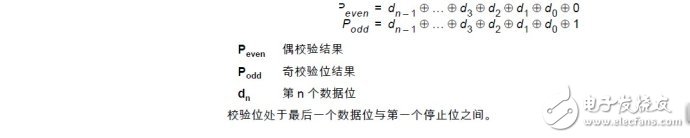

2)校驗位的計算

校驗位的計算是對數據的各個位進行異或運算。如果選擇了奇校驗,則異或結果還需要取反。校驗位與數據位的關系如下:

注意:校驗位位于最后一個數據位與第一個停止位之間。

5、USART的寄存器及設置

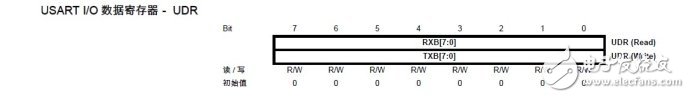

1)USART I/O數據寄存器

USART 發送數據緩沖寄存器和USART 接收數據緩沖寄存器共享相同的I/O 地址,稱為USART 數據寄存器或UDR。將數據寫入UDR 時實際操作的是發送數據緩沖器存器(TXB),讀UDR 時實際返回的是接收數據緩沖寄存器(RXB) 的內容。在5、6、7 比特字長模式下,未使用的高位被發送器忽略,而接收器則將它們設置為0。只有當UCSRA寄存器的UDRE標志置位后才可以對發送緩沖器進行寫操作。如果UDRE沒有置位,那么寫入UDR 的數據會被USART 發送器忽略。當數據寫入發送緩沖器后,若移位寄存器為空,發送器將把數據加載到發送移位寄存器。然后數據串行地從TxD 引腳輸出。接收緩沖器包括一個兩級FIFO,一旦接收緩沖器被尋址FIFO 就會改變它的狀態。因此不要對這一存儲單元使用讀- 修改- 寫指令(SBI 和CBI)。使用位查詢指令(SBIC 和SBIS)時也要小心,因為這也有可能改變FIFO 的狀態

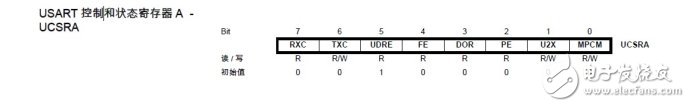

2)USART控制和狀態寄存器A

? Bit 7 – RXC: USART 接收結束

接收緩沖器中有未讀出的數據時RXC 置位,否則清零。接收器禁止時,接收緩沖器被刷新,導致RXC 清零。RXC 標志可用來產生接收結束中斷( 見對RXCIE 位的描述)。? Bit 6 – TXC: USART 發送結束發送移位緩沖器中的數據被送出,且當發送緩沖器 (UDR) 為空時TXC 置位。執行發送結束中斷時TXC 標志自動清零,也可以通過寫1 進行清除操作。TXC 標志可用來產生發送結束中斷( 見對TXCIE 位的描述)。? Bit 5 – UDRE: USART 數據寄存器空UDRE標志指出發送緩沖器(UDR)是否準備好接收新數據。UDRE為1說明緩沖器為空,已準備好進行數據接收。UDRE標志可用來產生數據寄存器空中斷(見對UDRIE位的描述)。復位后UDRE 置位,表明發送器已經就緒。? Bit 4 – FE: 幀錯誤如果接收緩沖器接收到的下一個字符有幀錯誤,即接收緩沖器中的下一個字符的第一個停止位為0,那么FE 置位。這一位一直有效直到接收緩沖器(UDR) 被讀取。當接收到的停止位為1 時, FE 標志為0。對UCSRA 進行寫入時,這一位要寫0。? Bit 3 – DOR: 數據溢出數據溢出時DOR 置位。當接收緩沖器滿( 包含了兩個數據),接收移位寄存器又有數據,若此時檢測到一個新的起始位,數據溢出就產生了。這一位一直有效直到接收緩沖器(UDR) 被讀取。對UCSRA 進行寫入時,這一位要寫0。? Bit 2 – PE: 奇偶校驗錯誤當奇偶校驗使能(UPM1 = 1),且接收緩沖器中所接收到的下一個字符有奇偶校驗錯誤時UPE 置位。這一位一直有效直到接收緩沖器 (UDR) 被讀取。對UCSRA 進行寫入時,這一位要寫0。? Bit 1 – U2X: 倍速發送這一位僅對異步操作有影響。使用同步操作時將此位清零。此位置1 可將波特率分頻因子從16 降到8,從而有效的將異步通信模式的傳輸速率加倍。? Bit 0 – MPCM: 多處理器通信模式設置此位將啟動多處理器通信模式。MPCM 置位后, USART 接收器接收到的那些不包含地址信息的輸入幀都將被忽略。發送器不受MPCM設置的影響。

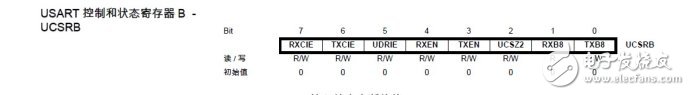

3)USART控制和狀態寄存器B

? Bit 7 – RXCIE: 接收結束中斷使能

置位后使能RXC 中斷。當RXCIE 為1,全局中斷標志位SREG 置位, UCSRA 寄存器的RXC 亦為1 時可以產生USART 接收結束中斷。? Bit 6 – TXCIE: 發送結束中斷使能置位后使能TXC 中斷。當TXCIE 為1,全局中斷標志位SREG 置位,UCSRA 寄存器的TXC 亦為1 時可以產生USART 發送結束中斷。? Bit 5 – UDRIE: USART 數據寄存器空中斷使能置位后使能UDRE 中斷。當UDRIE 為1,全局中斷標志位SREG 置位,UCSRA 寄存器的UDRE 亦為1 時可以產生USART 數據寄存器空中斷。

? Bit 4 – RXEN: 接收使能

置位后將啟動USART 接收器。RxD 引腳的通用端口功能被USART 功能所取代。禁止接收器將刷新接收緩沖器,并使 FE、DOR 及PE 標志無效。

? Bit 3 – TXEN: 發送使能

置位后將啟動將啟動USART 發送器。TxD 引腳的通用端口功能被USART 功能所取代。TXEN 清零后,只有等到所有的數據發送完成后發送器才能夠真正禁止,即發送移位寄存器與發送緩沖寄存器中沒有要傳送的數據。發送器禁止后,TxD引腳恢復其通用I/O功能。

? Bit 2 – UCSZ2: 字符長度

UCSZ2與UCSRC寄存器的UCSZ1:0結合在一起可以設置數據幀所包含的數據位數(字符長度)。

? Bit 1 – RXB8: 接收數據位 8

對9 位串行幀進行操作時,RXB8 是第9 個數據位。讀取UDR 包含的低位數據之前首先要讀取RXB8。

? Bit 0 – TXB8: 發送數據位8

對9 位串行幀進行操作時,TXB8 是第9 個數據位。寫UDR 之前首先要對它進行寫操作。

電子發燒友App

電子發燒友App

評論